CDMA BASED WIRELESS TRANSCEIVER SYSTEM MATLAB

advertisement

CDMA BASED WIRELESS TRANSCEIVER SYSTEM

MATLAB SIMULATION AND FPGA IMPLEMENTATION

Zohaib Mahtab, Suhaib Jalis Ahmed, Syed Sameem Hussain, Sarwar Hasan

Dept. of Computer & Information Systems Engg., N.E.D University of Engg. & Tech. Karachi

{zohaib.online,suhaibj, sameem.hussain, server_hasan}@gmail.com

Abstract

Code Division Multiple Access (CDMA) has become

the technology of choice for the current and future

generation of wireless systems. We have implemented the

CDMA IS-95 based Wireless Transceiver System using

Matlab Simulink v 7.0. The entire system is implemented

using the Xilinx System Generator Block v6.3.

Even though the CDMA IS-95 system is already

implemented in Simulink and is provided as a demo,

there is no way of converting it into real Hardware.

Using Xilinx System Generator we have made our

implementation capable of being translated into any of

the HDL codes. This can be then mapped onto

appropriate FPGA easily. We have used the hardware

co-simulation feature of the Xilinx System generator to

create a library of the basic building blocks of the IS-95

system. This library can be used for implementing to

create the various channels that are the part of the

CDMA system.

Keywords: CDMA, CRC, Convolutional, Interleaver, PN

Sequence, Walsh codes, Viterbi decoder.

1. INTRODUCTION

Code Division Multiple Access (CDMA) has become

the technology of choice for the current and future

generation of wireless systems. IS-95 based CDMA

systems developed by TIA have been widely deployed in

the U.S. and around the world [1]. The IS-95-A design

CCECE 2004- CCGEI 2004, Niagara Falls, May/mai 2004

0-7803-8253-6/04/$17.00 ©2004 IEEE

provides superior multiple-access capabilities, in addition

to a number of other desirable attributes for wireless

cellular service. These attributes include optimum

subscriber station power management, universal

frequency reuse, soft handoff, and enablement of the use

of optimum receiver structures for time-varying

multipath fading channels [1]. We assume that the reader

has some familiarity with CDMA principles and the IS95-A standard, in particular.

Simulink, which runs in MATLAB, is an interactive

tool for modeling, simulating, and analyzing dynamical

systems. The Xilinx System Generator [8], a highperformance design tool, runs as part of Simulink. The

System Generator elements bundled as the Xilinx

Blockset appear in the Simulink library browser. It

provides some basic block for system design. The

Bottom-Up approach for the system development is used,

wherein we have divided the sub-modules of the system

into the basic leaf blocks, so that they can be mapped

with the provided library blocks.

This paper is organized as follows. In section 2

System Architecture is explained. Section 3 deals with

the implementation of the whole architecture. Synthesis

and the results are discussed in Section 4. Finally the

paper is concluded in section 5.

2. SYSTEM ARCHITECTURE

In this section the complete system architecture has

been discussed.

[17 423]

[657, 475]

PCBs

1.2288 Mcps

800 bps

8.6 Kbps

9.6 Kbps

CRC

Generator

19.2 Kbps

Conv.Encoder

R = 1/2

I Pilot PN

Wi

BB Filter

1.2288 Mcps

19.2 Kbps

Block

Interleaver

To QPSK

Modulator

BB Filter

Long Code

Generator

f (ESN)

8.6 Kbps

Decimate

64

1.2288 Mcps

800 bps

19.2 Ksps

Decimate

24

19.2 Kbps

9.6 Kbps

Frame Quality

Detector

Viterbi

Decoder

[17 423]

[657, 475]

Derpeater

Long Code

Generator

1.2288 Mcps

Deinterleaver

Q Pilot PN

1.2288 Mcps

Despreader

Descrambler

Demodulator

Decimate

64

Wi

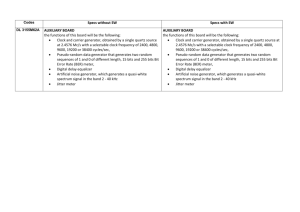

Figure 1: Forward Link Traffic Channel Transmitter and Receiver.

2.1 Channel Description

The base-band sequence is a stream of 0s that are spread

by Walsh function 0, which is also a sequence of all 0s.

The standard IS-95 protocol has two different link

structures for the Forward Channel and the Reverse

Channel. Our developed system is based on the IS-95

Forward Channel architecture.

2.1.2 Sync Channel: The information that is contained in

the sync channel message notifies the mobile of

important information about system synchronization and

parameters. First the base-band information is error

protected and interleaved. It is then spread by Walsh

function 32 and further spread by the PN sequence that is

identified with the serving sector. The base-band

information is at a rate of 1.2 Kbps.

The forward link consists of four types of logical

channels [1], [2], [3], [11]: pilot, synchronizing, paging,

and traffic channels. There is one pilot channel, one sync

channel, up to seven paging channels, and several traffic

channels. Each of these forward-link channels is first

spread orthogonally by its Walsh function, and then it is

spread by a quadrature pair of short PN sequences. At

one time IS-95 supports up to 63 channels, and each one

has a unique Walsh code sequences. All channels are

added together to form the composite SS signal to be

transmitted on the forward link.

2.1.1 Pilot Channel: The pilot channel is transmitted

continuously by the base station sector. The pilot channel

provides the mobile with timing and phase reference. The

mobile’s measurement of the signal-to-noise ratio (i.e.,

Ec /I0) of the pilot channel also gives an indication of

which is the strongest serving sector of that mobile. The

pilot channel is identified by the Walsh function 0 (w0).

The channel itself contains no base-band information.

2.13 Paging Channel: The paging channel also carries

baseband information at higher rates. It can transmit at

either 4.8 or 9.6 Kbps. Although there can be up to seven

paging channels per sector, each mobile only monitors

one paging channel. The baseband information is first

error protected, and then if the data rate is at 4.8 Kbps,

the bits are repeated once. Otherwise, they are not

repeated. Following interleaving, the data is first

scrambled by a decimated long PN sequence, and then it

is spread by a specific Walsh function and by the short

PN sequence assigned to the serving sector. Long PN

code undergoes a decimation ratio of 64:1 (i.e., from

1.2288 Mcps to 19.2 Ksps). The long-code generator

itself is masked with a mask specific to each unique

paging channel number (i.e., 1 through 7). The paging

channel is divided into 80-ms slots. A group of 2,048

slots is called a maximum slot cycle. An 80-ms slot is

divided into four paging channel frames, and each paging

channel frame is further divided into two paging channel

half-frames. The first bit of each half-frame is called the

synchronized capsule indicator (SCI) bit.

2.1.4 Traffic Channel: The forward traffic channel is

used to transmit user data and voice; signaling messages

are also sent over the traffic channel.

Figure 1 shows the forward traffic channel for Rate

Set 1. For this rate set, the vocoder is capable of varying

its output data rate in response to speech activities. Four

different data rates are supported: 9.6, 4.8, 2.4, and 1.2

Kbps. For example, during quiet periods of speech, the

vocoder may elect to code the speech at the lowest rate of

1.2 Kbps. The baseband data from the vocoder is

convolutionally encoded for error protection. For Rate

Set 1, a rate 1/2 convolutional encoder is used. The

encoding effectively doubles the data rate. After

convolutional encoding, the data undergoes symbol

repetition, which repeats the symbols when lower rate

data are produced by the vocoder. After symbol

repetition, the data is interleaved to combat fading then

the interleaved data is scrambled by a decimated long PN

sequence. The long PN sequence is generated by a long

PN code generator. The generator outputs a long PN

sequence at 1.2288 Mcps. Because the data rate at the

interleaver output is 19.2 Ksps, the PN sequence is

decimated by a ratio of 64:1 to also achieve a rate of 19.2

Kcps; the decimated long PN sequence at 19.2 Kcps is

then multiplied with the 19.2-Ksps data stream. Note that

the long-code generator produces the long PN sequence

using a mask that is specific to the mobile. In reality, the

mask is a function of the mobile’s electronic serial

number (ESN).

The PCBs at 800 bps are then multiplexed with the

scrambled data stream at 19.2 Ksps. A PCB can be

punctured into any one of the first 16 bit positions of a

PCG (which contains 24 bits). The exact location of the

PCB in the PCG is determined in a pseudorandom

fashion. More specifically, given that the input of the

decimator is the long PN sequence, the PCB bit position

is determined by the decimal value of the four most

significant bits of the decimator output. It is important to

recognize that the exact location of the PCB in the PCG

is not fixed, but is determined in a pseudorandom

manner.

At this point, the multiplexed data stream (still at

19.2 Ksps) is orthogonally spread by the assigned Walsh

function. Each forward traffic channel is identified by its

assigned Walsh function. The spreading Walsh function

is at a rate of 1.2288 Mcps; each symbol is spread by a

factor of 64, and the result is a spread data stream at a

rate of 1.2288 Mcps. The data stream is further spread by

the assigned short PN sequence of the transmitting

sector. The short PN sequence provides a second layer of

isolation that distinguishes among the different

transmitting sectors. This way, all 64 available Walsh

functions can be reused in every sector.

3. SYSTEM IMPLEMENTATION

3.1 Design Consideration

The design considerations which are followed during

the design will be mentioned here.

First, as per IS-95 system architecture, our design

starts after the very first block i.e. vocoder. It means that

the input to our system will be the raw data stream at the

defined rate sets.

Secondly, the IS-95 as an international standard for

mobile communication has some strict real time

constraints. Even though, we have followed the protocol

with timing limitations, very strictly, the leaf blocks

which are used to develop the system do have some

latency. Our system modules deal with the data stream in

frames, and a frame of information data as defined by the

IS-95 standard has a span of 20ms. The modules that are

developed, although accepts data in a 20ms time frame,

but their processing require some time, because of the

latencies. Therefore as the system starts, it will take some

time to output the first frame, but then after there will be

no delay in the subsequent frames.

3.2 Cyclic Redundancy Check Generator

IS-95 CDMA use Cyclic Redundancy Check to

indicate the quality of each transmitted frame [1].

According to the standard, when the vocoder is operating

at full rate, each 20ms frame consists of 172 bits, thereby

giving the data rate of 8.6kbps. This data is input to the

CRC encoder to generate the 12 frame quality bits and 8

encoder tail bits. The 8 encoder tail bits consist of 0s and

are merely responsible for flushing the bits out from the

convolutional encoder which comes after the CRC

encoder. The generator polynomial used to generate the

frame quality bits for a full-rate frame is:

g (x) = x 12 + x 11 + x 10 + x 9 + x 8 + x 4 + x + 1

Input: Input data Frame @ 8.6 kbps according to Rate

set 1, i.e. 172 bits in 20-ms. Output: CRC encoded data

@ 9.6 kbps according to Rate set 1, i.e. 192 bits in 20-ms

which consists of 172 data bits, 12 frame quality bits and

8 encoder tails.

The basic blocks which are used for the

implementation are Shifter, LFSR and the Select Logic.

The input 172 bits are first passed through the shifter

block which first converts the serial input into the

decimal equivalent of the 172 bits. This is done because

the shifter block of the system generator only accepts

parallel input. This decimal value is then shifted by 20

places and is then again converted into the serial form.

The shifted serial bits are then passed through the LFSR

block. The LFSR consists of a series of registers and

XOR gates, in which the tapping is done according to the

generator polynomial specified above. The remainder

from the LFSR will be generated after 184 clock cycles

and this remainder will be then appended with the data

starting from the 172nd clock cycle. Therefore delays of

12 units have to be inserted in the data bits path. The

check bits (remainder) will be generated in parallel exact

at 184th clock cycle but will be appended in the serial

fashion. To make the check bits serial from MSBs to

LSBs, the select logic and the MUX is used. The Select

Logic Block is used in order to enable the MUXes at the

right time. There are 12 Muxes in all and one of the

inputs to each of the MUXes is the one of the outputs

from the LFSR.

The remainder is then ORed with the delayed data

stream, the MSB or the remainder is put at 172nd placed

and so on, the remainder ends at 184th place. Then the 8

tail bits follow, thus making the length of whole CRC

encoded frame equal to 192. Since there is a maximum of

4 input OR is available in the library, and the latency of

the OR gate is zero, multiple gates are used in order to

perform the desired operation.

LFSR

184 bits

12 bits

12

Remainder

bits

192 bits Frame

Figure 2: CRC Encoder

3.2 Convolutional Encoder

3.3 Convolutional Encoder

The Convolutional Encoder provides us powerful

error-correcting & encoding capability [1]. At the

receiver, the Viterbi Decoder is used to reverse this

encoder’s effect. Along with the Viterbi Decoder, the

convolutional encoder is a means of correcting a multiple

number of errors. It is an FEC technique that is

particularly suited to a channel in which the transmitted

signal is corrupted mainly by additive white Gaussian

noise (AWGN). AWGN can be thought of as noise

whose voltage distribution over time has characteristics

that can be described using a Gaussian, or normal,

statistical distribution, i.e. a bell curve [4].

Encoded bits are functions of information bits and the

number of memory elements. The information sequence

is shifted into a shift register k bits at a time. Bits are

tapped off at different stages of the shift register and

summed in a modulo-2 adder (XOR gate).

The convolutional encoder is defined by two

parameters:

1. Constraint Length K = No. of shift registers + 1.

This basically represents the number of

locations from where bits can be tapped of.

2. Rate = k/n. If there are n modulo-2 adders, it

means that for every k-bit shift, there will be an

output of n bits.

For the forward-link, IS-95 sets the constraint length

as K=9. i.e. an 8-bit shift register is used. The 8 encoder

tail bits mentioned in the previous section were added to

clear the contents of the shift register before the next

frame enters. IS-95 has defined the rate to be 1/2., which

means that there are two separate modulo-2 adders. So

for every one bit that enters the convolutional encoder,

two bits are received at the output. The generator

polynomials representing the modulo-2 adders are

G0 = x8 + x7 + x5 + x3 + x2 + x + 1

G1 = x8 + x5 + x4 + x3 + x2 + 1

It should be noted that there should be only one

output port from which the result of both modulo-2

adders is to be passed. Therefore, the output of both

modulo-2 adders has to be time-multiplexed. The input

rate of the convolutional encoder is 9.6 ksps (kilo

symbols per second); this rate will obviously double to

19.2

ksps.

G

XOR

In

XOR

G

T

I

M

E

repeater:

Input

Out

1

0

M

U

X

2s

4s

Figure 4: Input to Interleaver

Convolutional Encoder

Figure 3: Convolutional Encoder

While implementing the convolutional encoder, the

data was made to pass through an 8-bit shift register. The

modulo-2 adders were implemented simply by using

cascaded 2-input XOR gates. Inputs for the modulo-2

adders (i.e. XOR) were tapped from the 8-bit shift

register as specified in the generator polynomials. Finally

the output of the modulo-2 adders were time multiplexed

onto a single output port.

3.4 Symbol Repeater

Symbol repetition has the following benefits:

• Reduces probability of error

• Decreases power per repeated symbol when the

data rate is low

• Maintains an output data rate of 19.2ksps

regardless of input rate, in case of Rate Set I.

The probability of error is reduced because of having

the same symbol repeated redundantly.

We must maintain an output data rate of 19.2 ksps

(kilo symbols per second) because that is the fixed input

data rate of the next component, i.e.

the block

interleaver. For this purpose, the following scheme is

used. At full rate of 19.2 ksps, there is no need to repeat.

At half rate i.e. 9.6 ksps, we will need to repeat the

symbol once, so that every symbol is sent twice, meaning

that the rate at the output is 19.2 ksps. Similarly at 4.8

ksps, we repeat the symbol thrice. While at 2.4 ksps, we

repeat it 7 times

Consider a scaled-down example in which we take 2

sps as full rate. Suppose data arrives at ¼ rate i.e. 0.5 sps,

at the input. We send 1 0 1 to the input of the symbol

1

Now, according to the principle of symbol repetition,

we increase the symbol rate by 4. This is done by

repeating each received symbol 3 times at 2 sps

Output

1

1

1

1

1

0

1

2

0

0

1

1

1

0

4s

Figure 5: Interleaved Output

So effectively, there does not seem to be any

difference between the input signal and the output signal.

This seems to mean that no additional circuitry in the

symbol repeater. We just have a clock which samples

input at 19.2 ksps, regardless of the input rate .The block

interleaver needs input at 19.2 ksps, and therefore it must

have a clock that samples at 19.2 ksps. This means that

the clock of the interleaver serves as the symbol repeater,

we won’t need a separate module for the symbol

repeater.

3.5 Block Interleaver

Signals traveling through a mobile communication

channel are susceptible to fading. The error-correcting

codes are designed to combat errors resulting from fades

and, at the same time, keep the signal power at a

reasonable level. Most error-correcting codes perform

well in correcting random errors. However, during

periods of deep fades, long streams of successive or burst

errors may render the error-correcting function useless.

Interleaving is a technique for randomizing the bits in

a message stream so that burst errors introduced by the

channel can be converted to random errors [1]. Random

errors are then corrected by the FEC techniques

mentioned in the previous sections.

The interleaver consists of a 2D block or matrix of

shift registers. The transmitter reads encoder output

symbols into the matrix by rows until it is full. Then the

contents of the matrix are shifted out by columns. While

one matrix is filling the other is being emptied.

The interleaver of IS-95 consists of two 24 row by 16

column blocks. While one block is shifting horizontally

to receive input of the current frame, the other is shifting

vertically to give output of the previous frame.

3.6 Data Scrambling

After the data is interleaved, it is XORed with Long

PN Sequence. [5] The long PN code is generated in a 42

stage linear shift register generator with the output of the

42nd stage input into the first stage and modulo-2 added

with the outputs of stages 1, 2, 3, 5, 6, 7, 10, 16, 17, 18,

19, 21, 22, 25, 26, 27, 31, 33, and 35 as depicted in the

figure below. The output of the long code generator is

taken after the output of each flip-flop in the generator

has been added with a corresponding bit in a 42-bit mask

which is unique to each user, access, and paging channel.

Figure 6: Horizontal Shift (used to take input)

Figure 8: Long Code LFSR

Figure 7: Vertical Shift (used to take output)

The functionality of the block interleaver was

implemented first by creating the matrix of shift

registers. Every shift register in this block has two

possible input sources. The first source is the horizontal

predecessor and the other is the vertical predecessor.

Hence a multiplexer was required for each of the 384

shift registers. However the first register requires no

multiplexing as it always receives the input bit. When the

select pin of these MUXes was ‘0’, it results in a

horizontal shift indicating the input mode. When this pin

is ‘1’, it results in a vertical shift indicating the output

mode.

The block interleaver uses two instances of this

matrix. At any time, one of the matrices takes input (i.e.

shifts horizontally) while the other gives output (shifts

vertically). Hence selection logic is required to select a

matrix for input or output. This selection logic simply

consists of a counter that counts to 384. As soon as the

count reaches 384, the roles of the matrices are switched.

The matrix that was taking input is now giving output

and the second matrix is doing vice-versa.

To understand the manner in which the effect of the

interleaver is nullified, please refer to the Block

Deinterleaver section.

The output of the flip-flop is in parallel; therefore it is

then passed from the Parallel to Serial block at the rate of

1.2288 Mcps. The output of the interleave is at the rate of

0.02 / 384 Kbps, therefore in order to make the Long

code compatible so that bit wised XORed can be

performed; it is down sampled by 64. This XORed data

is then passed from the power control block.

3.7 Power Control

Power control is essential to the smooth operation of

a CDMA system. Because all users share the same RF

band through the use of PN codes, each user looks like

random noise to other users. The power of each

individual user, therefore, must be carefully controlled so

that no one user is unnecessarily interfering with others

who are sharing the same band [1]. The base station

sends the power-control commands to the mobile using

the forward link. These power-control commands are in

the form of power control bits (PCBs). The amount of

mobile power increase and power decrease per each PCB

is nominally +1 dB and -1 dB.

After the data is interleaved the PCBs at 800 bps are

multiplexed onto the baseband stream at 19.2 Kbps. The

PCBs are integrated into the traffic channel by robbing

selected bits from the baseband stream. This way, a

separate “channel” at 800 bps (for power-control

purposes) exists beneath the traffic channel. The stream

of PCBs at 800 bps is therefore called the power-control

subchannel (PCS). These PCBs are continuously

transmitted to the mobile by the base station. Note that

since the rate of PCB transmission is 800 bps, a PCB is

sent once every (1/800) second, or 1.25ms. Both

forward-link and reverse-link traffic channel frames are

20 ms in duration. Since one PCB is sent once every 1.25

ms, each traffic channel frame can be divided into (20

ms/1.25 ms) or 16 segments. These segments are called

power-control groups (PCGs). Since each power-control

group is 1.25 ms in duration and the baseband is at a rate

of 19.2 Kbps, then each power-control group contains

(19.2 ´ 103)(1.25 ´ 10-3) = 24 bits.

The decimated output of the LFSR is again down

sampled by 6 to make the rate 800bps. The position of

the PCB in each PCG is determined in the pseudorandom

fashion. The 4 most significant bits of the two times

decimated long code is converted into decimal and then it

is used to control the MUX whose inputs are the first 16

bits of the PCG. Therefore the power bit can have any

place from 0 to 15 in each PCG. In this way the whole

power is distributed in the frame.

Figure 9: Power Spreading

3.8 Walsh Spreading

In order to avoid mutual interference on the forward

link, Walsh codes are used to separate individual users

while they simultaneously occupy the same RF band.

Walsh codes as used in IS-95 are a set of 64 binary

orthogonal sequences [1], [11]. These sequences are

orthogonal to each other, and they are generated by using

the Hadamard matrix. Recursion is used to generate

higher order matrices from lower order ones; that is,

Where ĤN contains the same but inverted elements of HN.

The seed matrix is:

The IS-95 forward link uses a set of 64 orthogonal

Walsh sequences, thus the physical limitation on the

number of channels on the forward link is 63 because in

an IS-95 system, w0 is not used to transmit any baseband

information.

In the implementation, all the 63 possible 64-bit

Walsh codes are placed in separate ROMs. A particular

channel will use only one Walsh code. The message m (t)

is up-sampled by a factor of 64. In other words, every bit

is repeated 64 times. Each repeated bit is XNORed with a

bit in the Walsh code w (t). The XNOR gate serves as a

multiplier that is unique for every channel. Its output is

called the product of m (t) and w (t). Effectively each

message bit mi(t) is multiplied with each Walsh code bit

wi(t). This product can be represented as mi(t)wi(t) and it

has two possible values: 0 and 1.

The output of the XNOR gate is then passed through

a unipolar-to-bipolar converter that basically converts 0

to -1, while 1 is left as it is. So now the signal has two

possible values: -1 and 1. The output of the unipolar-tobipolar converter of every channel is now added, the

result can be represented as Σ mi(t)wi(t). This output

varies from -63 to +63; i.e. the output has 7 bits coming

in parallel. These parallel bits are made to pass serially

through the single-bit output. The final output appears

completely different from the input.

Effectively, the input rate of 19.2 ksps has been

increased firstly before the multiplier by a factor of 64.

Then it is further increased by a factor of 7 at the output.

In all, the output rate of the Walsh Spreader comes out to

be 19.2ksps * 64 * 7= 8.6016 Msps.

To understand the manner in which the data is

retrieved, please refer to the Walsh Despreader.

3.9 Short PN Spreading

In a CDMA system the PN code sequence is mainly used

for code spreading, code scrambling, and code division

[12], [9]. Code spreading spreads the channel power

across the whole channel, the scrambling gives additional

data security and the code division expands the channel

capacity. Code division by PN code offset is used in the

IS-95 system. The channels use the same PN sequence

but skewed in time with reference to a common

reference. The PN code is characterized by a Polynomial,

where the degree of the polynomial is equal to the

number of stages in the generating register. In the

Cellular and PCS systems as per IS- 95, the quadrature

modulation in forward and reverse link is performed by

using two distinct PN sequences generated by 15 stage

shift registers and lengthened by one chip to 215 = 32,768

chips. At a rate of 1.2288 Mcps, the sequence repeats

every 26.66 ms or 75 times every 2 seconds [12]. The

characteristic polynomial for in-phase (I) and quadraturephase (Q) sequence are:

G0 = x15 + x13 + x9 + x8 + x7 + x5 + 1

G1 = x15 + x12 + x11 + x10 + x6 + x5 + x4 + x3

The implementation for the I and Q PN sequence is done

by the shift registers and the XOR gates as defined by the

polynomial.

3.10 Walsh Despreading

The Walsh Despreader is a component on the

receiver side, whose purpose is to nullify the effect of

Walsh spreading. The Walsh spreader was used to merge

the data of all 63 channels. But the Walsh Despreader

will extract the data of any one of the channels. Hence, it

only uses one Walsh code unique to that particular

channel.

The implementation of the Walsh despreader is as

follows. The output of the multiplier in the Walsh

spreader has a value varying from -63 to +63; i.e. the

output has 7 bits coming in parallel. But the 7 bits are

sent serially through the final output. The first task of the

Walsh Despreader is to collect 7 serially entering bits and

convert them to parallel. Once again we have values

ranging from -63 to +63, which represent Σ mi(t)wi(t).

The bits of the Walsh code (stored in memory) are

first passed one by one through a unipolar-to-bipolar

converter. So each bit has been converted to -1 or +1.

These values are multiplied by the incoming values of

Σ mi(t)wi(t). The products are sent into an adder that takes

64 such products as input. The output of this sum is

represented as Mi(t). A “decision threshold” looks at the

integrated function Mi(t ).The decision rules used are

m(t) = 0

if M(t) < 0

m(t) = 1

if M(t) > 0

The output data rate is 19.2 Ksps.

3.11 Descrambler

This is a hierarchical block performing power

bit extraction and descrambling. It extracts the power bit

for each PCG using the long code and combines the

signals from all fingers. The extracted power bit is

updated once every power group, that is, 16 times every

20 ms frame. There are two symbols carrying the power

control bit in Rate. After power bit extraction the block

sets to zero the symbol corresponding to the power

control bit. The block subsequently descrambles the

combined signal using the decimated long code

sequence. Synchronization between the sender and the

receiver is the most important thing while decoding.

Even if the synchronization is missed with only one bit

place the descrambler output can be highly affected

because it performs the same XOR function as was

performed on the receiver side to decrypt the data bits.

3.12 Block Deinterleaver

At the receiving end, the block deinterleaver nullifies

the effect of the block interleaver. T deinterleaver

reconstructs the message using the same matrix (block),

except in this case the deinterleaver loads the received

message into columns first, and then reads the message

out from the rows.

The block deinterleaver uses two instances of this

matrix. At any time, one of the matrices takes input (i.e.

shifts vertically) while the other gives output (shifts

horizontally). Hence selection logic is required to select a

matrix for input or output. This selection logic simply

consists of a counter that counts to 384. As soon as the

count reaches 384, the roles of the matrices are switched.

The matrix that was taking input is now giving output

and the second matrix is doing vice-versa.

The output of the deinterleaver will contain

information with random errors, i.e. the probability of

two contiguous erroneous bits is very much less. This is

so because the interleaver caused consecutive bits to

become far apart from each other, so burst errors in the

channel do not affect the consecutive bits. The absence of

no continuous erroneous bits makes it easier for the

Viterbi Decoder to correct the scattered random errors

3.13 Symbol Derepeater

At the receiver, the symbol derepeater works like a

voter. It simply counts how many of the repeated

symbols are 1 and how many are 0. If the number of 1s is

greater, the output is a 1. If the number of 0s is greater,

the output is a 0.

Naturally, the voter’s parameters depend on the data

rate. At full rate, there will be no voting. This is so

because full rate does not require repetition in the first

place. At ½ rate, the voter will check for majority in 2

symbols. At ¼ rate, the voter will check for majority out

of 4 symbols. At 1/8 rate, the voter will check for

majority out of 8 symbols.

The implementation was carried out by developing

separate circuitry for each rate. The basic functionality

was the same. Consider the circuit for ¼ rate. This circuit

consisted of an adder that sums 4 incoming bits. If this

value is greater than 2, the output is 1. If the value is less

than or equal to 2, the output is 0. The immediate

question that arises is that if the sum is 2, it indicates

equality, so why was the output set to 0. The answer is

that it does not create much of a difference. The Viterbi

decoder is able to correct multiple errors.

3.14 Viterbi Decoder

This block decodes a convolutionally encoded

information sequence optimally [6], [4]. In the IS-95

system, the constraint length of the viterbi decoder is 9.

The Viterbi algorithm searches through the trellis, which

defines all possible allowed sequences determined by the

encoder, for the most probable sequence. This is done by

updating likelihood metric for each possible choice of the

decoded sequence and selecting the paths corresponding

to the best metric choices. Finally, it outputs the decoded

data along with the metric for the final detected path. The

decoder performs a traceback along the survivor paths in

the trellis to generate the output bits. Since the traceback

is started in the zero state, so the last 8 bits of the

sequence being decoded must be 0, which indicates the

flush bits that were inserted in the CRC encoding

process. We do not have implemented the viterbi decoder

from the basic blocks, but have used the one that is

already provided in the library.

3.15 Frame Quality Indicator.

The effect of the CRC Generator is cancelled out by

the Frame Quality Indicator. Actually, this component

can be considered as “the last resort”. It checks to see if

the data is correct. If the data is correct, it is allowed to

move forward. However, if it is not, it stops it from

moving forward to the output.

Consider full rate transmission. The Frame Quality

Indicator extracts the 184 bits out of the 192 bit frame.

The remaining 8 bits are supposed to be 0.These 184 bits

are made to pass through an LFSR similar to the LFSR of

the CRC Generator. If the output of the LFSR is 0, it

indicates correct data.

4. SYNTHESIS AND RESULTS

After having developed the various submodules of

the mentioned architecture, those submodules were

integrated. The final simulation was run on Simulink.

Next, the hardware co-simulation feature of the System

generator was used to create a library of the separate

submodules. The blocks in this library were basically the

HDL versions of the submodules. These library blocks

were used to recreate the design, and the bit file was then

generated. Finally the bit file was dumped into the

Viterx2 xcv3000 FPGA with a speed grade of -4. A

simple application which consists of the microphone at

the transmitter and the speaker at the receiver was used to

test the dumped system.

5. CONCLUSION

Xilinx System generator is a powerful tool for

accurately translating the simulated design into HDL,

hence making it suitable for creating FPGA

implementation. System architecture based on the

forward Traffic channel of the IS-95 system has been

discussed, and briefly their implementation using the

library blocks of the Xilinx System Generator has been

presented. Finally a simple application demonstrating the

FPGA implementation has been presented.

References

[1] Samuel C. Yang, NCDMA RF SYSTEM

ENGINEERIN . London: Artech House

[2] CDMA DESIGN LIBRARY . Agilent Technologies,

2003.

[3] ACOLADE IS-95-A / CDMA LIBRARY OVERVIEW.

ICUCOM Corporation, 1996.

[4] Chip Fleming, “A Tutorial on Convolutional Coding

with Viterbi Decoding” Spectrum Applications.

[5] www.cdmaonline.com

[6] Richard B. Wells, APPLIED CODING AND

INFORMATION THEORY FOR ENGINEERS.

[7] CDMA DESIGN LIBRARY . Agilent Technologies,

2003.

[8] XILINX SYSTEM GENERATOR v 2.1 BASIC

TUTORIAL. U.S.A.

[9] CODE DIVISION MULTIPLE ACCESS – A

TUTORIAL . Amol Shah, 1999

[10] RECONFIGURABLE MODULE TO SUPPORT

MULTIPLE CDMA STANDARDS. Nara Doriswamy,

Metuchen, N.J.

[11] TECHNICAL INTRODUCTION TO CDMA

v3.23, Scott Baxter, 2003.

[12] RECONFIGURABLE MODULES TO SUPPORT

MULTIPLE CDMA STANDARDS.,

Nara Doriswamy, Metuchen, N.J.