Memory: Page Tables

advertisement

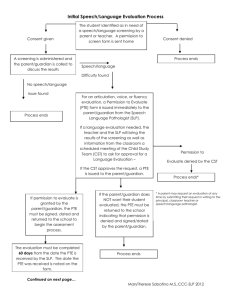

Memory Copyright ©: University of Illinois CS 241 Staff 1 Application Perspective (Reserved for OS) Stack Lots of separate processes Heap Uninitialized vars (BSS segment) Initialized vars (data segment) Code (text segment) (Reserved for OS) Stack Heap (Reserved for OS) Stack MMU Uninitialized vars (BSS segment) Initialized vars (data segment) Code (text segment) Heap Uninitialized vars (BSS segment) Initialized vars (data segment) Code (text segment) Physical RAM Copyright ©: University of Illinois CS 241 Staff 2 Address Translation Scheme Address generated by CPU is divided into Page number (p) An index into a page table Contains base address of each page in physical memory Page offset (d) Combined with base address Defines the physical memory address that is sent to the memory unit Page Number Page Offset P1 P2 D m-n n For given logical address space 2m and page size 2n Copyright ©: University of Illinois CS 241 Staff 3 Virtual addressing Used in all modern servers, desktops, and laptops One of the great ideas in computer Main memory science 0: CPU Virtual address (VA) 4100 CPU Chip MMU ... 1: 2: Physical address 3: (PA) 4: 4 5: 6: 7: 8: M-1: Data word Copyright ©: University of Illinois CS 241 Staff 4 Data Structure: Page Table A page table is an array of page table entries (PTEs) that maps virtual pages to physical pages Per-process kernel data structure in DRAM Physical page number or Valid disk address PTE 0 0 null 1 1 0 1 0 0 PTE 7 1 Physical memory (DRAM) VP 1 VP 2 VP 7 VP 4 PP 0 PP 3 Disk VP 1 null VP 2 VP 3 Memory resident page table (DRAM) VP 4 VP 6 Copyright ©: University of Illinois CS 241 Staff VP 7 5 Page Hit Reference to VM word that is in physical memory (DRAM cache hit) Virtual address Physical page number or Valid disk address PTE 0 0 null 1 1 0 1 0 0 PTE 7 1 Physical memory (DRAM) VP 1 VP 2 VP 7 VP 4 PP 0 PP 3 Disk null VP 1 VP 2 Memory resident page table (DRAM) Copyright ©: University of Illinois CS 241 Staff VP 3 VP 4 VP 6 VP 7 6 Page Fault Reference to VM word that is not in physical memory (DRAM cache miss) Virtual address Physical page number or Valid disk address PTE 0 0 null 1 1 0 1 0 0 PTE 7 1 Physical memory (DRAM) VP 1 VP 2 VP 7 VP 4 PP 0 PP 3 Disk null VP 1 VP 2 Memory resident page table (DRAM) Copyright ©: University of Illinois CS 241 Staff VP 3 VP 4 VP 6 VP 7 7 Handling Page Faults Page miss causes page fault (an exception) Virtual address Physical page number or Valid disk address PTE 0 0 null 1 1 0 1 0 0 PTE 7 1 Physical memory (DRAM) VP 1 VP 2 VP 7 VP 4 PP 0 PP 3 Disk null VP 1 VP 2 Memory resident page table (DRAM) Copyright ©: University of Illinois CS 241 Staff VP 3 VP 4 VP 6 VP 7 8 Handling Page Faults Page fault handler selects a victim to be evicted (here VP 4) Virtual address Physical page number or Valid disk address PTE 0 0 null 1 1 0 1 0 0 PTE 7 1 Physical memory (DRAM) VP 1 VP 2 VP 7 VP 4 PP 0 PP 3 Disk null VP 1 VP 2 Memory resident page table (DRAM) Copyright ©: University of Illinois CS 241 Staff VP 3 VP 4 VP 6 VP 7 9 Handling Page Faults Loads new frame into freed slot Virtual address Physical page number or Valid disk address PTE 0 0 null 1 1 1 0 0 0 PTE 7 1 Physical memory (DRAM) VP 1 VP 2 VP 7 VP 3 PP 0 PP 3 Disk null VP 1 VP 2 Memory resident page table (DRAM) Copyright ©: University of Illinois CS 241 Staff VP 3 VP 4 VP 6 VP 7 10 Handling Page Faults Offending instruction is restarted: page hit! Virtual address Physical page number or Valid disk address PTE 0 0 null 1 1 1 0 0 0 PTE 7 1 Physical memory (DRAM) VP 1 VP 2 VP 7 VP 3 PP 0 PP 3 Disk null VP 1 VP 2 Memory resident page table (DRAM) Copyright ©: University of Illinois CS 241 Staff VP 3 VP 4 VP 6 VP 7 11 Page Table Entry Why is the page number 20 bits wide? 1 1 1 2 M R V prot 20 page frame number Copyright ©: University of Illinois CS 241 Staff 12 Page Table Entry Why is the page number 20 bits wide? 1 1 1 2 M R V prot Because that’s how many bits you use to refer to pages!, 20 page frame number Each page is 4KB Need 12 bits to refer to offset within page Copyright ©: University of Illinois CS 241 Staff 13 Address Translation with a Page Table Page table base register (PTBR) Page table address for process n-1 p p-1 Virtual address 0 Virtual page offset (VPO) Virtual page number (VPN) Page table Valid Physical page number (PPN) Valid bit = 0: page not in memory (page fault) m-1 p p-1 0 Physical page number (PPN) Physical page offset (PPO) Physical address Copyright ©: University of Illinois CS 241 Staff 14 Address Translation: Page Hit 2 PTEA CPU Chip CPU 1 VA PTE MMU 3 PA Cache/ Memory 4 Data 5 1) Processor sends virtual address to MMU 2-3) MMU fetches PTE from page table in memory 4) MMU sends physical address to cache/memory 5) Cache/memory sends data word to processor Copyright ©: University of Illinois CS 241 Staff 15 Address Translation: Page Fault Exception Page fault handler 4 2 PTEA CPU Chip CPU 1 VA 7 MMU PTE 3 Victim page 5 Cache/ Memory Disk New page 6 1) Processor sends virtual address to MMU 2-3) MMU fetches PTE from page table in memory 4) Valid bit is zero, so MMU triggers page fault exception 5) Handler identifies victim (and, if dirty, pages it out to disk) Copyright ©: University of Illinois CS 241 Staff 16 Address Translation: Page Fault Exception Page fault handler 4 2 PTEA CPU Chip CPU 1 VA 7 MMU PTE 3 Victim page 5 Cache/ Memory Disk New page 6 6) Handler pages in new page and updates PTE in memory 7) Handler returns to original process, restarting faulting instruction Copyright ©: University of Illinois CS 241 Staff 17 Question 1: Memory Acceses Isn’titslowtohavetogotomemory twice every time? Yes,itwouldbe…so,realMMUsdon’t Copyright ©: University of Illinois CS 241 Staff 18 Speeding up Translation: TLB Page table entries (PTEs) are cached in L1 like any other memory word PTEs may be evicted by other data references PTE hit still requires a small L1 delay Solution: Translation Lookaside Buffer (TLB) Small, dedicated, super-fast hardware cache of PTEs in MMU Contains complete page table entries for small number of pages Copyright ©: University of Illinois CS 241 Staff 19 TLB Hit CPU Chip CPU TLB 2 PTE VPN 3 1 VA MMU PA 4 Cache/ Memory Data 5 A TLB hit eliminates a memory access Copyright ©: University of Illinois CS 241 Staff 20 TLB Miss CPU Chip TLB 2 4 PTE VPN CPU 1 VA MMU 3 PTEA PA Cache/ Memory 5 Data 6 A TLB miss incurs an additional memory access (the PTE) Fortunately, TLB misses are rare. Why? Copyright ©: University of Illinois CS 241 Staff 21 Question 2: Size Isn’tthepagetablehuge?Howcanit be stored in RAM? Yes,itwouldbe…so,realpagetables aren’tsimplearrays Copyright ©: University of Illinois CS 241 Staff 22 Page Table Size Suppose 4KB (212) page size, 64-bit address space, 8-byte PTE How big does the page table need to be? Copyright ©: University of Illinois CS 241 Staff 23 Page Table Size Suppose 4KB (212) page size, 64-bit address space, 8-byte PTE How big does the page table need to be? 32,000 TB! 264 * 2-12 * 23 = 255 bytes Copyright ©: University of Illinois CS 241 Staff 24 Multi-Level Page Tables Level 2 Tables Common solution Multi-level page tables Example: 2-level page table Level 1 table Each PTE points to a page table (always memory resident) Level 2 table ... Level 1 Table ... Each PTE points to a page (paged in and out like any other data) Copyright ©: University of Illinois CS 241 Staff 25 Addressing on Two-Level Page Table 32-bit Architecture Page Number 4K Page of Logical Memory 4096= 212 B Page 4096 addressable bytes Page the Page Table 4K pages as well 1024 addressable 4byte addresses Page Offset P1 P2 D 12 10 10 Copyright ©: University of Illinois CS 241 Staff 26 2-level page table hierarchy Level 1 page table Level 2 page tables Physical memory 0 PTE 0 ... PTE 0 PTE 1 ... VP 1023 PTE 2 (null) PTE 1023 VP 1024 VP 0 2K allocated VM pages for code and data ... PTE 3 (null) VP 2047 PTE 4 (null) PTE 0 PTE 5 (null) ... PTE 6 (null) PTE 1023 Gap PTE 7 (null) 6K unallocated VM pages PTE 8 (1K - 9) null PTEs PTE 1023 1023 unallocated pages VP 9215 Copyright ©: University of Illinois CS 241 Staff ... 32 bit addresses 4KB pages, 4-byte PTEs 1023 null PTEs 1023 unallocated pages 1 allocated VM page for the stack 27 Address Translation: k-level Page Table VIRTUAL ADDRESS n-1 VPN 1 VPN 2 Level 2 page table Level 1 page table ... ... ... p-1 VPN k 0 VPO Level k page table PPN m-1 p-1 PPN 0 PPO PHYSICAL ADDRESS Copyright ©: University of Illinois CS 241 Staff 28 Addressing on Two-Level Page Table page number page offset CPU p d 0 1 p-1 p p+1 Page frame number f d Page frame number 0 1 .. . .. . f .. . f-1 f f+1 f+2 physical memory page table Copyright ©: University of Illinois CS 241 Staff 29 Multilevel Page Tables With two levels of page tables, how big is each table? Allocate 10 bits to the primary page 10 bits to the secondary page 12 bits to the page offset Copyright ©: University of Illinois CS 241 Staff 30 Multilevel Page Tables What happens on a page fault? MMU looks up index in primary page table to get secondary page table MMU tries to access secondary page table May result in another page fault to load the secondary table! MMU looks up index in secondary page table to get physical frame # CPU can then access physical memory address Copyright ©: University of Illinois CS 241 Staff 32 Multilevel Page Tables Issues Page translation has very high overhead Up to three memory accesses plus two disk I/Os!! TLB usage is clearly very important Copyright ©: University of Illinois CS 241 Staff 33 Page Table Problem (from Tanenbaum) Suppose 32-bit address Two-level page table Virtual addresses split into a 9-bit top-level page table field, an 11-bit second-level page table field, and an offset Question: How large are the pages and how many are there in the address space? Offset Page size # virtual pages Copyright ©: University of Illinois CS 241 Staff 34 Question 3: So What? Is there any other super slick stuff can I do with page tables? Yes! Copyright ©: University of Illinois CS 241 Staff 36 Paging as a tool for protection Extend PTEs with permission bits Page fault handler checks these before remapping If violated, send process SIGSEGV (segmentation fault) SUP READ WRITE Process i: Address VP 0: No Yes No PP 6 VP 1: No Yes Yes PP 4 VP 2: Yes Yes Yes • • • PP 2 Physical Address Space PP 2 PP 4 PP 6 SUP READ WRITE Process j: Address VP 0: No Yes No PP 9 VP 1: Yes Yes Yes PP 6 VP 2: No Yes Yes PP 11 Copyright ©: University of Illinois CS 241 Staff PP 8 PP 9 PP 11 37 VM as a tool for sharing Process 1 virtual memory Physical memory Shared object Process 2 virtual memory Process 1 maps the shared object Copyright ©: University of Illinois CS 241 Staff 38 VM as a tool for sharing Process 1 virtual memory Physical memory Process 2 virtual memory Shared object Process 2 maps the shared object Notice how the virtual addresses can be different Copyright ©: University of Illinois CS 241 Staff 39 Protection + Sharing Example fork() creates exact copy of a process Lotsmoreonthisnextweek… When we fork a new process, all of the memory is duplicated for the child Does it make sense to make a copy of all of its memory? What if the child process doesn't end up touching most of the memory the parent was using? Copyright ©: University of Illinois CS 241 Staff 40 Performance + Sharing Some processes may need to access the same memory Copy-on-Write (COW) Allows parent and child processes to initially share the same pages in memory Only copy page if one of the processes modifies the shared page More efficient process creation Copyright ©: University of Illinois CS 241 Staff 41 Copy-on-Write 1. 2. Parent forks a child process Child gets a copy of the parent's page tables Parent (Reserved for OS) Child Parent's page tbl Child's page tbl (Reserved for OS) Stack Stack Heap Heap Uninitialized vars Initialized vars Uninitialized vars Initialized vars Code Code They point to the same physical frames!!! Copyright ©: University of Illinois CS 241 Staff 42 Copy-on-Write All pages (both parent and child) marked read-only Why? Parent (Reserved for OS) Child Parent's page tbl Child's page tbl (Reserved for OS) Stack Stack Heap Heap Uninitialized vars Initialized vars Uninitialized vars Initialized vars Code Code Copyright ©: University of Illinois CS 241 Staff 43 Copy-on-Write What happens when the child reads the page? Just accesses same memory as parent .... Niiiiiice! Parent (Reserved for OS) Child Parent's page tbl Child's page tbl (Reserved for OS) Stack Stack Heap Heap Uninitialized vars Initialized vars Uninitialized vars Initialized vars Code Code Copyright ©: University of Illinois CS 241 Staff 44 Copy-on-Write What happens when the child writes the page? Protection fault occurs (page is read-only!) OS copies the page and maps it R/W into the child's addr space Parent (Reserved for OS) Child Parent's page tbl Child's page tbl (Reserved for OS) Stack Stack Heap Heap Uninitialized vars Initialized vars Uninitialized vars Initialized vars Copy page Code Code Copyright ©: University of Illinois CS 241 Staff 45 Copy-on-Write What happens when the child writes the page? Protection fault occurs (page is read-only!) OS copies the page and maps it R/W into the child's addr space Parent (Reserved for OS) Child Parent's page tbl Child's page tbl Stack Stack RW Heap Uninitialized vars Initialized vars (Reserved for OS) Copy page Heap Uninitialized vars Initialized vars Code Code Copyright ©: University of Illinois CS 241 Staff 46 Sharing Code Segments Shell #1 (Reserved for OS) Stack Shell #2 Heap Uninitialized vars Initialized vars (Reserved for OS) Stack Same page table mapping! Code for shell Code Heap Uninitialized vars Initialized vars Code Copyright ©: University of Illinois CS 241 Staff 47