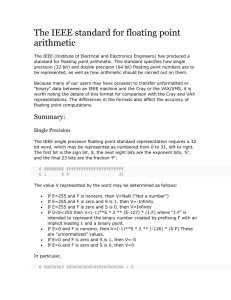

Floating Point Arithmetic Chapter 14

advertisement