Standard Cell DataSheet

advertisement

PDK45 Cell Name

Student Names on Design Team

Design Team Group Number

Date

Introduction and Physical Properties

Cell Description

Describe, in your own words the cell’s Boolean function and typical

applications of the cell. This section requires more than a single sentence.

For example, the inverter is a simple logic function but also provides the

basic cell for the delay modeling.

Cell Symbol

Where applicable use standard logic symbols (i.e. INVERTER, NAND,

NOR, AOI has a standard symbol) for the assigned standard cells. This will

require editing the symbol after Cadence NSCU CDK creates the boring

square or rectangular default symbol. [Note: There are two “extra” pins

inside the inverter symbol. These pins may be needed for a workaround

when simulating the extracted view of the physical design later in the term

and next quarter. The top symbolic pin is for the VDD and the lower for

GND. If they are not needed they can be dropped in the schematic as well as

in this picture.]

Figure 1: Example Logic Symbol from NCSU Digital Parts

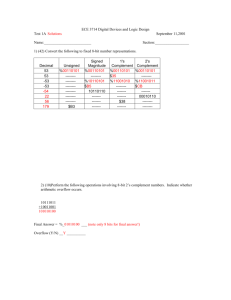

Cell Truth Table

Complete the truth table for all cell outputs using {0, 1} for the input low

and high, respectively and {L, H} for the output low and high, respectively.

Repeat rows and columns as needed.

Robert Daasch

Page 1

15 February 2016

0

0

…

Cell Truth Table

Cell Inputs {0,1}

Cell Outputs {L,H}

0

0

H

0

1

L

Cell Schematic Diagram

Prepare Encapsulated Postscript of the schematic for publication (Cadence

has this option in the Virtuoso schematic design). Do not use a screen shot or

create Encapsulated Postscript of the raw schematic from a screen shot. For

each “publication schematic” in NSCU CDK remove the transistor width

and length, model name etc. but leave the instance names of the pins and

transistor. This makes the schematic easier to read.

Figure 2: Example Schematic from NCSU CDK Publication Schematic

Cell Layout Diagram and Dimensions

Save a color or black and white layout of the cell in EPS (i.e. Encapsulated

Postscript) format. The cell dimensions are saved in both lambda (note

complete table header with conversion nanometers of ) and microns (m).

Record the transistor length and width dimensions (nm).

[Repeat the transistor row as needed.]

Cell Physical Dimensions (nm/)

X

Y

Cell Dimension in

Cell Dimension in m

Transistor Dimensions

Transistor Instance

Length

Width (nm)

Number

(nm)

Robert Daasch

Page 2

15 February 2016

Performance Analysis

[Note: Split the simulation work load among the team members so that each

team member learns how to use the tools.]

Combinational Logic Propagation Delays

Simulate propagation delays (low to high tplh and high to low tphl) for the

worst case single input transition for the range of output loads shown in the

table. For multiple input logic gates add copies of the table below as

needed. Use a 1.2V power supply and 50% of the rail for measurement.

Any negative value is 0. Label the tables with worst case input in each stack

and the output.

Low to High Propagation Delay Data tplh (ns)

Input fall

Output Load (FOx)

time (ns)

0

1

2

4

0.02

High to Low Propagation Delay Data tphl (ns)

Input rise

Output Load (FOx)

time (ns)

0

1

2

4

0.02

8

8

From slew rate data compute the best fit linear propagation delay equation

for low-to-high tplh and high-to-low tphl.

Summarize your linear delay model in the table below. The ‘All data’ row is

the slope and intercept by averaging the propagation delays tplh and tphl for

rising and falling input slew rates at each FOx load. For multiple input logic

gates add copies of the table below as needed.

Robert Daasch

Page 3

15 February 2016

Logical Effort Propagation Delay Equation Coefficients

tavg = p + g·h where h is the FOx=Cout/Cin

Input Slew

Rate (ns)

All data 0.02

Rising Logical Effort (g)

Parasitic Falling Delay (p)

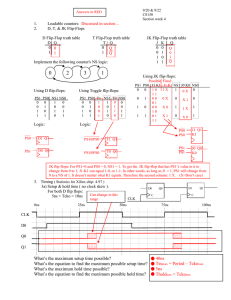

D Flip-Flop Characterization

The D Flip-Flop is characterized by four values for the Clock-to-Q delays,

the setup time and the hold time. Use simulation to estimate the 4 D FlipFlop characterization parameters.

Input Slew

(ns)

Clock-to-Q tccq, tpcq (pS)

Output Load (FOx)

1

2

4

0

tccq

tpcq

tccq

tpcq

tccq

tpcq

tccq

8

tpcq

tccq

tpcq

0.02

Input Slew

(ns)

Setup and Hold tsetup, thold (pS)

Output Load (FOx)

0

1

2

4

tsetup

thold

tsetup

thold

tsetup

thold

tsetup

8

thold

tsetup

thold

0.02

Robert Daasch

Page 4

15 February 2016