High k Gate Dielectrics for Transistors

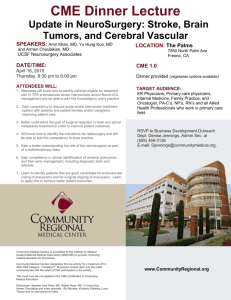

advertisement

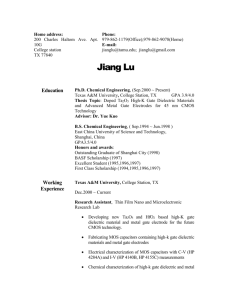

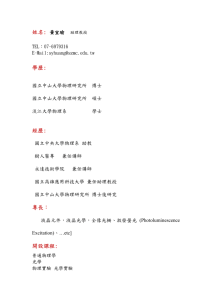

High k Gate Dielectrics for Transistors High k gate dielectrics are required for the sub-65 nm MOS structure because the conventional SiO2 film is too thin (e.g. 2 nm) to minimize the tunneling current and the out diffusion of boron from the gate. A thick layer can be used with the high k material to lower the parasitic capacitance. Many issues have to be solved before it is acceptable for the products. In general, there are three types of high k dielectrics: 1. those with 4 < k < 10 such as SiNx; 2. those with 10 < k < 100 such as Ta2O5, Al2O3, ZrO2, and HfO2; and 3. those with 100 < k such as PZT. The type 2 dielectric film has been routinely used in transistors, such as TFTs. A thick layer is used to prevent the top-to-bottom metal shortage, which is a killing factor for the yield. The high k dielectric material is usually used in combination with a high quality dielectric interface layer to lower the interface density of states. For example, in the a-Si:H TFT case, the N-rich SiNx is exclusively used as the interface layer. Examples on TFTs with the dual gate dielectric structure (e.g. SiNx/TaOx and two different types of SiNx/SiNx) are shown as follows. We are researching on new type of high k dielectric materials using elements throughout the whole Periodical Table. The goals are to find new high k thin films that have enhanced dielectric constants and low leakage currents. We are also working on high-k based new devices, such as the nonvolatile memories where nanocrystals are embedded in the dielectric layer. . Nanocrystals Embedded High-k for Nonvolatile Memories (see Nonvolatile Memories for more information) - nc-ITO Embedded Zr-doped HfO2 A. Birge, C.-H. Lin, and Y. Kuo, “Memory Functions of Nanocrystalline Indium Tin Oxide Embedded Zirconium-Doped Hafnium Oxide MOS Capacitors,” JES 154(10) H887 (2007) - nc-ZnO Embedded Zr-doped HfO2 J. Lu, C.-H. Lin, and Y. Kuo, “Nonvolatile Memories Based on Nanocrystalline Zinc Oxide Embedded Zirconium-doped Hafnium Oxide Thin Films,” ECST 11(4), 509-518 (2007). - nc-Si Embedded Zr-doped HfO2 J. Lu, Y. Kuo, J. Yan, and C.-H. Lin, “Nanocrystalline Silicon Embedded Zirconium-Doped Hafnium Oxide High-k Memory Device,” JJAP 45(34) L901 (2006). - nc-RuOx Embedded Zr-doped HfO2 and RuZrHfO C.-H. Lin, Y. Kuo, and J. Lu, “Influence of Ru Dopant on the Dielectric Properties of Zr-doped HfO2 High-k Thin Film,” ECST 6(1) 121 (2007). - nc-RuOx Embedded Zr-doped HfO2 Reliability TiN/ ZrHfOx/RuOx/ZrHfOx/p-Si R. Wan, C.-H. Lin, Y. Kuo, and Way Kuo, “Charge Trapping of Ultra-thin ZrHfOx/RuOx/ZrHfOx High-k Stacks,” IIRW 2007. Doping of TaOx and HfO2 films - Sub 1 nm EOT Zr-doped HfO2 J. Yan, Y. Kuo, and J. Lu, “Zirconium-Doped Hafnium Oxide High-k Dielectrics with Subnanometer Equivalent Oxide Thickness by Reactive Sputtering,” ESL 10(7), H199 (2007). - Effects on bulk material properties - Suppression of crystal formation JES Letters (Accepted to appear in 2004) XRD Patterns of TaOx (a) undoped, (b) Al-doped, (c) Si-doped, (d) Ti-doped films, 700°C, 10 Minutes - Effects on interface layers - Interface formation problems and improvement Lu, Kuo, Tewg, and Schueler, Vacuum, 539-547, 2004. (Courtesy of B. Foran of SEMATECH) J. Lu, Y. Kuo, and J.-Y. Tewg, JES 153(5) G410 (2006). - Interface modification by inserted 5Å TaNx Tewg, Kuo, Lu, and Schueler, “Influence of a 5 Å Tantalum Nitride Interface Layer on Dielectric Properties of Zirconium-Doped Tantalum Oxide High-k Films,” JES 2005. Kuo, Lu, and Tewg, JJAP 42 (3), Pt. 2, No. 7A, 2003 ESCA of Ta chemical states of the deposited TaNx interface layer after 700ºC 10 min O2 annealing. Kuo, Lu and Tewg, JJAP 42, L769, 2003 - Effects on electric properties - Increase of k value Kuo, Lu and Tewg, JJAP 42, L769, 2003. Measured k as a Function of the Dopant Zr Co-Sputtering Power AVS ICMI Meeting, 02/13/02. k vs. Film Thickness 700°C 10 min annealed Y. Kuo. SEMATECH, Stacked Gate Dielectric Meeting Procs. Austin, TX. 05/22/01 Y. Kuo, J. Y. Tewg, and J. Lee. AVS 3rd Natl. Microelectronics and Interfaces, 133-135, 2002. Y. Kuo, J. Y. Tewg J. Donnelly, and J. Lee. Proc. 1st Natl. Conf. Semi-conductor Tech., ECS. Vol. 2001-17, 324-327, 2001. - Decrease of leakage current Kuo, Lu and Tewg, JJAP 42, L769, 2003. Leakage vs. Dopant Target Sputtering Power 600°C 60 min annealed AVS ICMI Meeting, 02/13/02. J-E curves of the Zr-doped HfOx films, including pure HfOx. J. Yan, Y. Kuo, S. Chatterjee, and J. Lu, “Electrical Characterization of Doped Hafnium Oxide High-k Films,” 2005 ECS Abstract. W. Luo, et al., IEEE IRW 2.1.1, 2003 - Enhance breakdown strength J. Lu, Y. Kuo, and J.-Y. Tewg, JES 153(5) G410 (2006). - Effects on charge trapping VFB, and ∆VFB J. Lu, J. Yan, S. Chatterjee, H. C. Kim, and Y. Kuo, “Doping of Hafnium Oxide High-K Film with Zirconium,” 2005 AVS ICMI. Tewg, Kuo, Lu, and Schueler, JJAP 151 (3), F59-F67, 2004 - Gate electrode effects Tewg, Kuo, and Lu, “Zirconium-Doped Tantalum Oxide Gate Dielectric Films Integrated with Molybdenum, Molybdenum Nitride, and Tungsten Nitride Gate Electrodes,” JECS 2005. Tewg, Kuo, and Lu, “Zirconium-Doped Tantalum Oxide Gate Dielectric Films Integrated with Molybdenum, Molybdenum Nitride, and Tungsten Nitride Gate Electrodes,” JECS 2005. Tewg, Kuo, and Lu, “Zirconium-Doped Tantalum Oxide Gate Dielectric Films Integrated with Molybdenum, Molybdenum Nitride, and Tungsten Nitride Gate Electrodes,” JECS 2005. Gate Electrode Material and Annealing Effects on ALD HfO2 S. Chatterjee, Y. Kuo, J. Lu, Microelectron. Eng. (2007). - Reliability issues - SILC Applied voltage generates traps in the oxide, which act as coulombic scattering centers and as pathways for increased local leakage currents. Figure 2: (a) Diagram illustrating log(1-[Qo(t)/Qo(0)]) as a function t for different CVS. (b)The time dependence of the current density increase observed during constant voltage stressing @ -2.5 V of 800oC PMA MoN/5nmHfO2/Si MOS. Chatterjee, Kuo, etc., “Effects of Post Metallization Annealing on the Electrical Reliability of Ultra-thin HfO2 Films with MoN and WN Gate Electrodes,” 2005 IRPS. - Time dependent current leakage t J (t ) A1 exp . (Vg ).t (5) Figure 3: Breakdown phenomena of WN/HfO2 (5 nm)/Si MOS structures during CVS –2.5 V. Chatterjee, Kuo, etc., 2005 IRPS - Hysteresis disappear due to breakdown 1.E-04 I (A) 1.E-06 after breakdown in ramp stress from -5 to -10MV/cm after a ramp stress from 0 to -5MV/cm 1.E-08 1.E-10 2nd 1.E-12 1st 1.E-14 -2 -1 fresh sample of Hf-doped TaOx+TaNy EOT=25.7A 0 V (V) 1 2 W. Luo, et al., IEEE IRW 2.1.1, 2003 - Humidity & Temperature Stresses 1.0E-05 Ta2O5 at 60% RH, 80C for 12 hr 1.0E-07 I (A) after stress 1.0E-09 1.0E-11 before stress 1.0E-13 -3 -2.5 -2 -1.5 -1 -0.5 V (V) W. Luo, et al., IEEE IRW 2.1.1, 2003 0 Wen Luo, Way Kuo, Yue Kuo, “Bayesian Approach to Reliability Projection for High k Dielectric Thin Films,” 2005 IRW proceedings. For more detailed information, please see the Publications List. Graded Gate SiNx Gate Dielectric for a-Si:H TFT Y. Kuo, JECS, 141(4), 1061, 1994. Dual SiNx/TaOx gate dielectric for TFT Y. Kuo, JECS, 139(4), 1199, 1992. Home, TFTs, Low k dielectrics, RIE, PECVD, Biochips, Laboratory, Publications, Activities, Presentations, Links