Lab 10 up down skip counter

advertisement

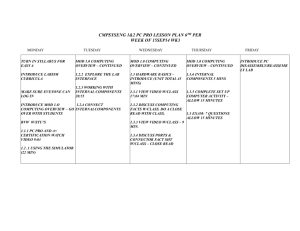

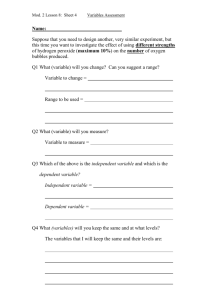

Lab 10 Design of a up/down skip counter using 74LS107 flip-flops. You may do this lab either on Thursday April 16th of April 23rd; however, the requirements are different depending on which day you complete the lab. Name: ___ Name: ________ ________________, Last digit of your VCU ID number: ______ = A ___________, Last digit of VCU ID number: ______ = B If you complete the lab on 4/16/09 follow these directions to compute Sa and Sb. 1. Convert A and B to mod 5. Sa = A mod 5 = ________, Sb = B mod 5 = ________ 2. If the Sa = Sb then for Sb use the above (Sb + 3) mod 5 = _______ 3. Design a mod 5 counter using the specifications below. If you complete the lab on 4/23/09 follow these directions to compute Sa and Sb. 1. Sa = A mod 5 = ________, Sb = B mod 5 = ________ 2. If Sa = Sb then for Sb use the above (Sb + 3) mod 10 = _______ 3. Design a mod 10 counter using the specifications below. For this lab, work with a partner. Only two people may work together. If you do not have a partner, for Sb use your Sa + 3 mod 5 or 10. No lab report is necessary, but your circuit must be successfully demonstrated, and you must turn in this sheet along with your transition diagram, transition table, Q maps, equations and an annotated Orcad schematic. Final Sa ________, Final Sb ___________, Counter modulo ___________ Using 74LS107 JK flip-flops, and any of the common gates available in lab design, implement, and demonstrate your up/down skip counter that meets the following specifications. The counter is to count either up or down in binary with the following exceptions. When counting up skip state with a binary value equal to Sa. When counting down skip the state with a binary value equal to Sb. When the machine switches mode it is possible to be in a state that would be skipped in that mode. In this case when next clocked the machine should go to the next allowed state. The mode is controlled by an input X. When X = 0 the machine counts up. When X = 1 the machine counts down. 1 All work must be neat to be accepted. Equations, maps and state table must be filled in using word. Penciled valued will not be accepted. If you do not bring correct versions of the items below to lab Thursday you may not be allowed to complete your lab on that day. 1. Complete the state transition table. 2. Draw a state transition diagram. 3. Fill in the Q maps using the maps provided. 4. Obtain the equations for J and K for each flip-flop. 5. Draw a fully annotated schematic for your design using Orcad. The above sheets must be stapled together. Signoff on the above steps: _________________________________________ Notes: Wire up and demonstrate your design. Use (Q3), Q2, Q1, and Q0 for outputs and connect these to LED’s on the CADET. Use SWT 1 for X, and use the TTL output of the CADET oscillator for the Clock. The clock input to the flip-flops respond to very fast transitions. It is important to use good fabrication techniques. Keep your wire leads short and be sure to use .01 to .1 uF bypass capacitors on all IC’s. Signoff for demonstration: ___________________________________________ State transition table. Enter Next state in each column. For mod 5 stop with state S4 and don’t use Q3 X State Q3Q2Q1Q0 0 1 S0 0000 S1 0001 S2 0010 S3 0011 S4 0100 S5 0101 S6 0110 S7 0111 S8 1000 S9 1001 2 Maps for mod 5 counter on 4/16/09. X Q2 Q0 Q1 Q2 X Q1 Q0 Q1 Q2 X Q0 Q0 Q1 Q2 3 Maps for mod 10 counter on 4/23/09. X=0 Q3 X=1 Q3 Q0 Q1 Q3 Q0 Q1 Q2 Q2 X=0 Q3 X=1 Q3 Q0 Q1 Q2 Q0 Q1 Q2 Q2 X=0 Q3 X=1 Q3 Q0 Q1 Q1 Q0 Q1 Q2 Q2 X=0 Q3 X=1 Q3 Q0 Q1 Q0 Q0 Q1 Q2 Q2 4