EE_441_Lab_Report_4

advertisement

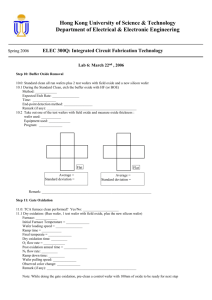

Lab Report 4 | EE 441 | Chad Ostrowski Construction Lab 1: We were given boron-doped (p-type) wafers (mine was A12) that were 2 inches across, 100 aligned, 0.0126in thick, and had 0.426 ohm-cm resistivity. We were told about the things we would do (wafer cleaning, aligning, exposing, developing, etching, growing oxide) and safety procedures that needed to accompany these processes. We learned that our yellow room was class 200 & we learned to gown up. Lab 2: We learned to clean our wafers: Bath Conditions Temp Time 1 Acetone (removes organics) 40C 10 min 2 IPA (removes acetone) 40C 10 min 3 DI (dilutes IPA) Indeterminate Rinse 4 SC1* (removes more organics & particles) 85C 10 min 5 DI (dilutes SC 1) Indeterminate Rinse 6 SC2** (removes metals & alkalies) 85C 10 min 7 DI (dilutes SC 2) Indeterminate Rinse 8 5% HF dip (removes SiO2) Room Temp To a visual end point 9 DI (dilutes HF) Indeterminate Rinse 10 IPA (replaces DI) (very pure) Room Temp Indeterminate *SC1 is a mixture of ammonium hydroxide (NH4OH), hydrogen peroxide (H2O2), and DI water (H2O). A typical concentration ratio for the mix is 1:1:5 NH4OH:H2O2:H2O, although recently ratios as low as 0.05:1:5 have been used for better cleaning performance. **SC2 is a mixture of hydrochloric acid (HCl), hydrogen peroxide (H2O2), and DI water (H2O). A typical concentration ratio for the mix is 1:1:5 HCl:H2O2:H2O. We learned about growing oxide, which was done by Euichul for us at the end of the lab, and is outlined in the diagram Basically, in order to grow a specific thickness of oxide, the wafers are put into the furnace (maintained at 800C) in an inert environment consisting of only N2 gas, which is controlled by a bubbler (discussed under Lab 4) at the back of the furnace. The temperature is raised 10C/min until it reaches, arbitrarily, 1050C and it just adjusts to this for 5 minutes. Then the chamber is evacuated of N2 by the bubbler and filled with O2 for a specific amount of time - in this case, about 120 minutes so that we could grow approximately 700nm of field oxide. The higher temperature allows for faster oxidation of the wafer.The chamber is then evacuated of O2 and refilled with N2 by the bubbler and the temperature is lowered to 800C at 20C/min. Lab 3: We did our first photolithography:: We applied photoresist: Dehydration bake 200C for at least 5 min, Put on green Nitrile gloves, Place wafer on spinner chuck, Activate spinner and blow off spinning wafer with N2 (also verify correct spin speed and time), Deactivate spinner, Apply 5-7 drops of adhesion promoter (HMDS) to the center of the wafer, Spin for about 12 seconds, Apply a puddle, covering at least half of the wafer, of photoresist to the center of the wafer, Spin at 5000 RPM for 30s (controller will turn off automatically based on specified time), and, finally, prebake 100C for 60s . Spin-on Material Concentrations: Material Constituents Concentrations Adhesion Promoter HMDS : PGMEA 60:40 Photoresist 1811 100 We exposed: My group used the Cobilt aligner named Jon, which required exposing for 5 seconds. This is how the aligners work: A photo is shown to the left. We learned that the chrome side of a mask must always go down in the aligner. Catastrophe ensues when this is ignored! We also decided (Euichul decided) that our convention would be to put the notch of the mask to the left, which means that the flat of our wafers must face right when we place them on the platform before we rotate it under the mask. We lined up the patterns to approximately the center of our wafer (since this was the first alignment it was arbitrary) and exposed. Then we hardbaked them at 125C for 3 minutes in order to harden all the photoresist that wasn't exposed. We developed: To slough off all the exposed photoresist (which was in the areas where we were going to put our sources and drains), we used a 4:1 351:DI solution for about 45 seconds. Then we checked these under the microscope for tell-tale signs of under-development/exposure (rainbows) or overexposure (blurry edges), but mine had crisp edges and just pink and white. Dr. Tadigadapa approved. We etched: Since the photoresist looked well-placed and well-developed, it was time to get rid of the field oxide in the patches where we wanted to put our sources and drains (where we got rid of the photoresist). We used HF. Since it's such a nasty chemical, we let Euichul do this. Half a class-worth of wafers were loaded onto a little boat at a time and Euichul soaked them in a 6:1 Buffered Oxide Etch (BOE), consisting of HF & NH4F. The NH4F dissociates into NH3 (ammonia) and F, keeping the solution at the proper concentration rather than letting the F level drop exponentially (hence the term "buffered"). They were all etched for 7 minutes and 41 seconds in order to erode XXXnm of oxide, which erodes at 10 to 20nm a minute in said solution. The wafers were then rinsed in acetone at 30 to 40C and then in IPA at 30 to 40C for ten minutes. Lab 4: Since our wafers were p-type, the n-type doping will need to first compensate for this p-type doping and then, in a manner of speaking, overcompensate so that it becomes n-type. The depth of the n regions down into the wafer is actually measured as the depth at which these two doping levels are the same (the background doping of the device and the new doping). In modern fabrication facilities, doping is done with ion bombardment. In the olden days that our lab is replicating, however, they did not practice such clever fabrication techniques. Instead we use a two step diffusion process in which phosphorous is first deposited onto the surface of the wafer in a controlled amount (this is called predeposition) and then these phosphorous dopant atoms are diffused (driven down) into the wafer (drive-in), an equilibrium process controlled by the solid solubility limit. The predeposition step in our lab was accomplished with liquid source phosphorous diffusion, though solid source diffusion is also possible. Liquid source diffusion is accomplished by, first of all, putting POCl3 in the bubbler and heating it to a specific temperature so that a known vapor pressure is created above it. Careful! The vapor pressure has an exponential dependence on temperature, so really tiny changes in temperature make huge changes in the amount of POCl3 gas created. After a controlled amount of POCl3 is created, wafers are loaded onto a boat in the tube furnace at an elevated temperature (we arbitrarily chose 1000C) and the inert-gas environment (nitrogen) is replaced with a mixture of oxygen and the POCl gas, which is fed into the furnace controlledly. The POCl first reacts with oxygen to form P2O5 and chlorine gas, and then the P2O5 reacts with the Si at the wafer surface to create SiO2 and P, which is just phosphorous-rich glass. This functions essentially as an infinitesimally thin layer of P, which can then controlledly deiffused into the depth of the wafer. This setup, shown below, allows for the flow of the POCl gas from the bubbler on and off to control the doping time. Figure 1: Liquid Source Phosphorous Diffusion After this diffusion layer is created, drive-in is accomplished via wet oxidation, in which the created oxide pushes the phosphorous into the bulk of the Si. Ideally we end up with a lot of n+ areas and approximately a 300nm oxide on top to insulate the diffused crossovers. We arbitrarily decided to do this at 1050C. The diagram of this process is shown in Figure 2. Figure 2: Drive-In To figure out the exact amounts of time necessary for all of these steps, working backwards through the process is the only way to go. So, knowing that the temperature used for drive-in would be 1050C, we used a program developed just for this task. It asked the wafer orientation (100), if it was wet or dry drive-in (wet), what the oxide ambient pressure was (640 torr), what temperature (1050C), and the desired oxide thickness in nm (300). It told us to run the oxidation process for 0.4568 hours, which is 27.6 minutes. Hence, the drive-in process will occur as shown in Figure 3: Figure 3: Drive-in process times & temperatures We, of course, drove in a certain amount of impurity Q that had been put on the wafer surface during the predeposition. These impurities (phosphorous, in this case) had a certain diffusivity given by D = 4.7exp(3.68/kT) which, for our chosen temperature of 1050C, gives 4.5 x 10-14cm2s-1. Knowing the diffusivity allowed us to calculate the needed Q as Cs(pi*D*t)0.5 where t is the time previously calculated by the program. This gave that we needed a Q = 4.4 x 1015 atoms/cm2. Then we determine the time spent predepositing by figuring out the diffusivity at 1000C, which gives D = 4.7 exp( -3.68/(8.617e-5*1273)) = 1.27 x 10-14 cm2s-1. This is for use in the equation Q = (2/pi)Cs(Dt)0.5. To find the solid solubility limit Cs, a chart of impurity concentration vs. temperature for various dopant atoms in silicon is consulted. We found that the solubility limit is approximately 1021. This gives t = (pi / 1.27e-14) (3.05e15 / (2*1e21) )2 = 575s = 9.59 minutes. This is summarized in Figure 4. Figure 4: Predeposition process times & temperatures Oxide was then grown again afterward, to protect the newly formed sources and drains and to allow for the distinct formation of gates. Lab 5: This lab was spent doing the same sort of lithography we did in lab 3, but this time instead of forming regions that would become sources and drains we formed regions between them that would be gates. So the process was clean with acetone and IPA, dehydration bake at 200C for at least 5 minutes, spin & blow with N2, drop on promoter HMDS, spin 12s, drop on photoresist 351, spin 30s, prebake at 100C for a minute, align, expose for the calibrated time for the specific machine used, develop in 4:1 351, hardbake at 125C for 3 minutes, etch in buffered & diluted HF solution. The etch this time took four minutes and 58 seconds. This lithography was also a bit different from the first one because the alignment wasn't arbitrary, there was a pattern down already that had to be aligned to. This took some getting used to. After the exposure and the development, a gander under the microscope showed more-or-less rectangular patterns cut through the photoresist that not only covered the areas between sources & drains, but well overlapped the sources & drains themselves. These cause capacitance in the transistors between the gate and the source & drain regions which will slow down the operation of the device. However, this is unfortunately hard to avoid when using archaic practices like hand-aligned exposure, and we fortunately will never actually use the devices we fabricate, so we're not too worried about it. Lab 6: In this lab we grew a high quality thin oxide to insulate the gate region of the transisitors. Whereas usually we're just growing field oxide, now we need a lot more precision because we're growing the gate oxide. Field oxide is just slapped on top of each process step in order to cut in new regions and eventually as an isolator between all the various interconnects, and thus the electrical properties of the field oxide are of no import. But the gate oxide is electrically crucial, being the main element in the electrical "dam" that is a Metal Oxide Semiconductor FET: the absence of a (in our case) positive charge on the metal that will be layered above the oxide needs to leave the semiconductor below P-type, a small positive charge needs to invert it to N-type and let current pass from the source to the drain. We want to make a 30-40nm thick gate oxide for our devices. Thinner oxides allow for greater conduction in the channel due to increased electric field with a unit voltage applied to the gate. In modern transistors, SiO2 oxides are approximately 1.2nm thick, but we lack the ability to grow such thin oxides with our antiquated technologies. Also, we are going to apply a larger voltage to our devices than those used in modern ICs, creating a larger electric field. We would be hard-pressed to create an oxide that was 1.2nm thick and didn't break down with such a large electric field applied. With such a thin oxide, 1V put across it will give an electric field of E=1V/(3x10 -8m) = 0.3MV/m, so we need a very good quality oxide that will not be close to breakdown when subjected to such electric fields. A characteristic of good quality oxides is that they have few impurities and many O-O bonds, called bridging bonds. As it turns out, using dry oxidation creates better quality oxides than wet oxidation. We don't want T to be less than 800C or more than 1000C; we arbitrarily choose 950C. Using equation 6.25 in the book, we find: (30nm)2/B + (30nm)/(B/A) = t B=(772um2hr-1)*exp[(-1.23eV)/(k*(950+273)K)] B/A=(6.23*106um hr-1)*exp[(-2eV)/(k*(950+273)K)] t = 30 minutes Another thing to be considered is impurities that end up in the boundary interface layer between the oxide and the semiconductor. SiO2 has a larger lattice constant than plain Si, and thus exerts a stress on Si when grown, inevitably causing a charge-sheet. This is why no good MOSFETs were made for a long time despite having the theory for the most part worked out. The impurity levels in the interface layer need to be at least around 1013-1014cm-3, getting the whole way down to zero is a violation of the second law of thermodynamics. The first step in reducing interface charges is of course cleaning the wafer with the RCA process, followed by a dip in HF because the RCA process causes some oxides to grow. Then a useful tool in the battle against metals in the interface layer is to introduce chlorine into the ambient during the oxidation process. This reacts with the metals and forms volatile gases that are removed from the chamber. We introduce this chorine using the gas trichloroethane, abbreviated TCA. This of course changes the equations above slightly, but our well-educated TA has considered these effects for us. TCA being a nervous system depressant and reacting to form various toxic gases within the furnace (including Cl2), something must be done to make sure it is removed from the furnace before cooling it back down and removing the wafers. Thus a post-anneal is done at the same temperature, 950C, with N2 pumped through for half an our to remove all but the last few stubborn atoms of TCA. Dry oxidation works by simply putting silicon in an oxygen-rich ambient and elevating the temperature, then changing the gaseous species in the ambient. We have a simple horizontal furnace in the lab in which the wafers are loaded in the front and the gases from the bubbler are pumped into the back. This is usually done between 800 and 1200 degrees Celsius. Since the silicon on the surface of the wafer is part of the reaction, 46% of the oxide ends up below the original surface of the silicon and 54% ends up above. Here's how our process went: Figure 5: Dry Oxidation for growth of Gate Oxide Lab 7: In this lab we just did another photolithography, this one opening windows to fill with a metal, so that we have interconnects. With this one the etch-in-HF-time was 9 minutes and 49 seconds. Lab 8: Before this lab, our wafers had titanium coated across the surface. This was accomplished with sputtering. Sputtering is a kind of Physical Vapor Deposition. In sputtering, the wafer is placed in a chamber which is then evacuated to pressures of about 10-6-10-7 torr opposite a large titanium source. The two are biased and a noble gas, usually argon because it's larger than helium (therefore making a better wrecking ball) but not as expensive as krypton or xenon, is flown in between them and ionizes due to the bias. This creates a high energy plasma, particles of which smash into the titanium source, essentially sand-blasting it and causing small sprays of titanium atoms which fly straight to the wafer across the chamber, due to such a long distance between collisions that occurs in such low pressures. This eventually builds up to a thin film grown anisotropically. It fills in all the vias (the windows-to-the-gates-andsources-and-drains) and covers the surface. Obviously, having everything electrically connected as it was after sputtering would be pretty useless, since we'd just have one big short circuit. So in lab 8 we did the fourth and final lithography to define where the metal should actually go. This lithography was only slightly different than the third lithography because we were etching metal instead of oxide, so the actual etch time in HF was much shorter. Mine was exactly two minutes, for instance, as opposed to the nearly ten minutes we needed for the oxide. However, this step could have been made longer if the exposure had been done for a shorter amount of time—there simply needs to be a balance between the two. See, with oxide exposure, the UV light shines through the photoresist, exposing it, and absorbs (mostly) into the SiO2 beneath the photoresist. With titanium exposure, the UV light shines through the photoresist, exposing it, then mostly bounces off the titanium beneath it, re-exposing the photoresist on the way back out. So since we exposed the photoresist over the titanium for the same amount of time as we had been exposing the photoresist over the oxide, the titanium-photoresist became much more developed. Thus, when it came time for etching (after the development and hardbake), the parts-to-be-sloughed-off were much more ready to be sloughed off, and so the etching took place over a much shorter time. If the exposure time had been shrunken, this step could have taken approximately as long as the oxide-etch, allowing for greater precision. Characterization Alignment Accuracy Shown to the left are the alignment verniers that were included on all of our chips. As seen in the image, only one pair of bars will line up from the top and the bottom. There were two of these verniers laid down on each patterning, one for the x direction and one for the y direction (those were tilted 90 degrees from those shown). If the middle two lined up, then that was a perfect alignment (for that axis), if the ones immediately to the right lined up, we recorded a +1, two to the right, +2, etc. For the y axis, the convention was that those above the middle were positive. The bars mark off microns, to tell how many microns off each alignment was. Five chips were measured total, two chips up, two chips down, two to the left, and two to the right of the original chip. The results for each chip/device were: Device # 1 1st alignment 2nd alignment 3rd alignment 2 3 4 5 x 0 y 0 x 0 y 0 x 0 y 0 x 0 y 0 x 0 y 0 -1 1 -2 0 0 2 -1 3 0 -1 0 -1 1 0 -1 -1 1 0 0 -1 mean 0.33 0.00 0.33 0.00 0.33 0.33 0.00 1.00 0.00 0.67 Using the means to compute the average angle by which the alignments were off, I find that (Theta) from 2 to 3 = atan[(-.3 + .3)um/12mm] = 0 (Theta) from 4 to 5 = atan[(1 + .7)um/28mm] = 0.0035 degrees While modern devices couldn't withstand such tolerances (it's even absurd to measure microns of difference in modern devices), for our archaic standards this is pretty good. Diode I-V Measurement To the left is a drawing of the diode we measured. Yes, it was just a square. In the drawing we have, there are other little square pads at the corners of it, but that's not actually how it looked on our wafers. We just put one probe on the pad and the ground probe on the border of the chip, which is ground. These probes were tiny needles, put into place with little knobs. Along with the platform on which our wafers rested, there was also a microscope attached to the same apparatus that allowed us to see the needles as we placed them. The whole thing was attached via BNC cables to an old oscilloscope (ok, a Semiconductor Parameter Analyzer), which output tiny voltages and currents across our tiny diodes and measures the tiny currents that resulted. For mine, it gave the graphs below. The one on the left is the linear I vs. V, the right is log I vs. V. We see machine-controlled breakdown on the linear plot at the bottom left. Also, as shown, my log plot kinda went nuts. The ideality factor is given by n=(q/(kT))*1/I * dI/dVa and is plotted below vs. positive Va. The contact resistance Rs is given by the slope of linear V vs. I at higher I, which is plotted below to the right with a trendline on it. So Rs≈1.18kΩ. (That n plot looks awfully messed up, huh?) MOS-Capacitor C-V Measurement Shown to the left is the bunch of MOS capacitors we patterned so that we could measure their characteristics. We did the first measurement on the one marked "1" (the 'thin oxide' capacitor) and the second measurement just on the field oxide marked "2" (the 'thick oxide' 'capacitor'). This second 'capacitor' measurement was simply to demonstrate the fact that field oxide is insulating, and that growing gate oxides is a tricky business that requires precise control. Derivative We used an instrument that was kind of like the one used in the diode measurements (meaning it looked basically like an outdated oscilloscope), but it measured impedance instead of simply resistance. It was called HP4275A Muilti-Frequency LCR Meter. As expected, the measurement on the field oxide produced a horizontal line. That for high frequency showed the expected field-oxide-capacitance-while-in-accumulation and miniumum-when-in-inversion. The low frequency gave the expected field-oxide-capacitance-while-in-accumulation-and-while-in-inversion, as long as a light was shined on it so that more carriers were produced. From the plots, Cox = 20pF, while from theory we get that Cox=k(ox)*A/t(ox) = 3.5e-13F/cm * (100um*100um) / (30nm) = 12pF. So we have a 66% error, which is high but reasonable, considering the methods we used to piece all of this together. High Frequency response for thin oxide Low frequency response for thin oxide High Frequency response for field oxide – shows a capacitance of 4.7pF, which is higher than I expected but still an order of magnitude smaller than the gate oxide. MOSFET Characterization As shown in the image to the left, the pads used to actually connect to the devices are a bit larger than the devices themselves. The gate length refers to the (in this picture) vertical height of it, while the width refers to the distance from the source to the drain. For the MOS 1 gate, L=50um, W=10um, and hence W/L=0.2. For the MOS 2 gate, L=20um, W=10um, and hence W/L=0.5. The plots of linear ID vs. VDS and sqrt(ID) vs. VDS are shown below for both devices. MOS1 MOS2 Linear I vs. V Linear I vs. V Sqrt(I) vs. VG Sqrt(I) vs. VG The threshold voltage & mobility are both given by the plot of sqrt(ID) vs. VDS. Using the approximation that sqrt(ID)=sqrt[1/2unC(ox)*(W/L)]*(VGS - VT) in the saturation region, if the plot is extended down to the intersection with the V axis at ID=0, this is VT, while the slope will be the mobility (everything else is known). The slope is noted on the graph, slope=1/2 * un * C(ox) * W/L ==> un = 2*slope*L/W /C(ox) = 2*[.0021 || .0042]*[.2 || .5] / 2e-11 = 42Mm/s?? for MOS1 and 210Mm/s?? for MOS2, which are surprisingly different at nearly an order of magnitude apart. The mobility ought to be a constant over the whole wafer. We account for this by noting that XXX. And, we see from the extrapolation that VT is about .002V for MOS1 and also about .002V for MOS2, and we smile because they agree. Sheet Resistance and Transmission Line Measurements Below is illustrated the transmission line structure that we used to make calculations of the contact resistance, Rc, and the sheet resistance in the diffused region. The distance between pad 1 and 2 is 10um, between 2 & 3 is 40um, between 3 & 4 is 100um, and between 4 & 5 is 220um. We made plots of resistance vs. the distance between the contacts. This resistance is modeled as R=Ren*L/W+2*Rc+Rp, where Rp is the resistance of the interconnect wires and is ignored, so that the y-intercept on our graph is 2Rc, the contact resistance, and the slope of the line is Ren*L/W, where Ren is the sheet resistance, W is the transmission line diffused region width, and L is the length of the transimission lines which we're plotting against. The plot we got from this measurement is shown below: PLOT Which gives Rc=XXX and slope=Ren/W==>Ren=W*slope=XXX. Ring Oscillators The image above shows the 31-stage ring oscillator we had on each of our devices. Each had a gate length of 10um and a gate width of 50um. When various voltages were run through this oscillator, the following table of values was obtained: Voltage (V) Frequency (kHz) 4 5 6 7 8 9 440 532 600 670 725 776 10 <11 824 fail! (as short) The oscilloscope loads the circuit with an additional 1mega-ohm and 12pF. The ohmic load does nothing to change the speed of oscillation, but the capacitance does.