Inverter Tutorial with Virtuoso

advertisement

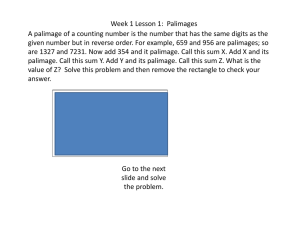

Schematic Entry with Composer 1. Creating a New Library o To create library from the CIW window (for NCSU kit): a) Select File -> New -> Library. b) Enter a library name. c) Enter the absolute path name if you want the library created somewhere other than the working directory. d) Choose the Attach to an existing techfile option. e) Choose your library; for instance, for 0.6um AMI technology, choose “AMI 0.60u C5N” f) Click OK. 2. Creating a New Schematic Cell View o In the CIW window: a) Select File -> New -> Cellview. b) Choose the library under which you would like to create the new cell view. c) Enter a cell view name. d) Choose Composer - Schematic as the Tool. View name should be schematic. e) Click OK. A blank composer - schematic window should open. 3. Creating Logic: o Switch-Level a) Create instance of nmos or pmos from the analogLib library. 1. Select Add -> Instance or use the toolbar. 2. Choose devices from NCSU_Analog_Parts for the NCSU kit. Use the Browse button in the Add Instance Form to choose a symbol view of a CMOS device. 3. Enter values for device parameters in the Add Instance Form. Model Name: from NCSU_Analog_Parts for the NCSU kit, N_Transistors (or P_Transistors) -> nmos4 (or pmos4) in the component browser; note that for NCSU kit, singleclick (not double-click) in the component browser window chooses the device, and also, VDD and ground connections Inverter Tutorial Using Cadence Tools 1 are also available under "supply nets" category in the component browser. b) Add wire to source of nmos/pmos c) Add pins for inputs and outputs. 4. Select Add -> Pin or use the toolbar. 5. Enter pin name(s) (You can enter several names at once). 6. Choose appropriate direction: Input or Output or InputOutput (bidirectional). 7. Place pin in the schematic. 8. Click Cancel when done placing pin(s). d) Add wires to connect gates and pins: Add -> Wire or use the toolbar. 4. Change Properties Using CDF: Select the Component for which you want to change the properties, then select Edit -> Properties (or use shortcut key “q”), change the properties: Width: Your chosen width (example: 1.5 µm, or as necessary) Length: Your chosen length. (example: 1.5 µm, or as necessary) 5. Use Check and Save to save design. Select Design -> Check and Save or use the toolbar. Errors will be displayed in the CIW. Correct any errors. Inverter Tutorial with Virtuoso Creating a New Cellview: o Create a new cellview under an existing library. See “Schematic Entry with Composer” to find out how to create a new library. In the Command Interface Window (CIW): a) Select File -> New -> Cellview. b) Choose the library under which you would like to create the new cell view. c) Enter Cell Name: My_Inv (for the tutorial) d) Choose Virtuoso as the Tool. View name should be layout. e) Click OK. A blank virtuoso window should open. Setting Display Parameters: Inverter Tutorial Using Cadence Tools 2 a) Select Design -> Options -> Display. b) Set the following options: 1. Pin names: On 2. X Snap Spacing: 0.03 3. Y Snap Spacing: 0.03 4. Minor Spacing: 0.03 5. Major Spacing: 0.03 6. Display levels: 7. From: 0 8. To: 20 Click "Save To" to set them permanently. Layout an Inverter: The inverter consists of three parts -- p-transistor, n-transistor, and connections. o Layout of N-transistor with L=6 λ and W=6 λ. In this tutorial, we are using the Nwell process. Thus, the substrate will be psubstrate. Draw the active a) Select the active layer from the LSW window b) Select the Create->Rectangle (or choose the Rectangle icon from the side toolbar). c) Using your mouse, draw the active on the cellview to be 12 λ long by 6 λ wide. (you can use the Edit->move command to move the layer) Draw Poly a) Select the poly layer from the LSW window b) Select the Create->Rectangle (or choose the Rectangle icon from the side toolbar). c) Using your mouse, draw the poly on the cellview to be 6 λ long by 12 λ wide. The poly should be placed at the x-center of the active Draw Source/Drain contacts 1. Draw a contact layer to be 2 λ long by 2 λ wide and place it directly over the active layer. 2. Draw a Metal 1 layer to be 4 λ long by 4 λ wide and place it directly in the center of the contact Layer. Inverter Tutorial Using Cadence Tools 3 So, far you have drawn one diffusion contact. Draw a second diffusion contact (repeat a & b). The two contacts should be placed at both sides of the active. Draw the n-select region a) Select the n-select layer from the LSW window b) Select the Create->Rectangle (or choose the Rectangle icon from the side toolbar). c) Using your mouse, draw the n-select on the cellview to be 14 λ long by 8 λ wide (Extends active by 2 λ on all sides). o Layout of P-transistor with L=6 λ and W=6 λ. Draw the active a) Select the active layer from the LSW window b) Select the Create->Rectangle (or choose the Rectangle icon from the side toolbar). c) Using your mouse, draw the active on the cellview to be λ long by 6 λ wide. Draw Poly a) Select the poly layer from the LSW window b) Select the Create->Rectangle (or choose the Rectangle icon from the side toolbar). c) Using your mouse, draw the poly on the cellview to be 6 λ long by 12 λ wide. The poly should be placed at the x-center of the active. Draw Source/Drain contacts a) Draw a contact layer to be 2 λ long by 2 λ wide and place it directly over the active layer. b) Draw a Metal 1 layer to be 4 λ long by 4 λ wide and place it directly in the center of the contact Layer. So, far you have drawn one diffusion contact. Draw a second diffusion contact (repeat a & b). The two contacts should be placed at both sides of the active. Draw the p-select region a) Select the p-select layer from the LSW window b) Select the Create->Rectangle (or choose the Rectangle icon Inverter Tutorial Using Cadence Tools 4 from the side toolbar). c) Using your mouse, draw the p-plus on the cellview to be 14 λ long by 8 λ wide (Extends active by 2 λ on all sides). The p-plus should be placed within the n-well. (you can use the Edit->move command to move the layer) o Draw the well a) Select the n-well layer from the LSW window b) Select the Create->Rectangle (or choose the Rectangle icon from the side toolbar). c) Using your mouse, draw the n-well on the cellview to be 16 λ long by 10 λ wide (Extends p-select by 2 λ on all sides). Layout necessary connections Connecting the output 1. Select the Metal1 layer from the LSW window 2. Select the Create->Rectangle (or choose the Rectangle icon from the side toolbar). 3. Draw a Metal1 rectangle between NMOS and PMOS drain region contacts. Connecting the Input a) Select the poly layer from the LSW window b) Select the Create->Path. The path options box will pop up. In the path mode you can draw lines (or paths) with the selected layer. The width of the drawn line can be adjusted, the default is the minimum width of the selected layer. c) Start path d) Double click to finish path Making the Metal1 connection for the input a) Starting from the poly line connecting the gates, start drawing a horizontal poly path b) On the Path Options dialog box, click on Change To Layer and switch to Metal1 c) Finish the path Note: By default, only the current layer of hierarchy is visible. Objects that you include as instances will be shown as boxes corresponding to their size. You can press SHIFT-F to see all levels of hierarchy. CTRL-F will return you to viewing only a single layer of hierarchy. Inverter Tutorial Using Cadence Tools 5 Power Rails a) Draw the Power Rail in Metal-1 above the PMOS b) Draw the Ground Rail in Metal-1 below the NMOS Draw the Substrate-contact(Method 1) a) Select the p-Select layer from the LSW window b) Select the Create->Rectangle (or choose the Rectangle icon from the side toolbar). c) Using your mouse, draw the p-island on the cellview next to the N-Transistor d) Add a diffusion contact (see previous step -- Draw Source/Drain contacts) in the center of the substrate-contact island. e) Connect the Metal1 to Ground Rail covering the entire substrate contact. Draw the Substrate-contact(Method 2): Using Instance a) Select Create -> Instance option from the menu Create b) In the invoked GUI, Select Library as Tutorial or the technology library and choose Cell/View as NTAP/symbolic. c) Move the instance to the desired location(in front of PTransistor). d) Place the Instance. e) Connect the Metal1 to Ground Rail covering the entire substrate contact. o Design Rule Check (DRC) DRC is used to check that all process-specific design rules (such as spacing) have been met 1. Choose Verify -> DRC from the menu. The Verify DRC form will appear. 2. Set the Switch Names field. This switch name depends on the process you're running. o Leave as default. 3. Click OK to run DRC. o If your design has violated any design rules, DRC will reports the errors in the CIW. o Errors are indicated by the markers (white color) on the circuit. o You may then proceed to correcting the errors according to the design rules Inverter Tutorial Using Cadence Tools 6 LVS (Layout-Versus-Schematic) with Virtuoso Following steps should be followed for running LVS: Check and Save your design (schematic): a) Click on the first icon to the left of the schematic (it is the icon with a box and a check mark). You will be warned if you have any floating wires or pins. You can also perform the same function by typing X or selecting Check and Save from the Design menu of the schematic window. Make sure you select Check and Save, not just Save. From the Command Interface Window (CIW): a) Select File -> Open. b) A new window appears. Set the following items, and Click OK. Library Name: my_lib Cell Name: My_Inv View Name: layout A Virtuoso window shows the layout of a Inverter. Select Verify -> Extract. o An extractor window appears. Click OK and watch any errors in CIW. It extracts a netlist from the layout, and creates a new view name "extracted." Open the inverter with view name "extracted". (Click Design -> Load ...) A new window appears. Set the following items, and click OK. o o o Library Name: my_lib Cell Name: My_inv View Name: extracted A Virtuoso windows shows the extracted view of the Inverter. Select Verify -> LVS ... A new window appears. Set the following items under Schematic, and click "RUN." It takes for a while. o o o o Library Name: my_lib Cell Name: My_inv View Name: schematic Run Directory: LVS Inverter Tutorial Using Cadence Tools 7 To see if the job is still running, you can click on the Job Monitor... button and a pop up menu will appear. After a while, a pop up menu will appear notifying you of the successful completion or failure of the LVS job. Click OK. In the LVS window, click "Output" to get the information regarding the lvs run. If the netlist doesn't match, click" Error Display" to find out the error. Useful Links: http://vlsi.wpi.edu/cds http://www.tec.ufl.edu/~wre/EEL5322/CadenceStartNew.html Inverter Tutorial Using Cadence Tools 8