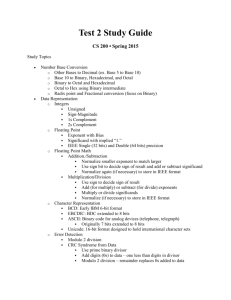

Chapter 4 - Southeastern Louisiana University

C HAPTER 4

C OMBINATIONAL L OGIC

Introduction

A combinational circuit consists of input variables, logic gates, and output variables.

The logic gates accept signals from the inputs and generate signals from the outputs.

Both input and output data are represented by binary signals.

For n inputs variables, there are 2 n possible combinations of binary input values.

Since a variable in a Boolean expression may appear primed or unprimed, it is necessary to provide an inverter for each literal not available in the wire.

An input variable may appear in two wires, supplying normal and complement forms to the input of the circuit.

Design Procedure

The procedure involves the following steps:

1. The problem is stated.

2. The number of available input variables and required output variables is determined.

3. The input and output variables are assigned letter symbols.

4. The truth table that defines the required relationships between inputs and outputs is derived.

5. The simplified Boolean function for each output is obtained.

6. The logic diagram is drawn.

Adders

The simple addition consists of four possible elementary operations o 0 + 0 = 0, 0 + 1 = 1, 1 + 0 = 1, 1 + 1 = 10.

-

The last operation sum’s length is 2. The higher significant digit is called carry . The carry obtained from two bits is added to the next higher-order pair of significant bits.

A combinational circuit that performs the addition of two bits is called half-adder .

One that performs the addition of three bits (two significant and a carry) is full-adder .

Half-Adders

Symbols x , y are two inputs and S (sum) and C (carry) for outputs.

We now generate the truth table x y C S

0

0

1

1

0

1

0

1

0

0

0

1

0

1

1

0

The S output represents the least significant bit of the sum.

The simplified sum of products expressions are:

S = x’ y + x y’ when S = 1

C = x y when C = 1

Figure 4 –2 Page 118 shows the half-adders.

The half-adder can be implemented with an exclusive-OR and an AND gate as shown in Figure 4

– 2(e).

Full-Adders

A full-adder is a combinational circuit that forms the arithmetic sum of three input bits. It consists of three inputs and two outputs.

Inputs x and y are the 2 significant bits to be added. Input z represents the carry from the previous lower significant position.

Two outputs are necessary because the sum of three binaries range from 0 to 3, which in return needs to digits. x

0

0

S (sum) and C (carry) for outputs.

The truth table is: y z C S

0

0

0

1

0

0

0

1

1

1

1

0

0

1

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

1

1

0

1

0

0

1

-

When all bits are 0’s, the output is 0.

S is equal to 1 when all three inputs are 1s or when only one input is 1.

C has a carry of 1 when 2 or three inputs are equal to 1.

Two different interpretations are given to the values of the bits encountered in this circuit.

The I/O logical relationship of the full-adder circuit may be expressed in two Boolean functions, one for each input variable.

Each output Boolean function requires a unique map for its simplification.

Each map must have 8 squares 2 3 .

The 1s in the squares for S and C are determined directly from the truth table.

S = x’y’z + x’yz’ + xy’z’ + xyz

C = xy + xz + yz

Figure 4

– 3 Page 120 shows maps for full adders.

Figure 4

– 5 shows the full-adder with two half-adders and an OR gate.

Subtractors

Is accomplished by taking the complement of the subtrahend and adding it to the minuend.

Half-Subtractors

It is a combinational circuit that subtracts two bits and produces their difference.

The minuend is x and the subtrahend is y .

If x ≥ y, we have three possibilities:

1. 0 – 0 = 0

2. 1

– 0 = 1

3. 1 – 1 = 0

The result is called the difference bit .

If x < y, we have

1. 0 – 1 and we need to borrow a 1 from the next higher stage.

2. The 1 borrowed from the next higher stage adds 2 to the minuend bit.

3. If the minuend equals to 2, the difference becomes 2

– 1 = 1.

The half-subtractors needs two outputs:

1. D , which generates the difference.

2. B for borrow, generates signal that informs the next stage that a 1 has been borrowed.

The truth table for the input-output relationship of a half-subtractor can now be derived as follows:

x y B

0

0

1

0

1

0

0

1

0

1 1

D = x’ y + x y’

0

B = x’ y

D

0

1

1

0

Analysis Procedure

- A Logic Diagram (circuit diagram) can be culminated from a set of Boolean functions

1

1

1

1

0

0

0

A

0 or a truth table.

- Ex: 4

– 9 Page 128 shows the Logic diagram for analysis example.

Truth table for the Logic Diagram of Fig. 4 – 9

B C AB AC BC T

2

T

1

F

2

F

2

’ abc a+b+c t

4

= ab+ac+bc T

4

’

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

1

1

0

0

0

0

0

1

0

1

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

0

1

1

1

1

1

1

1

0

0

0

1

0

1

1

1

1

1

1

0

1

0

0

0

T

3

F

1

T

1

+ T

4

’ T

2

+T

3

0

1

1

0

1

0

0

0

0

1

1

0

1

0

0

1

Multilevel NAND Circuits

- The NAND gate is a universal gate because any digital system can be implemented with it.

- Figure 4 – 10 shows the implementation of NOT, AND, and OR by NAND gates.

1

1

1

1

0

0

0

0

0

0

0

1

1

1

1

Derivation of the Truth Table

- Ex: Figure 4 – 14 Analysis example.

Truth table for the Logic Diagram of Fig. 4

– 9

A

0

B

0

C

0

D

0

(B’)’ A’

0 1

T

1

T

2

T

3

( CD)’ (BC’)’ (T

1

T

4

B’)’ (T

3

F

A)’ (T

2

T

4

)’

1 1 0 1 0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

0

1

1

1

0

1

1

1

0

1

1

1

0

1

1

1

0

0

1

1

1

1

1

1

0

0

1

1

0

0

1

1

1

1

1

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

1

1

1

1

1

AB CD

00 01

00

01

A 11

1

1

1

1

F = AB + BC’ + ACD

A 10

D

Parity Generators and Parity Checking

C

11

1

1

D

C

10

1

B

B

A parity bit is used for the purpose of detecting errors during transmission of binary information.

It is an extra bit to make the numbers of 1s either odd or even.

The message, including the parity bit, is transmitted and then checked at the receiving end for errors.

-

An error is detected if the checked parity doesn’t correspond with the one transmitted.

That circuit that generates the parity bit in the transmitter is called a parity generator.

That circuit that generates the parity bit in the receiver is called a parity checker.

The following truth shows the Even-Parity-Generator Table:

1

1

1

1

1

0

1

1

1

0

1

1 x

0

Three-bit Message y z

0

0

0

0

0

1

1

1

0

0

0

1

0

1

Parity Bit

P

0

1

1

0

1

0

1

1

1

1

0

1

0

1

An error occurs during transmission if the four bits received have an odd number of

0

0

0

0

0

0 x

0

1s, indicating that one bit has changed in value during transmission.

The output of the parity checker, denoted by C , will be equal to 1 if an error occurs, i.e., if the four bits received have an odd number of 1s.

The following is Even-Parity-Checker Table:

Four bits Received Parity Bit y z p C

1

1

1

0

0

0

0

0

0

1

0

0

1

1

0

1

0

0

1

0

1

1

0

0

0

1

1

0

0

1

1

1

1

1

0

0

0

1

0

0

1

1

1

0

0

1

1

0

1

0

1

1

0

1

0

1

0

1

1

0

1

1

0

0