CBT VLSI Design Project Lab 2 DA Logic Schematics

advertisement

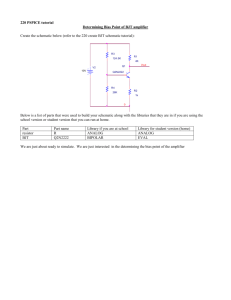

Lab Guide 4 – Digital Schematics Computer-based project in VLSI Design Computer-Based Project on VLSI Design Co 3/6 Laboratory Guide 4 – Digital schematics with Design Architect This laboratory guide provides further experience in the use of the Mentor Graphics Design Architect package, emphasising its value for digital schematic capture and symbol creation. In this session you will create a schematic specification and a symbol corresponding to the ring oscillator element, ring_oscillator. You will then be able to use a similar approach to develop the remaining parts of the design (relating to the programmable frequency synthesiser). Finally, you will create a component, named top_level, in which all the elements of the target design are embodied. When you complete the session, you should have a complete schematic representation for the programmable divider unit, which includes the ring oscillator design and all its supporting elements. Before you commence work with Design Architect, it is necessary to give some thought at this point to the form of the schematic sheet for the ring_oscillator module. This may usefully be done off-line, away from the workstation. Review the results of Lab Session 2, and, if necessary, consult the Ring Oscillator Specification pamphlet, which describes the system requirements for the ring oscillator. Then draw a rough sketch of your proposed schematic. Although the appearance of the schematic has no bearing on the functionality of the entity it represents, a neat and regular diagram clearly contributes to the process of understanding its operation. Show your plan to a demonstrator before you enter it into Design Architect. Once this paper design is complete, you should log in at a workstation and start up Design Manager, as described in the Getting Started pamphlet. 1. Start Design Architect. Select the design_arch icon in the Tools window, and either double click it, or give the command: (menu bar) Object > Open. Iconise Design Manager. When the Design Architect window appears, drag and resize it to a convenient format. Note the availability of (menu bar) commands, soft keys (listed at the foot of the screen), and command palette (column at right). 2. Open the supplied sheet for the top_level design, by clicking on the OPEN SHEET button in the palette window. The Open Sheet dialogue box appears. Fill in the Component Name box with: $CBT_WD/top_level. Leave the sheet name as sheet1 and OK the dialogue box. A new Edit window appears, containing the sheet, which is an incomplete version of the target design. Spend a few moments examining the contents. You should see: Input pads (column at left hand side) Output pads (column at right hand side) Power and ground pads (top) Input and output pads provide a means of making a physical connection (i.e. with wires or printed circuits) to the on-chip circuitry. Power and ground pads have pre-defined functions in terms of providing supply current, and certain input pads and output pads have already been assigned to functions; in each case, the yellow NET property indicates the name anticipated for the signal. Designers are at liberty to change these, by editing the corresponding property – see below – but this will need to be taken into account in later sections. A few pads have not been D M Holburn Apr 2007 EN2002 83 C6lab4.doc Lab Guide 4 – Digital Schematics Computer-based project in VLSI Design allocated (their NET property name is still the default: Net); it will be up to each design group to determine a suitable allocation of those pads to the remaining input and output signals. Note: The physical sites of the pad cells have been pre-determined (through the Place property) – for example, L1 – to avoid problems at the layout stage. You should avoid editing the properties of these components indiscriminately. Ask a demonstrator if you cannot identify these items, or if you have a question. 3. Refer to the block diagram Figure 1 (page 29), which depicts the logic modules required by the design, and lists the signal inputs and outputs that are needed. You will see that certain key items are omitted from the schematic sheet for the top_level design, including the counter, the shift register, the ring oscillator module, and certain other gates. Nor is there any indication of how the modules are to be connected. These deficiencies will be remedied during the course of this session. 4. Find the Mietec library components. At this stage, the 2 input NOR gate to be used is a primitive component contained in a large library of components supplied by Mietec Alcatel. Each item in the library has a characteristic graphic symbol, and an assortment of properties, which specify its various electrical and other characteristics. The library is held in a collection of design files and directories in a fixed place in the Mentor filespace, and is accessible to any designer for reading, but cannot be changed. Later in this project, we shall substitute in place of this library item a NOR gate of our own design and with properties which we shall determine through a detailed modelling procedure. Give the command (menu bar) Libraries > Mietec Library. The palette should now show CMOS24, the product name given by Mietec to this library (which is built using CMOS technology with transistors of gate length 2.4 m). Click on: CMOS24 > Digital Cells > Core Cells > Simple Gates. If necessary, enable scroll bars on the resulting palette menu by using the menu item Show Scroll Bars available on the right mouse button. Before proceeding, note that you can ascend through the sequence of library menus by using the (pull down) Back menu item, accessed with the right mouse button (Menu). Using this facility, investigate the library menus and explore the variety of gates provided in the Mietec library. Ask a demonstrator for details of any gates whose purpose is not clear. When ready, return to Simple Gates. 5. Place a 2 input NOR gate. Click on NOR2. The ADD INstance prompt bar appears at the foot of the screen with the At Location box highlighted in red. Move the cursor onto the sheet; a ghostly image of a NOR2 will follow the cursor. Click to drop the component in a suitable location, somewhere near the bottom of the sheet. Note the Active Symbol window now shows a NOR2 symbol. To place a further NOR2 you can click in the Active Symbol window, then position the ghostly image as above. You can reposition the symbol once placed by clicking it to select it, then depressing the Alt key followed by the middle mouse button. You will need to use these procedures again when creating the ring_oscillator schematic discussed later. D M Holburn Apr 2007 EN2002 84 C6lab4.doc Lab Guide 4 – Digital Schematics Computer-based project in VLSI Design 6. Wire up the NOR gate The inputs and outputs of the NOR gate are to be connected (via input or output pads) direct to external pins. The input and output pads (library components) have already been placed on the sheet. Each is connected to a pin element described as a portin or a portout, as appropriate, signifying an external connection to the system. Each has a property NET, which needs to be assigned an unambiguous symbolic name for the benefit of downstream simulation tools. Examine the schematic and determine convenient pins for the NOR gate. Unselect all by pressing function key F2. Give the command: (menu bar) Libraries > Display Schematic Palette. With the ADD/ROUTE palette displayed, click the Add Wire icon. If you prefer, you can instead use (Pulldown) ADD > Wire, or press function key F3 to begin wiring. The ADD WIre prompt bar and a wiring cursor (cross) will appear. To connect two points, click on the first point, click on any intermediate points, and double click on the last point to finish the wire. The ADD WIre prompt bar remains until cancelled; the next wire can then be placed immediately without the need to issue the Add Wire command again. If you are not satisfied with the appearance of you hand-drawn wires, you can delete them and try again. Alternatively, with the wires selected (left click), you can use the ROUte SELected command in the ADD/ROUTE palette to snap them to the internal grid. 7. Change the NET property You must now change the NET property for the newly wired pins, as described, to represent appropriate external names. The suggested names are A, B and NOR. You can if you wish use names of your own choosing, but if you do so you must be prepared to substitute the appropriate names in all later parts of the session. To do this, first unselect all. Give the command: (Menu bar) Edit > Edit Commands > Properties > Change Text Values. A Change Text Values dialogue box appears, showing a single text box. Enter A in this box, and a further box will appear. Use the mouse to get to it and enter B. Enter NOR in a similar way. OK the dialogue box. A sequence of messages (in the message area) and prompt bars will then appear asking you to position the items of text. Click on the appropriate instance of NET to change the property. Repeat this for the two remaining pins. You can use the same procedure if you wish to change the NET properties assigned to any of the other pins. 8. Save the work done so far It is wise before proceeding to save the work done so far. Design Architect encourages the designer to perform a number of elementary checks on the schematic before it is saved. Although at this stage the design, being incomplete, will generate a number of warning messages, we shall execute the check nonetheless. Give the command: (Menu bar) Check > Sheet > With Defaults. A window will appear, reporting the results. There should be no errors. You can safely ignore the warning about unconnected pins, as these will be resolved later. Ask a demonstrator if you encounter errors or unexpected warnings. Close the report window. Give the command: (Menu bar) File > Save Sheet > Default Registration to save the part-completed sheet. Repeat this procedure at any time to save your work. D M Holburn Apr 2007 EN2002 85 C6lab4.doc Lab Guide 4 – Digital Schematics Computer-based project in VLSI Design 9. Place a counter component on the sheet. The counter is provided in your design directory under the name 4bit_counter. This is not itself a library component, but is a hierarchical element, itself consisting of a set of primitive library parts. In contrast with the NOR2 part, it can be explored and edited in just the same way as the top_level schematic you are currently editing. You will later have an opportunity to make a minor modification to the 4bit_counter schematic using Design Architect. Since the counter is not actually a part of the Mietec library, a different procedure has to be adopted to incorporate it. Give the command: (menu bar) Libraries > Display Schematic Palette. Click the Choose Symbol icon in the palette. Note: depending on the size of the Design Architect window, you may need to enable scroll bars to see this icon. A Navigator dialogue box opens. Select the 4bit_counter component, and OK the dialogue box. Position the ghostly image that appears in an appropriate site and drop it by clicking. OK the ADD INstance prompt bar. 10. Wire up the counter Use the wiring technique described above to link all four outputs of the counter and its RB input to suitable pins. Edit the NET property of each associated pin to an appropriate name (see the block diagram in figure 1). Check the sheet and save. 11. Try to add the ring_oscillator block. At this stage it is necessary to add the ring_oscillator block, representing the ring oscillator module. Note that ring_oscillator is not in the Mietec library, nor is it provided in your working directory. Verify this by using the Add instance procedure just described, and cancel the dialogue box when ready. You will therefore have to create a symbol by which to represent the ring oscillator, and define its content in terms of library elements (2 input NOR gates NOR2). Both these operations can be accomplished using Design Architect. As stated before, we shall later substitute a 2 input NOR gate of our own design. 12. Compose the ring_oscillator schematic For convenience, we shall first create the ring_oscillator schematic, to define its content in terms of logic gates. We shall then create a symbol, also named ring_oscillator, to represent the ring_oscillator entity within the top-level schematic top_level. Mentor keeps these separate but related design entities in a container (actually a sub-directory) so that they may be accessed conveniently. Give the command: (Menu bar) Libraries > Display Schematic Palette. Click the Session icon in the palette; the title bar of the top_level daughter window will grey as that window is temporarily de-activated. Click on Open Sheet in the palette. When the dialogue box appears, fill in the name ring_oscillator, leave the sheet name as sheet1, and OK the dialogue. A new sheet appears (overlaying the inactive top_level sheet). 13. Enter the ring_oscillator schematic You should by now have given consideration to the form of the schematic for the ring_oscillator module. If not, review the material at the start of this sheet, and carry out this part of the design, away from the workstation. D M Holburn Apr 2007 EN2002 86 C6lab4.doc Lab Guide 4 – Digital Schematics Computer-based project in VLSI Design 14. Place and wire the necessary primitive gates You will need to place a number of primitive gates from the Mietec library and wire these together. The detailed instructions for doing this will not be repeated here. Carry out these operations using the placing and wiring techniques practised earlier. Be sure to check and save your work from time to time. 15. Place portin and portout elements On this occasion, you will also need to place portin and portout elements which allow the input and output signals from the module to be made available in the ring schematic sheet. These are provided in the CMOS24 library, under: CMOS24 > Digital Cells > Schematic. Note that input and output pads are not required in this part of the design, since these are provided in the higher-level schematic sheet top_level. This is an important consequence of the hierarchical approach we have chosen for the design process. Place and wire the portin and portout elements just as you did the NOR2 cell, and edit the NET property on each to an appropriate name (see Figure 1). Check the sheet. Once it is complete, there should be no errors and no warnings. When you are satisfied, save the ring_oscillator sheet, but do not close the schematic window just yet. 16. Generate a symbol for ring_oscillator In order to represent ring_oscillator within the top_level schematic, we require a suitable symbol. In the hierarchical design process, the symbol serves to conceal the complexity of the underlying logic and provides a clean and well-understood interface to other symbols. We shall use Design Architect's inbuilt facility for generating a symbol from an existing schematic. Give the command: (menu bar) Miscellaneous > Generate Symbol. Observe the Generate Symbol dialogue box which appears, but do not change anything. OK the dialogue box. A new symbol editing window should appear showing an automatically generated symbol for the ring_oscillator component, with pins matching the input and output ports on the schematic sheet. Give the command: (menu bar) Check > With Defaults. There should be no errors, but you may observe some benign warnings appertaining to the symbol's interface. Close the results window, and save the symbol using the command: (menu bar) File > Save Symbol > Default Registration. This operation also registers the interface exposed by the symbol so it can be reconciled with any schematic in which it appears. Note that if you now repeat the check operation carried out prior to saving, it generates no warnings, indicating that the saved copy is correctly prepared. Close the symbol editing window, and resume editing the top_level schematic. 17. Place and wire an instance of ring_oscillator Now that a symbol and schematic have been prepared for ring_oscillator, it is possible to wire up that component. Using the procedure you adopted for the 4bit_counter component, place an instance of the ring_oscillator component in a convenient position. Wire up its pins appropriately, and edit any NET properties that remain to be changed. Check and save the schematic. D M Holburn Apr 2007 EN2002 87 C6lab4.doc Lab Guide 4 – Digital Schematics Computer-based project in VLSI Design 18. Simulate the basic design using QuickSimII At this point we recommend you switch to Lab Guide 5, and familiarise yourself with the general techniques needed for simulating the target design using the cmos24 digital cell library. This resembles the approach used in Lab 2, in which a basic design comprising the ring oscillator and a 4-bit counter was modelled in order to gain familiarity with the ModelSim VHDL environment. It may be convenient to make use of time outside the scheduled sessions to plan the more elaborate programmable counter design, which will comprise more than one counter element, a comparator, and control logic. You will need to make a number of design choices and research the availability of suitable cmos24 library cells, details of which can be seen via the CamTools VLSI web board. Once you have successfully accomplished this, you should return to Design Architect to complete entry of the schematic form of the synthesiser design. Several more components are required in order to complete the design as specified, representing the programmable counter stages, comparator and control logic. However, you are recommended to retain the basic experimental design just used for QuickSimII modelling. Use the Save Sheet As… command to save it under a different name – for example top_level_4bit – and resume your development using the top_level schematic cell. 19. Place and wire other instances as needed Several more components are required in order to complete the design as specified. Although there are many possible ways of completing the design, we strongly encourage you to use a hierarchical approach, creating schematics and symbols as you proceed, and use a consistent naming structure. We recommend you use the following names, or derivatives of them: divider and comparator, and control, although it is perfectly possible to change these. The notes below and in subsequent Lab Guides assume that a naming structure of this form has been used. If you wish to use different names, you must be prepared to substitute in place of those given the names you have actually used in your design. For the programmable divider, counters of 6 to 10 bits will be required. This is not supplied in a ready-to-use form, and you will need to find a way to implement it. One approach might be to use 4bit_counter as a model, and craft a schematic to provide n-bit counters, as selected for the target design. Another, possibly quicker, though less elegant approach, will be to craft larger counters using instances of the 4bit_counter cell, which is freely available in your cbt directory. A comparator element is also required. This would commonly be implemented using exclusive-OR or exclusive-NOR gates. Gates exor and exnor are the corresponding Mietec digital library cells. Certain other combinational and sequential gates may also be required to fulfil the final specification. Consult the CamTools VLSI web board for a summary of the library contents. Using the procedure described in paragraphs 12 - 16, place the necessary instances, save the various schematic sub-cells, create symbols, and load any necessary instances into top_level. Wire up the pins of the new instances, and edit any NET properties that remain to be changed. Check and save the schematic. D M Holburn Apr 2007 EN2002 88 C6lab4.doc Lab Guide 4 – Digital Schematics Computer-based project in VLSI Design 20. Gather material for the Second Interim Report. Your report should include schematic diagrams and other design information, as well as answers to exercises contained in the Lab Sheets and elsewhere. You should also list the primitive cells used by your design, and indicate the function of each. To assure yourself of this information, you may need to open the 4bit_counter and other schematics in Design Architect to get a view of the primitive cells each one contains. If you do this, be sure not to make any inadvertent changes to the schematic - i.e. do not save it at this stage. You can alternatively use Design Manager to list the cells by selecting either component and giving the command: (menu bar) Report > Hierarchy. You may wish to generate printouts of the schematics and symbols created so far for inclusion in your Second Interim Report. The procedure is described below. 21. Predict the expected performance of the design Study the block diagram and specification of the top_level design (Figure 1). Consider the specifications and schematics for the main modules of the design, viz. divider, comparator and control. Referring as necessary to the results of your VHDL simulations in Lab 2, sketch the waveforms you expect to see at each of the outputs of the design. Include these results in your Second Interim Report, but keep a copy. You will find this information useful in later phases of the design to compare against the results of numerical modelling, and hence for verifying correct operation of your design. Printing out schematics or symbols First review the material in the Getting Started document on Generating Hardcopy, which introduces some general concepts. In order to set up Design Architect for printing, give the command: (menu bar) MGC > Setup > Printer. When the Setup Printer dialogue appears, enter the Printer name in the corresponding text box. Normally this will be mgcps_a4. Leave the number of copies set at 1 - the utility mgcplot will provide a means for printing a copy for each team member. Check that the Object Type is set to Design, and that Scale is set to Fill Page. Orientation should be set to Best Fit; you may ignore the Panel Name box and the Priority and Notification settings. OK the dialogue. In order to print the sheet, give the command (menu bar) File > Print Sheet: (or Print Symbol:, as appropriate). When the Print Object prompt bar appears, verify that it contains the correct printer name, and correct if necessary. OK the prompt bar. A status message should confirm that operation has been successful. The final stage of printing requires the use of mgcplot. Open a new X terminal window, and when the Unix prompt appears, give the command: mgcplot. For the moment, press Enter when asked if you wish to process colour or A3 plots. Examine the list of output files you have so far generated, and select one by number. Mgcplot will now prompt you with a numbered list of output possibilities, including a Preview to Screen. You are recommended to use this to verify the results before committing them to paper. When you are ready, exit the ghostview Preview utility, and choose a printer if appropriate. D M Holburn Apr 2007 EN2002 89 C6lab4.doc Lab Guide 4 – Digital Schematics Computer-based project in VLSI Design If you wish to include output in your interim or final report, consider the option: Save a copy in your home directory, which will place a copy of the Postscript file in your (personal) workspace. Note that it may be desirable for each team member to do this. Further processing of the Postscript files can be carried out with a range of Unix or Windows-based utlities, but this is beyond the scope of the lab guide! Note: Unless you hear to the contrary, only the A4/monochrome printing options are available. D M Holburn Apr 2007 EN2002 90 C6lab4.doc