Improved Thermal Performance of SOI Using a Compound Buried

advertisement

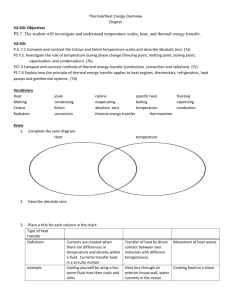

1 TED-2014-03-0322-R.R1 Improved Thermal Performance of SOI using a Compound Buried Layer Paul Baine, John H Montgomery, B. Mervyn Armstrong, Harold S. Gamble, Sarah J Harrington, Sydney Nigrin, Robin Wilson, Kean B. Oo, G. Alastair Armstrong and Suli Suder Abstract—The buried oxide layer in SOI was replaced by a compound buried layer (CBL) containing layers of SiO2, polycrystalline silicon (polysilicon) and SiO2. The un-doped polysilicon in the CBL acted as a dielectric with a higher thermal conductivity than SiO2. CBL provides a reduced thermal resistance with the same equivalent oxide thickness as a standard SiO2 buried layer. Thermal resistance was further reduced by lateral heat flow through the polysilicon. Reduction in thermal resistance by up to 68% was observed, dependent on polysilicon thickness. CBL SOI substrates were designed and manufactured to achieve a 40% reduction in thermal resistance compared to a 1.0 µm SiO2 buried oxide. Power bipolar transistors with an active silicon layer thickness of 13.5 µm manufactured on CBL SOI substrates showed a 5% - 17% reduction in thermal resistance compared to standard SOI. This reduction was dependent on transistor layout geometry. Between 65% and 90% of the heat flow from these power transistors is laterally through the thick active silicon layer. Analysis confirmed CBLSOI provided a 40% reduction in the vertical path thermal resistance. Devices employing thinner active silicon layers will achieve the greater benefit from reduction in vertical path thermal resistance offered by CBL SOI. Index Terms—Compound buried layer SOI, reduced thermal resistance in SOI, power bipolar transistors on SOI, SOI technology. I. INTRODUCTION S ILICON ON insulator (SOI) technology offers many advantages for both bipolar and MOS integrated circuits. Parasitic capacitance and process complexity are significantly reduced. However, the thermal resistance is high as the buried SiO2 layer has a low thermal conductivity ~ 1 Wm-1 K-1. This may lead to overheating and device failure in both bipolar and MOS power switching transistors and in high density CMOS integrated circuits. SOI with the buried SiO2 layer replaced with a compound layer (CBL) consisting of an This work was co-funded by the U.K. Technology Strategy Board Collaborative Research and Development programme TP/8/ADM/6/I/Q2102J. P. Baine, J. H. Montgomery, B. M. Armstrong, H. S. Gamble, G. A. Armstrong and S. Suder are with School of Electronics, Electrical Engineering and Computer Science, Queen’s University Belfast, Belfast BT9 5AH UK (email:p.baine@qub.ac.uk) S. J. Harrington and S Nigrin are with Plessey Semiconductors Ltd (Swindon), SN5 7XE UK (email:Sydney.Nigrin@plesseysemi.com) R. Wilson is with IceMos Technology Ltd., Belfast BT17 0LT UK (email:robinwilson@icemostech.com) K. B. Oo is with Intel Technology (Malaysia), Penang, Malaysia (email:koo01@qub.ac.uk) un-doped polysilicon layer sandwiched between two thin SiO2 layers has been shown to reduce device thermal resistance [1,2]. CBL in small area vias was proposed for alignment under integrated circuit hotspots, but adds considerable complexity to the substrate technology. A patterned CBL structure applicable uniquely to LDMOS transistors resulted in enhanced breakdown voltages >700V, reduced operating temperature and slower operating speed [3]. Electro-thermal simulation has shown CBL structures offer significantly lower thermal resistance than standard SOI [4]. However, these simulations employed the thermal conductivity of single crystal silicon which is considerably higher than that of polysilicon. Full area CBL SOI has been employed in the production of high voltage bipolar transistors [5]. Thermal resistance reduction has been achieved without compromise to breakdown voltage or parasitic capacitance requirements. In this work, CBL structures have been manufactured with a range of polysilicon thicknesses. Experimentally determined thermal resistance of the CBL structures is lower than comparable SOI structures. A lateral heat flow path through the polysilicon was observed and characterized with an analytical model. Power bipolar transistors with a range of size and architectures were manufactured on a CBL substrate. Resultant thermal resistance showed a strong dependence on transistor geometry. These results have been analyzed in detail and the superior performance of the CBL SOI technology has been verified. II. THERMAL CHARACTERISATION The structure of the CBL SOI substrate is shown in Fig. 1. In this work the active silicon layer was typically 2.5m thick to suit vertical power bipolar transistor manufacture. The underlying CBL BOX consisted of a three layered structure of SiO2, un-doped polysilicon and SiO2. The substrate was manufactured by wafer bonding technology which will be described in detail in section III. The polysilicon provides higher thermal conductivity than SiO2 but its polycrystalline structure results in a reduced thermal conductivity compared to single crystal silicon. The polycrystalline structure of the material results in phonon scattering at the grain boundaries [6]. This is strongly influenced by grain size and can also be anisotropic in nature with strong dependence on microstructure features [6-12]. It is crucial to the CBL SOI substrate that the polysilicon layer is intrinsic and acts as a dielectric to contribute to capacitance reduction. Standard IC manufacturing processes have been employed in the 2 TED-2014-03-0322-R.R1 production of the polysilicon by LPCVD at 620 oC with subsequent anneals at 1050oC during thermal oxidation and at 1100oC during wafer-bond anneal. No customized deposition or anneal processes have been employed to optimize grain size or microstructure in the layer [6,7,13]. Typically quoted values for the thermal conductivity of standard un-doped polysilicon layers lie in the range 10-40 Wm-1K-1. The thermal characterization of the CBL BOX has been undertaken using substrates with a range of layer thicknesses. Thermal characterization of the CBL dielectric layer structure was undertaken using the customized Van der Pauw resistors illustrated in Fig. 2 and the novel measurement technique used for standard SOI substrates [14]. The resistors were manufactured in a 300 nm Al layer evaporated directly onto the CBL dielectric and standard SOI dielectric samples. Two contact pads are employed to provide the current drive circuit through the resistor. The voltage developed across the resistor, shown in Fig. 2 with length L, is measured between the two additional contact pads. Hence the resistance can be accurately determined. The four contact pads are spaced at long distance from the main body of the resistor to minimize any cooling effect of probes applied during measurement [1,14]. The Van der Pauw resistors employed have a spacing L of 300 m between the voltage measurement arms and a width W of 8 µm. In this work, the resistance of each resistor is accurately measured on a temperature controlled chuck at fixed temperatures in the range 30-90 C to produce a calibration graph of resistance against temperature. A low current drive of 10 µA was employed in order to avoid selfheating. Following this, the chuck is then reset to 30 C and the wafer allowed to cool before the resistor is measured again at current drives of up 100 mA. This high current drive causes the resistor to self heat and hence rise in temperature and in resistance. The attained temperature of the resistor at the high current drive (and power P) can be determined from the calibration graph. Hence it is possible to compute the thermal resistance of the substrate as the temperature rise ΔT is given by equation (1), where RTH is the substrate’s thermal resistance. ΔT = P/RTH (1) The thermal resistance can be described by equation (2). RTH = tox/Ak + RSH (2) A is the area of the resistor, tox is the oxide thickness, k is the thermal conductivity of the SiO2, and RSH is the thermal resistance of the silicon handle wafer. The test structure was initially employed to characterize conventional SOI substrates with SiO2 BOX. Oxide thicknesses in the range 300nm to 1100 nm relevant to power bipolar transistors were employed. A graph of measured thermal resistance against oxide thickness is shown in Fig. 3(a). A linear dependence is observed. The thermal conductivity of the oxide was extracted from the slope of this graph using equation (2) and yields a value 1.3 Wm-1 K-1. The intercept on the y axis is attributed to RSH the thermal resistance of the 720 µm thick silicon handle wafer under the BOX. A value of 80 K/W was obtained. The thermal conductivity of single crystal silicon is 150 Wm-1K-1. Similar measurements have been undertaken on substrates with a CBL BOX. These substrates contain a SiO 2– polysilicon–SiO2 sandwich structure. The bottom oxide thickness tox1 was varied from 120 nm to 370 nm, while the polysilicon thickness was fixed at 0.9m and the top oxide tox2 was fixed at 90 nm. The experimentally measured thermal resistance of the CBL SOI substrates (CBL1) is also shown in Fig. 3(b). These values are plotted against the total oxide thickness (tox1 + tox2) in the CBL BOX. The CBL SOI substrate has exhibited a linear increase in thermal resistance dependent on total oxide thickness. More importantly, the thermal resistance is considerably lower than an SiO2 BOX with the same total oxide thickness (tox1 + tox2). It is therefore clear that the inclusion of the polysilicon does not constitute a small additional thermal resistance in the CBL structure, but actually decreases the thermal resistance. It is therefore proposed that the polysilicon, which has considerably higher thermal conductivity than the SiO2, provides a lateral heat flow path. This heat flow will be directly via the lateral path in the polysilicon and a potential heat spreading route through the underlying oxide as illustrated in Fig. 4. This heat flow path acts in effect as a thermal shunt in parallel with the underlying bottom oxide and the silicon substrate. The proposed lumped thermal resistance model is also illustrated in the schematic diagram shown in Fig. 4. The CBL SOI data in Fig. 3(b) yields an intercept with y-axis at a value of 98 K/W. This extracts the effective residual thermal resistance with the oxide thickness reduced to zero, and is made up of the silicon handle wafer thermal resistance, RSH, plus an additional thermal resistance associated with the polysilicon layer series and shunt components. The inclusion of the polysilicon layer in the CBL BOX yields a reduction in thermal resistance of the SOI substrate while also reducing its parasitic capacitance. This can be illustrated by plotting the thermal resistance data against the equivalent oxide thickness (EOT) of the CBL substrate. Using the relative permittivity values for polysilicon and SiO2 of 11.9 and 3.9 respectively, the EOT of 0.9 µm of polysilicon is 0.3 µm. Fig. 3(c) shows this CBL data compared with the SiO2 BOX. It is clear that for the range of resistor samples manufactured, a reduction in thermal resistance of greater than 50% is achieved compared to an SiO2 BOX with the same EOT and hence identical parasitic capacitance. Further experimental analysis has been undertaken with a batch of substrates (CBL2) which have a fixed oxide thickness and several values of polysilicon layer thickness. The bottom oxide thickness tox1 is 155 nm while the top oxide thickness tox2 is 120 nm. The polysilicon thickness is varied from 118 nm to 746 nm in batch CBL2. Fig. 5 plots the thermal resistance of batch CBL2 as a function of polysilicon thickness. As the polysilicon layer thickness is increased, the thermal resistance of the CBL BOX decreases. This supports the concept of the polysilicon providing a parallel thermal resistance shunt. As the polysilicon layer thickness increases, the shunt thermal resistance decreases in value and results in 3 TED-2014-03-0322-R.R1 an overall decrease in the CBL BOX thermal resistance. The y-axis intercept yields the intrinsic residual thermal resistance associated with the silicon substrate and the two oxides in agreement with value in Fig.3(a). In effect this value of 160 K/W is reduced by the inclusion of the polysilicon. The polysilicon also increases the EOT of the CBL BOX. The experimental data has therefore been plotted against EOT in Fig. 6 along with the SiO2 BOX for comparison purposes. As EOT is increased by employing thicker polysilicon layers, the decrease in thermal resistance compared to an equivalent SiO2 BOX becomes greater. For example a 35-40% reduction in thermal resistance has been achieved for a CBL BOX compared to its equivalent i.e. a 0.5 µm SiO2 BOX. The CBL BOX thermal resistance can be further reduced by reduction of the oxide thicknesses and increase in the polysilicon thickness. Additional samples, labelled CBL3, employed a bottom oxide thickness tox1 of 105 nm and a top oxide thickness tox2 of 91 nm. The polysilicon thickness was varied from 570 nm to 2080 nm. This structure results in a 52% reduction in thermal resistance compared to its equivalent 0.5 m SiO2 BOX. This is increased to approximately 68% when the polysilicon thickness employed is approximately 2 m yielding an EOT of 891 nm. The simple lumped model proposed to analyse the effective thermal resistance of the CBL SOI is shown in Fig. 4. The lateral heat flow path through the polysilicon is modeled with the thermal resistance Rshunt. Circuit analysis has been employed to determine the value of Rshunt in all of the experimentally measured samples. The values Rox1 and Rox2 were calculated using oxide thickness values and the experimentally determined value of oxide thermal conductivity. The effective polysilicon series thermal resistance, Rpoly, was calculated using the polysilicon thickness and a thermal conductivity of 12 Wm-1K-1 [4]. The silicon handle wafer thermal resistance RSH was extracted from the experimental data measured on the CBL BOX substrates. The shunt thermal resistance was calculated for each substrate by employing its experimentally determined thermal resistance and the calculated values of the series connected thermal resistance components. A plot of shunt resistance versus 1/tpoly is shown in Fig. 7 for the range of CBL BOX structures employed. The linear relationship indicates that shunt thermal resistance is inversely proportional to polysilicon layer thickness. The CBL1 samples had a fixed polysilicon thickness. These samples exhibited a shunt thermal resistance of 235 oK/W 5%. An experimental fit for the shunt resistor data can be made in the following equation (3), where K is a constant which will be related to the lateral thermal conductivity of the polysilicon. wafers were 0.01 – 0.02 ohm-cm [100] n type silicon. These were precision ground and polished to the standard commercial quality employed for SOI manufacture. The handle wafer was thermally oxidized at 1050oC to produce an oxide thickness of 280 nm. The active wafers were 15-20 ohm-cm [100] p type silicon. These substrates were thermally oxidized at 1000oC to produce an oxide thickness of 230 nm. The oxidation was followed by LPCVD of polycrystalline silicon at 6200C. A relatively thick layer of polysilicon was deposited and polished to produce a smooth bondable surface with RMS roughness < 1 nm suitable for wafer bonding. The polysilicon thickness after this polishing step was 1.35 µm. The oxidized handle wafer was then bonded to the polysilicon coated active wafer. The structures involved, and the wafer bonding process steps are illustrated in Fig. 8. Following the wafer bond, the substrates were annealed at 1100C for 2 hours to strengthen the bond. Finally the wafers were precision ground and polished to yield a CBL SOI substrate with an active silicon layer thickness of 2.5 0.5 µm and a BOX EOT of 0.96 μm. Using equation (3) and the quoted values for the material thermal conductivities, a Van der Pauw resistor manufactured on this CBL BOX is predicted to yield a 40% reduction in thermal resistance compared to that manufactured on a 1 µm SiO2 BOX. The completed substrates are illustrated in Fig. 1. The CBL dielectric in these substrates was tested by removal of the silicon layer in test areas using a selective chemical etch. Aluminium was deposited and patterned into 1mm diameter capacitor dots. These were intended to verify the CBL dielectric capacitance and its leakage current characteristics at the high voltages associated with the power bipolar transistors. Since the silicon handle wafer has a low resistivity, (0.01 ohm-cm), and the dielectric is relatively thick, the test capacitors have a very high negative threshold voltage ~ 300 V. C-V measurements conducted in the voltage range -30 V to +30 V therefore yielded a constant capacitance of 29 pF. The capacitor remains in accumulation mode and therefore yields an EOT of 0.93 µm in close agreement with the measured layer thicknesses quoted earlier for these substrates. The I-V characteristics of the CBL structure were measured and are plotted in Fig. 9. Very low substrate leakage currents were observed for applied voltages up to ±130 V, which is well in excess of the highest drive voltages used in the power transistors to be manufactured on these substrates. The ±130 V voltages obtained would result in electric fields in the polysilicon of ~ 4.5105 V cm-1. Rshunt = K/tpoly (3) The value extracted for the constant K to fit the experimental graphs in the last two figures is 2.3 x 10 -4 Km/W. A complementary bipolar technology was employed to manufacture a range of NPN and PNP transistors on both standard and CBL SOI substrates. The CBL SOI substrates described in section III had an equivalent oxide thickness of 0.96 µm for direct comparison with standard SOI with a 1µm SiO2 BOX. The transistor manufacture includes silicon epitaxy resulting in an overall silicon layer thickness of approximately 13.5 µm. This is needed to accommodate the depletion layer thicknesses formed within the vertical bipolar III. CBL SOI PRODUCTION FOR BIPOLAR TRANSISTORS The substrate technology has been undertaken initially on 150mm diameter substrates. Wafer bonding technology has been employed in the production of CBL SOI. The handle IV. BIPOLAR TRANSISTOR PERFORMANCE 4 TED-2014-03-0322-R.R1 structures biased at high voltage. The bipolar transistors fabricated on the SOI substrates are isolated by 0.8 µm wide, 13.5 µm deep trenches lined with oxide and nitride layers and filled with un-doped polysilicon. The devices have a double polysilicon emitter base architecture and conventional LOCOS defined active areas with minimum photolithographic feature size of 0.6 µm. The transistor designs employ 1, 2, 4 or 8 emitter fingers with lengths ranging from 2 µm to 32 µm. Contact to the bases is made using polysilicon extended contacts, doped appropriately. The emitter-base junctions are formed from shallow base implants and implanted polysilicon emitters. A typical NPN transistor is shown schematically in cross-section in Fig. 10. Manufacture of the transistors was achieved on CBL SOI substrates in the same process flow as the standard SOI substrates. The electrical characteristics of the transistors were very similar for all substrate types [5] and the typical current gains were 102 and 96 for the standard SOI and CBL SOI substrates respectively. Thermal resistance measurements were taken at wafer level using an Agilent 4155 parametric analyser. The methodology is based on using the base emitter voltage (Vbe) as the temperature sensitive parameter of the devices [15]. In this technique, the transistor is first biased at zero collector-base voltage and collector current (Ic) versus Vbe measurements are taken at various wafer substrate temperatures. From this data, the temperature dependence of base-emitter voltage (dVbe/dT) is then extracted. The substrate is subsequently fixed at a temperature of 300 K, and Ic versus Vbe plots are obtained at various fixed collector base voltages. The change in Vbe is then used in conjunction with the associated dVbe/dT data to estimate the junction temperature increase above ambient at various transistor power dissipation values and then the device thermal resistance is extracted. All transistors on the CBL SOI substrates exhibited a 5% – 18% reduction in thermal resistance compared to standard SOI with 1µm SiO2 BOX. This reduction showed strong dependence on transistor layout geometry, with greater improvements achieved on transistors with lower perimeter/area ratio as shown in Fig. 11(a). The reduction in thermal resistance is less than the 40% value predicted in section III. The emitter/buried collector area ratio in all transistors is relatively small. The emitter is surrounded by high thermal conductivity of the SOI single crystal silicon 13.5 µm in thickness. Heat flow from the emitter will therefore be three dimensional. In addition to the vertical heat flow path to the substrate, there will be a relatively long lateral heat flow path through the silicon to the surrounding trench isolation. Transistors with the largest perimeter/area ratio show smaller reduction in thermal resistance as their thermal performance is dominated by the lateral heat flow to the transistor perimeter compared to the heat flow path in the vertical direction to the substrate. Transistors with a lower perimeter/area ratio show a greater reduction in thermal resistance as the lateral heat flow path is less dominant and the improvement offered by the CBL SOI substrate therefore becomes greater. It is essential to the analysis of these findings, that the lateral heat flow path within the SOI layer transistors is characterized and separated from the substrate thermal resistance. In order to achieve this, the transistor batch has been manufactured on two standard SOI substrates with buried oxide thicknesses of 1.0 µm and 0.5 µm. A simple lumped thermal resistance model of these substrates is shown in Fig. 12. RSOI and RSilat represent the thermal resistances of the vertical and the lateral heat flow paths respectively in the active silicon layer above the BOX. The thermal resistance has been measured on both substrates. RSH, RSOI and RSilat are the same for identical transistors on each substrate, and the only change is in the value Rox. Using the experimental data from Fig. 3(a), the value of (Rox + RSH) for a Van der Pauw resistor manufactured on the two standard SOI substrates would be 400 K/W and 240 K/W. If the resistors had been on a substrate with a 13.5um SOI layer an additional vertical thermal resistance path RSOI of 46 K/W would have occurred, assuming a thermal conductivity for the silicon of 150 W/mK. The vertical thermal resistance of any transistor can then be scaled by a factor 1/c according to its area relative to that of the experimental Van der Pauw test resistors yielding values of 446c K/W and 286c K/W R1 and R2 are the measured thermal resistances of identical transistors on SOI substrates with 1.0 µm and 0.5 µm buried oxide thickness respectively. A value for RSilat can now be extracted for every transistor using the analytical model for transistors on each substrate type as shown in Fig. 13 (a) and (b). Equations (4) and (5) describe the vertical path component of thermal resistance and these can be manipulated to yield a value for RSilat as shown in equation (6). 446c R1 RSilat RSilat R1 RR 286c 2 Silat RSilat R2 0.56 R1 R2 RSilat 1.56 R2 R1 RR ( RCBL 46)c 3 Silat RSilat R3 (4) (5) (6) (7) R3 is the thermal resistance of the transistors manufactured on CBLSOI. The extracted values of RSilat for each transistor can now be employed using equation (7) to determine the vertical thermal resistance component of the CBL SOI substrate for direct comparison with standard SOI. Fig. 14 shows the measured values of thermal resistance R1, R2 and R3 of identical transistors on the three substrate types. Four transistor designs have been included with 1, 2, 4 or 8 emitter fingers of length 24 µm. The extracted value for Rsilat for each transistor type is also included in Fig. 14. Increasing the number of emitter fingers results in both increased area and increased perimeter and hence all thermal resistance values decrease. Fig. 15 shows the vertical thermal resistance of the transistors on the three substrate types. This shows clearly that in comparison with the standard SOI substrate with a 1.0 µm SiO2 buried insulator, the CBL SOI substrate yields a 40-46% reduction in the vertical thermal resistance of the transistors which is in good agreement with the predicted improvement 5 TED-2014-03-0322-R.R1 for this substrate. It is also notable that the CBL BOX, which includes 0.51 µm of SiO2, exhibits lower thermal resistance than standard SOI with a BOX consisting of 0.5 µm SiO 2. The analysis was extended to all the transistor designs and the percentage improvement in the vertical thermal resistance is plotted in Fig. 11(b). This shows improvements in the vertical thermal resistance of the order 40%, as predicted, irrespective of transistor geometry, size or area/perimeter ratio. Fig. 15 shows that RSilat in these power transistors is much smaller than the vertical path thermal resistance. Depending on the transistor layout design, the SOI with a 1 µm SiO 2 BOX has 65% -90% of the heat flow via the conduction through the lateral value RSilat. RSilat will be inversely proportional to the silicon layer thickness. Therefore any transistors or integrated circuits which can be manufactured on thinner silicon layers will have thermal resistance reduction closer to that of the vertical heat flow path. The reduction in thermal resistance will approach the 40% value for silicon layer thicknesses less than 1 µm. The CBL SOI substrates in this work were designed to match the EOT of the standard power transistor substrate. The thermal resistance can be further reduced by using thinner oxide layers in the CBL BOX. The oxide and polysilicon thicknesses can be adjusted to meet any design requirements for breakdown voltage and parasitic capacitance. The CBL substrate therefore has further potential application to ease thermal issues in high density CMOS integrated circuits. V. CONCLUSIONS A novel SOI substrate which includes a compound buried layer as the buried insulator (BOX) has been demonstrated to provide lower thermal resistance than a conventional SiO2 BOX of the same equivalent oxide thickness. The thermal resistance of Van der Pauw structures manufactured on CBL SOI substrates has been reduced by ~50% compared to standard SOI of the same equivalent oxide thickness. This significant improvement has been shown to be dominated by a lateral heat flow path along the buried polysilicon layer. The CBL SOI substrate also exhibited lower parasitic capacitance showing the un-doped polysilicon acted as a dielectric layer, and supported high voltages. The CBL SOI manufacturing process has been achieved and substrates designed to achieve a 40% reduction in thermal resistance were supplied to industrial partners. The CBL SOI substrates have been successfully used in the production of commercial power bipolar transistors. The transistor electrical parameters and yields on CBL SOI were identical to those manufactured on standard SOI substrates. The thermal resistance of the power bipolar transistors manufactured on 13.5 µm thick active silicon layers on CBL SOI exhibited a 5% - 18% reduction in thermal resistance compared to identical transistors manufactured on conventional SOI substrates. Active transistors of this thickness exhibited 65%-90% of their heat loss due to lateral heat flow through surrounding single crystal silicon. Extraction of data concerning the thermal resistance of the transistors to the vertical heat flow confirmed the CBL SOI substrate provided a reduction by ~ 40%, in agreement with the predicted performance improvement. A simple lumped model taking into account lateral heat flow has been developed and used to ascertain the different heat flow paths and their relative importance in practical situations. REFERENCES [1] P. Baine, K. Y. Choon, H. S. Gamble, B. M. Armstrong and S. J.N.Mitchell, “Novel materials for Thermal Via incorporation into SOI structyres”, J. Materials Science, Materials in Electronics, 12, 2001, pp. 215-218 [2] Gamble HS "Variants on Bonded SOI for Advanced ICs" Electrochemical Society, Silicon-on-insulator Technology and Devices X, Proc 10th Intl Symp Vol.2001-3, pp.1-12 Washington DC March 2001 ISBN 1-56677-309-1W.-K. Chen, Linear Networks and Systems. Belmont, CA: Wadsworth, 1993, pp. 123–135. [3] S D Hu, X R Luo, B Zhang and Z J Li, “Design of compound buried layer SOI high voltage device with double windows” Electron, Lett. Vol 46 no 1, 2010 pp 82-84 [4] K Van Wichelen, M Schaekers, S Decoutere, M Seacrist, V Drobny and R Wise, “Sandwich stacks replacing SiO2 in standard bonded Si-onInsulator (SOI) substrates to obtain a High-Thermal-Conductivity HTCSOI substrate” IEEE International SOI Conference Proceedings, 2008, pp 67-68. [5] S J Harrington, A Bousquet, S Nigrin, S.Suder and B M Armstrong, “A High Performance 36 V Complementary Bipolar Technology on Low Thermal Resistance Compound Buried Layer SOI Substrates”, IEEE Proc BCTM 2010, pp37-40 [6] L Wei, M Vaudin, C S Hwang, G White, J Xu and A J Stecky, “ Heat conduction in Silicon thin films: Effect of Microstructure.” J Mater. Res., Vol.10, No. 8, 1995, pp 1889 – 1896. [7] S Uma, A D McConnell, M Asheghi, K Kurabayashi and K E Goodson, “Temperature-Dependent Thermal Conductivity of Undoped Polycrystalline Silicon Layers”, International Journal of Thermophysics, Vol 22, No.2, 2001 pp 605 – 616. [8] A Jain and A Kumar, “Effect of Surface and Grain Boundary on Lattice Thermal Conduction of Polycrystalline Silicon Layers”, Proc ISRS on Materials Science and Engineering, Dec 2004 [9] Z Lv, J Yuan, L Tian, L Liu, Z Li , “Measurement of the Thermal Conductivity of Undoped Polysilicon Thin Films Over 300K to 400K”IEEE Proc ICSICT 2004, PP 1796 – 1799. [10] M von Arx, O Paul and H Baltes, “Process-Dependent Thin Film Thermal Conductivities for Thermal CMOS MEMS”, IEEE J Micromechanical Systems, vol 9 no 1, March 2000 [11] F Volkien and H Baltes, “A Microstructure for Measurement of Thermal Conductivity of Polysilicon Thin Films” IEEE J Micromechanical Systems, vol 1 no 4, Dec 1992. [12] A D McConnell, S Uma and K E Goodson, “Thermal Conductivity of Doped Polysilicon Layers” , J Micromechanical Systems,Vol. 10, no. 3, 2001, pp 360 – 369. [13] OS Panwar, RA Moore , SH Raza , HS Gamble , BM Armstrong “Comparative Study of Large Grains and High-Performance TFT’s in Low Temperature Crystallised LPCVD and APCVD Amorphous Silicon Films”, Thin Solid Films, Vol.237, No.1-2, 1994, pp255-267. [14] B. M.Tenbroek, R. J. T.Bunyan, G.,Whiting, W.Redman-White, M. J. Uren, K. Brunson, and C. F.Edwards, “Measurement of buried oxide thermal conductivity for acccurate electrothermal simulation of SOI” IEEE Trans Electron Devices, Vol. 46, No 1, 1999, pp. 251 – 253. [15] van Noort WB, Dekker R. “Thermal resistance of HBT’s on bulk Si, SOI and glass”, IEEE Proc BCTM 2003. p.129-132 6 TED-2014-03-0322-R.R1 Active Si layer _ tox2 _ tpoly _ tox1 _ 8 µm wide Al test structure ox2 SiO2 polySi poly Si ox1 SiO2 Rpoly Rshunt Rox1 Silicon handle n+ Si Handle Rox2 RSH . Figure 1. Cross-section schematic of the CBL SOI V W Figure 4 CBL BOX schematic and lumped thermal model. Top oxide thermal resistance Rox2, bottom oxide thermal resistance Rox1, polysilicon series thermal resistance Rpoly, polysilicon lateral shunt thermal resistance Rshunt, silicon substrate thermal resistance RSH L I Figure 2. Schematic layout of the Van der Pauw test structure (a) Figure 5 Thermal resistance for CBL2 BOX plotted against polysilicon layer thickness with tox1 =155nm and tox2 = 120 nm 450 400 350 (c) 300 Rth (K/W) (b) SiO2 BOX 250 CBL2 200 CBL3 150 Linear (CBL2) Linear (CBL3) 100 50 0 Figure 3 Experimental thermal resistance for (a) SiO2 BOX Rth v tox, (b) CBL1 BOX Rth v (tox1 + tox2) and (c) CBL1 BOX Rth v EOT. CBL1 BOX consists of tpoly =0.9µm, tox2 = 90 nm and various values of tox1 0 200 400 600 EOT (nm) 800 1000 1200 Figure 6 Thermal resistance of CBL SOI substrates with several polysilicon thicknesses plotted against EOT and compared with SiO2 BOX. CBL2 employs tox1 =155nm and tox2 = 120 nm, CBL3 employs tox1 =105nm and tox2 = 91 nm 7 TED-2014-03-0322-R.R1 p+ polysilicon B E 2500 n+ polysilicon C CVD oxide 2000 oxide n+ 1500 Shunt Rth (K/W) p + p CBL1 CBL2 CBL3 1000 n+ epitaxy n- 500 sinker buried n+ Buried SiO2 or CBL BOX 0 0 0.002 0.004 0.006 1/tpoly (nm-1) 0.008 insulator 0.01 Si handle wafer Figure 7 Shunt thermal resistance v 1/polysilicon thickness Figure 10 Schematic cross-section of a NPN transistor 55.00 50.00 45.00 % reduction oxide Si active wafer Si handle wafer (b) 40.00 polysilicon 35.00 30.00 25.00 Total Rth reduction 20.00 Vertical Rth reduction 15.00 Power (Total Rth reduction) 10.00 (a) Linear (Vertical Rth reduction) 5.00 Figure 8 The handle and active wafers prepared for wafer bonding 0.00 0.00 1.00 2.00 3.00 4.00 5.00 Perimeter/Area ratio (cm-1) 1.0E-08 Figure 11 Percentage reduction in (a) the total thermal resistance, and (b) the vertical thermal resistance of transistors manufactured on CBL SOI compared to standard SOI 8.0E-09 6.0E-09 4.0E-09 I (A) 2.0E-09 -200 -150 -100 0.0E+00 -50 0 -2.0E-09 50 100 150 200 active silicon oxide -4.0E-09 RSOI RSilat -6.0E-09 -8.0E-09 -1.0E-08 Applied voltage (V) silicon substrate Rox RSH 9 I-V characteristics of MOS capacitors manufactured with CBL dielectric structure Figure Figure 12 Lumped thermal model of the transistors on SOI 8 TED-2014-03-0322-R.R1 446c RSilat R1 RSilat R2 RSilat R3 (a) 286c (b) (RCBL+46)c (c) Figure 13 Analytical lumped models for transistors on the three substrate types. Figure 14 Measured thermal resistance of transistors on the three SOI substrate types for transistors with 1, 2, 4 and 8 emitters of length 24 m together with the extracted values of RSilat Figure 15 Extracted values of the vertical path thermal resistance of the three substrate types together with RSilat