Lab 5 - University of Connecticut

advertisement

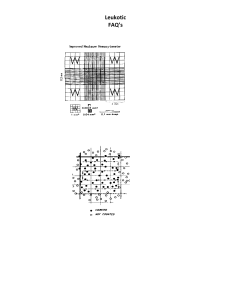

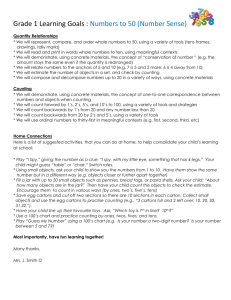

University of Connecticut Computer Science and Engineering CSE 268 Fall 2000 Lab Five: Counting Networks Using Atomic Data Structures In this lab you will continue using your simple multi-threaded system that relies on PowerPC memory access synchronization primitives. In this lab your will (1) develop an atomic balancer data structure and test its linearizability, (2) develop a 4-input/4-output Bitonic counting network using your atomic balancer data structures and observe its behavior, and (3) repeat the exercise for 8-input/8-output Bitonic network. In addition to the material that was covered in Lab 3 and Lab 4 dealing with PowerPC interrupts, time base and memory synchronization primitives, you will need to review/learn the following material that was presented in class: J. Aspnes, M. Herlihy and N. Shavit, ”Counting Networks”, Journal of the ACM, vol. 41, no. 5, pp. 1020-1048, 1994 Sections 1 and 2.1: basic information and properties Section 3: Bitonic network construction N. Lynch, N. Shavit, A. Shvartsman and D. Touitou, “Timing Conditions for Linearizability in Uniform Counting Networks,” Theoretical Computer Science, special issue on Distributed Algorithms, vol. 220, pp. 67-91, 1999 Section 1: background and main linearizability results Section 2:.definition of linearizability and non-linearizability We now describe the three parts of the lab in more detail. 1 Atomic 2-Input/2-Output Balancer and Linearizability In this exercise you will use the multi-threaded program you developed in Lab 3 and the techniques for constructing atomic data structures you learned in Lab 4 to construct a single 2input/2-output balancer. A balancer inputs “tokens” on the balancer's input “wires” and outputs the tokens on its output “wires”. The balancer servers as a toggle mechanism that, given a stream of input tokens, repeatedly sends one token to the “top” (or North) output wire and one to the “bottom” (or South) output wire, effectively balancing the number of tokens that have been output. Recall that balancers admit two equally valid interpretations: one in terms of “nodes” and “wires”, and the other in terms of “data structures” and “pointers”. On a shared memory multiprocessor, counting networks are implemented as data structures, in which balancers are represented as records and wires as pointers among them. Tokens are “shepherded'” by threads that traverse this pointer-based data structure from input pointers to output wires, finally incrementing the counter on the appropriate output wire. This implies that tokens may overtake one another on a wire and that balancer and network traversal times are dependent on individual thread/processor speeds and variations in these speeds. You will need to construct a single copy of a balancer whose outputs are connected to two atomic counters by means of pointers. The North counters is initialized to 0, the South counter is initialized to 1, and both count in increments of 2. You will need to test the linearizability of this simple single-balancer counting network using 2, 3 and 4 threads. You must try to alter your schedule in order to cause as many non-linearizable operations as possible. In the case of 3 threads, you must be able to reproduce the example of non-linearizability that was discussed in class. 1 University of Connecticut Computer Science and Engineering 2 CSE 268 Fall 2000 4-Input/4-Output Bitonic Counting Network In this exercise you will use the balancers and atomic counters developed in Part 1 to construct a 4-input/4-output Bitonic Counting Network. You will need 4 atomic counters that count in increments of 4. The first counter starts at 0, the second at 1, the third at 2 and the fourth at 3. You will run counting experiments using 2, 4 and 8 threads, in which each thread repeatedly invokes the increment operation using the counting network. You will need to instrument your experiment to make it easy to see how many non-linearizable operations were encountered. Inputs Outputs Values x0 y0 0, 4, 8, 12, … x1 y1 1, 5, 9, 13, … x2 y2 2, 6, 10, 14, … x3 y3 3, 7, 11, 15, … Design your network in a modular way so that you can use your code in a modular way in the next experiment. 3 8-Input/8-Output Bitonic Counting Network This exercise is similar to Part 2. To construct a 8-input/8-output Bitonic Counting Network you will need two instances of the 4-input/4-output counting networks (from Part 2) and the additional balancers and atomic counters (developed in Part 1) to configure the merge network. You will need 8 atomic counters that count in increments of 8. You will run counting experiments using 2, 4 and 8 threads, in which each thread repeatedly invokes the increment operation using the counting network. You will need to instrument your experiment to make it easy to see how many non-linearizable operations were encountered. Inputs Outputs Values x0 y0 0, 8, 16, … x1 y1 1, 9, 17, … x2 y2 2, 10, 18, … x3 y3 3, 11, 19, … x4 y4 4, 12, 20, … x5 y5 5, 13, 21, … x6 y6 6, 14, 22, … x7 y7 7, 15, 23, … Bitonic[4] Merger[8] 2 University of Connecticut Computer Science and Engineering 4 CSE 268 Fall 2000 Deliverables You will write a report documenting the three exercises for the required number of threads. The report must adhere to the lab report requirements. Make sure to include the high level design of your programs. For the exercise in part 1 describe also an example sequence of events that leads to non-linearizable behavior. You need to include a table that shows the counting operations. For each operation give some operation identifier, start time, finish time and the counter value obtained. Note that you need to instrument your code to collect the data, but you do not need to analyze the data on the PowerPC. It is enough to dump the data into a file and then analyze it on a PC (any PC). The analysis code does not need to be submitted. You will need to include all code in your report and (optionally) to demonstrate your programs. The report is due at 9 am in class on October 24, 2000 (after the Spring break). 3