HV Test System Design Proposal

advertisement

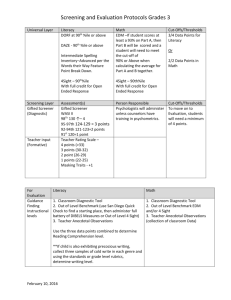

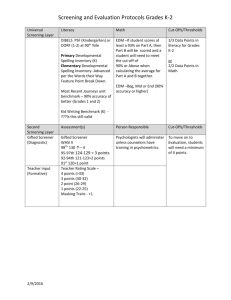

LHCb Outer Tracker FE Electronics ―A Proposal for HV Board Tester 0 HV BOARD TESTER ............................................................................................................................ 1 0.1 General description .................................................................................................................... 1 0.2 Specifications ............................................................................................................................. 1 0.3 Block Diagram and Schematics ................................................................................................. 2 0.4 Layout......................................................................................................................................... 4 0.5 Caution ....................................................................................................................................... 4 1 HV CONTROLLER ............................................................................................................................... 5 1.1 General description ............................................................................................................. 5 1.2 Specification ............................................................................................................................... 5 1.3 Schematic ................................................................................................................................... 6 1.4 Reed Relay.................................................................................................................................. 8 2 MUX.................................................................................................................................................. 3 2.1 General description .................................................................................................................... 3 2.2 Specification ............................................................................................................................... 3 2.3 Schematic ................................................................................................................................. 10 2.4 Switch ....................................................................................................................................... 11 2.5 Pre_amp ................................................................................................................................... 14 3 CAPACITOR ....................................................................................................................................... 15 3.1 General description .................................................................................................................. 15 3.2 Specification ............................................................................................................................. 15 3.3 Schematic ................................................................................................................................. 16 3.4 Caution ..................................................................................................................................... 17 4 MONITOR ......................................................................................................................................... 18 4.1 General description .................................................................................................................. 18 4.2 Specification ............................................................................................................................. 18 4.3 Schematic ................................................................................................................................. 18 5 MCU .................................................................................................................................................. 5 5.1 General description .................................................................................................................... 5 5.2 Specifications ............................................................................................................................. 5 5.3 Schematic ................................................................................................................................... 5 5.4 Caution ....................................................................................................................................... 5 6 POWER ............................................................................................................................................. 21 6.1 General description .................................................................................................................. 21 6.2 Specifications ........................................................................................................................... 21 6.3 Schematic ................................................................................................................................. 16 6.4 Caution ..................................................................................................................................... 16 7 ACCESSORIES: MOTHERBOARD, CABLING, AND CONNECTORS ......................................................... 17 7.1 Motherboard............................................................................................................................. 17 7.2 Cabling ..................................................................................................................................... 17 7.3 Connectors ............................................................................................................................... 17 0 HV Board Tester 0.1 General description HV boards tester is designed for testing 1,950 HV boards of LHCb Outer Tracker before they are mounted into the front-end electronics box. A test on prototype HV boards has demonstrated that the most critical components in HV board are Johanson capacitors, which are buried inside the 4 layer printed circuit boards. They will be burned-in with high voltage up to 2.5kV and put into the temperature chamber for thermal cycling as well for several days. So the basic function of the tester is to monitor the capacitor parameters such as leakage current, capacitance during burn-in and thermal cycling. It is necessary to measure the capacitance of each channel of capacitor because the broken capacitor may lose its capacitance partially while its leakage current remains low. The leakage current from HV pads to the ground pads (plane) is also critical and needs to be measured at the same time. The functions of the HV board tester include: 1. Distributing (providing, optional) high voltage to HV boards under test; 2. Monitoring the leakage current of 32 capacitors in each board and the leakage current from HV pads to ground pads (plane) of each board; 3. Measuring the capacitance of each channel regularly; 4. Monitoring temperature, humidity inside the temperature chamber, voltage and total current of the high voltage supply; 5. Transferring all measured data to PC. The following table shows the time needed to test 1,950 HV boards for different testing strategies. Testing time / run Testing boards / run Testing time in total 1 wk 32 61 wks 1 wk 64 31 wks 2 wks 32 122 wks 2 wks 64 61 wks 0.2 Specifications 0.2.1 I/O specifications NAME Description I/O TYPE NOTE HV_INPUT HV supply Input HV up to 2.5kV HVGND HV GND Input GND HV_OUT<1..32> HV output to HV boards Output HV C[1..1024] Connection from HV capacitor Input analog RS232 Communication to PC I/O digital RS232 Power1,2 Tester power supply Power AC 220V, 50Hz up to 2.5kV 1 0.2.2 Performances Capacity: 32 HV boards / tester Leakage current measurement: 1nA-1uA Capacitance measurement: 1pF Communication interface to PC: RS232 (USB, optional) 0.2.3 Power dissipation 0.3 Block Diagram and Schematics HV Board Resistors Embed Caps Connector Board A Connector Board B HV POWER SUPPLY HV_INPUT Temperature Chamber HVGND HV_OUT[1..32] HV BOARD HVBI[1..1024] TESTER ILEAKBRD[1..32] HV Board Tester Motherboard RS232 Fig 0.1 HV Board Tester System The whole test system for HV boards is shown in Figure0.1. 32 HV boards can be mounted on the tester motherboard at the same time and they will be put into the temperature chamber with temperature up to 80oC. An external HV power supply is needed. 32 channels of high voltages are sent into the tester motherboard from the HV board tester and 1024 channels of signals are connected out in the opposite direction. The large number of connections cannot be avoided otherwise one has to consider the reliability problem to put electronics into the temperature chamber. RS232 serial communication protocol is implemented in the HV board tester because of its compatibility and simplicity. 2 1 2 3 4 5 6 A A HV _Co ntro ller HV Con tro ller.SCH DOC AG ND +15 V +5V M on itor M on itor.SCHD OC Ad d[0 ..2 ] Ctrl_B[0 ..7] WR DG ND V_ pt 10 0s upp ly V_ s6 00 0s upp ly V_ tem perature V_ RH HV _IM ON HV _V MO N HV _ITRIP HV _V TRIP INT HV _IM ON HV _V MO N HV _ITRIP HV _V TRIP HV _O UT[1 ..32 ] AD D[0 ..2] Ctrl_B[0 ..7] WR DG ND VM ON +15 V -15 V +5V GN D M CU VM ON V_ ileakcap V_ ileakbrd Repeat(H ig h v oltage b oard, 1,3 2) to PC B INT HV _INPU T HV _G ND Be careful in the shielding continuity!!! HV _IN[1 ..3 2] AD D[0 ..2] Ctrl_B[0 ..2] WR DG ND B VCA P1 VCA P2 VSQ UARE HV BO[1. .10 24 ] ILEA KBRD[1 ..32 ] RS23 2 M UX M UX. SCHDO C Repeat(p re_am p,1 ,3 2) pre_ amp .SCHD OC HV BI[1 ..1 02 4] ILEA KBRD[1 ..32 ] HV _G ND +5V GN D -5V +15 V -15 V C AD D[0 ..2] Ctrl_B[0 ..7] WR DG ND V_ ILEA KCAP V_ ILEA KBRD Repeat(ILE AK) Repeat(V _ILE AK) HV _G ND +15 V GN D -15 V +5V -5V CAPA CITA NCE C Pow er File Nam e Capacitor Capacitor. SCH DOC +15 V -15 V CAPA CITA NCE HV _G ND VSQ UARE VCA P1 +5V VCA P2 GN D DG ND +5V -5V GN D Tester for HV board D D Title Tester for HV board Size Nu m ber Revi sion Orcad B 1 1 2 3 8 4 Date: File: 5 20 03 -12 -16 Sheet of C:\Docu m ents and Settin gs \..\ Tester for H VDrawn b oard. SCH By: DO C 6 Fig 0.2 Schematics of the HV board tester The HV board tester consists of 6 functional modules: HV controller, MUX, Capacitance, Monitor, Power and MCU. The schematic of the HV board tester is shown in Figure0.2. HV controller distributes high voltage to 32 boards using external HV power supply. Each channel of high voltage output can be controlled individually by a reed relay. Analog monitoring signals of the voltage and total current of the high voltage supply are provided to Monitor module. High voltage trip and total current trip can be set by adjusting internal potential meters continuously. The lower potential nodes of the HV capacitors are connected out to MUX module, where in total 1,024 capacitors are multiplexed to leakage current and capacitance measurement circuits correspondingly, e.g., capacitance is measured for each capacitor, while leakage current is measured for each board (32 channels of capacitors). Preamplifiers used in leakage current measurement are also included in this module. Capacitance of each capacitor is measured by Capacitance module. Monitor module measures all environment and condition parameters such as temperature, relative humidity, high voltage and its total current, trip levels set by HV controller. Power module provides ±15V, ±5V low voltage power supply. All analog measurement signals are digitized by ADCs inside MCU (micro-control unit). Meanwhile the MCU sends out all control signals needed in other modules such as address signals for multiplexers. The communication interface to PC is also implemented by the MCU module. Each module will be described in detail in following sections. 3 0.4 Layout Fig 0.3 Layout of the HV board tester Backboard architecture is adopted for its convenience for maintenance, as is shown in Figure0.3. Some function modules are divided into several repeated PCB boards due to the large channel number, e.g., MUX module. CH is the reed relay, which is used for 32 channels high voltage distribution. N and M are the number of the same type PCB. To depress the electromagnetic interference and crosstalk between channels, ground shielding should be kept along signal paths continuously, and twisted-pair or coaxial cables should be used to connect 024 signal channels and 32 HV output channels. 0.5 Caution 1. The trip thresholds should be set in advance before adding on any high voltage, otherwise protection circuit won't work properly. 2. Be sure that the safety voltage indicator is on or the high voltage is discharge when connecting/disconnecting high voltage and handle HV boards manually. 4 1 HV Controller 1.1 General description HV Controller is used for dispatching high voltages, and providing monitoring signals of the input high voltage and its total current. There are 32 high voltage output channels, which supply high voltages for 32 HV boards under testing. Each channel of them can be switched on/off independently. The monitoring signals are isolated from HV up to 2500V RMS. Over voltage/current protection and indication, and safety voltage indication are also implemented in this module. 1.2 Specification 1.2.1 I/O specification NAME Description I/O TYPE NOTE ADD[0..2] Control registers address Input TTL Ctrl_B[0..7] Control word bus Input TTL WR Control word write enable Input TTL DGND Digital Ground Input HV_INPUT High voltage supply Input 0~2500Vrms HV_GND High voltage GND Input HV_GND HV_OUT[1..32] High voltage output channels Output 0~2500Vrms INT HV tripped interrupt Output TTL 1=HV tripped HV_VTRIP HV voltage trip threshold Output 0~1V ~1V/3000V HV_ITRIP HV current trip threshold Output 0~1V ~1V/1mA HV_VMON HV voltage monitor output Output 0~1V 1V/3000V HV_IMON HV current monitor output Output 0~1V 1V/1mA +15V DC power supply Power +15V Typ:260mA Max:2880mA +5V Power +5V Typ: 176.2mA Max: 273.7 mA GND Power GND 1.2.2 Accuracy HV voltage monitor accuracy: better than 3V. HV current monitor accuracy: better than 1uA. 5 1.2.3 Power dissipation Typical: 4.781W Max: 44.569W 1.3 Schematic 1 2 3 4 5 6 7 8 AG ND R6 1K C5 .0 1u F U2 AG ND GN D INB+ INA+ INBINAOU TB OU TA VCC U4 FB 1 0k R10 1 0K HV _ITRIPE D A +5 AG ND M AX 91 07 R7 C6 R8 .0 1u F 1 K 4 .7K R12 1 0K AD 21 0 HV _ITRIP C19 R16 1K RS22 0-5 27 9 R18 HV _IM O N AG ND D1 R15 IN 1 00 M HV _G ND OU T S0 GND +15V HV _G ND R63 ICOM 1 0k ON DGND Vcc K1 Reed relay.SCHD OC BZV 85 -C12 1 2V HV _IN PUT IN DS1 1 R22 2 OU T S1 GND +15V B ON DGND Vcc K2 Reed relay.SCHD OC +5 1K K3 Reed relay.SCHD OC U6 B is Vs afe 1 2 3 HV _G ND R64 1 00 M 4 IN OU T DM 7 4A LS04 BSJ S2 GND +15V DM 7 4A LS04 BSJ ON DGND Vcc GRE EN U6 A +5 R23 4 .7K C36 13 GN D 1 Clr_ trip CLR 2 D R24 1K 5 Q 12 CLK D 9 Q U1 4A 1 3 S1 INT DM 7 4A LS04 BSJ SHV 1 DM 7 4A LS08 SJ U1 4B 4 6 +5 HV _V TRIPED U1 5A 1 10 2 R25 1k 6 4 U6 C 5 C 11 CLK 2 Ov er Vo ltage PR 1 CLR 3 +5 U7 B 8 DM 7 4A LS74 ASJ Q PR Q DS2 4 .7u F U7 A 6 DM 7 4A LS74 ASJ 3 HV _G ND 1M R30 HV 32 1M R31 HV 31 1M R32 HV 30 1M R33 HV 29 SHV 0 S1 4 6 U1 5C 11 9 S0 13 9 DS3 1 8 HV 28 1M R35 HV 27 1M R36 HV 26 1M R37 HV 25 1M R38 HV 24 1M R39 HV 23 1M R40 HV 22 1M R41 HV 21 1M R42 HV 20 1M R43 HV 19 1M R44 HV 18 HV Repeat(IN ) B Repeat(O UT ) C29 1 uF C30 1 uF C31 1 uF C32 1 uF C33 1 uF C34 1 uF C7 .0 1u FC18 .0 1u F HV 17 1M R46 HV 16 1M R47 HV 15 1M R48 HV 14 1M R49 HV 13 1M R50 HV 12 1M R51 HV 11 1M R52 HV 10 1M R53 HV 9 1M R54 HV 8 GN D WR Ad d[0 ..2 ] Ctrl_B[0 ..7 ] HV _IM O N HV _V M ON HV _ITRIP HV _V TRIP INT 1M R55 HV 7 1M R56 HV 6 1M R57 HV 5 1M R58 HV 4 1M R59 HV 3 1M R60 HV 2 1M R61 HV 1 Ad d[0 ..2 ] U8 B2 1 WR 1 1 Ctrl_B0 3 Ctrl_B1 4 Ctrl_B2 7 Ctrl_B3 8 Ctrl_B4 1 3 Ctrl_B5 1 4 Ctrl_B6 1 7 Ctrl_B7 1 8 1/8 W act as fuse sockets are needed S2 C9 .0 1u F C10 .0 1u F C11 .0 1u F U9 B4 1 WR 1 1 OE CLK D1 D2 D3 D4 D5 D6 D7 D8 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 2 5 6 9 12 15 16 19 CH1 CH2 CH3 CH4 CH5 CH6 CH7 CH8 C12 .0 1u F C13 .0 1u F C14 .0 1u F C15 .0 1u F C16 .0 1u F C17 .0 1u F +1 5V AG ND +5 V DG ND WR Ad d[0 ..2 ] Ctrl_B[0 ..7 ] HV _IM O N HV _V M ON HV _ITRIP HV _V TRIP Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 2 5 6 9 12 15 16 19 CH1 7 CH1 8 CH1 9 CH2 0 CH2 1 CH2 2 CH2 3 CH2 4 +5 1 2 3 R65 6 4 5 4 .7K DG ND A B C Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 OE 1 OE 2A OE 2B 15 14 13 12 11 10 9 7 INT B1 B2 B3 B4 B5 C SN7 4L S1 3 8D DM 7 4S3 74 WM U1 0 U1 1 B5 1 WR 1 1 OE CLK D1 D2 D3 D4 D5 D6 D7 D8 D1 D2 D3 D4 D5 D6 D7 D8 HV _O UT [1.. 32 ] U1 3 Ad d0 Ad d1 Ad d2 OE CLK Ctrl_B0 3 Ctrl_B1 4 Ctrl_B2 7 Ctrl_B3 8 Ctrl_B4 1 3 Ctrl_B5 1 4 Ctrl_B6 1 7 Ctrl_B7 1 8 DM 7 4S3 74 WM DM 7 4A LS08 SJ C8 .0 1u F OU T[1 ..3 2] +5 B3 1 WR 1 1 C35 1 uF OU T AG ND +5 C28 1 uF .1 uF +1 5V 1M R45 Ctrl_B0 3 Ctrl_B1 4 Ctrl_B2 7 Ctrl_B3 8 Ctrl_B4 1 3 Ctrl_B5 1 4 Ctrl_B6 1 7 Ctrl_B7 1 8 C27 1 uF C21 AG ND Repeat(Ch ,1 ,32 ) Reed relay.SCHD OC HV [1. .32 ] R26 1K C26 1 uF Vs afe R20 R62 1 K 3 .6K HV _V M ON 2 C25 1 uF 1 00 K C24 1 uF R17 R21 1K Sho rtage DG ND R28 4 .7K HV _V TRIP C20 AG ND 1M R34 10 DM 7 4A LS32 SJ GN D1 0 +5 R9 AD 21 0 is Vs afe M AX 91 07 R14 1 0K DM 7 4A LS32 SJ DM 7 4A LS04 BSJ +5 HV _V TRIPED R13 1 0K 1K U1 4C 5 8 DM 7 4A LS08 SJ 12 HV _G ND AG ND +1 5V AG ND ICOM OCO M PWR PWRCO M VO +VO SS -VO SS GN D INB+ INA+ INBINAOU TB OU TA VCC .1 uF U1 5B U1 4D 12 DM 7 4A LS04 BSJ U6 F FB 1M DM 7 4A LS08 SJ 8 2 13 +VISS -VISS R29 5 U6 D 9 DM 7 4A LS32 SJ HV _ITRIPE D +IN -IN R27 3 .3M OU T U3 AG ND U5 1G .1 uF R19 1K AG ND Repeat(ON) DGND Vcc +VISS -VISS R11 ICOM AG ND +1 5V AG ND ICOM OCO M PWR PWRCO M VO +VO SS -VO SS CH GND +15V +IN -IN CH[1..32] A Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 2 5 6 9 12 15 16 19 CH9 CH1 0 CH1 1 CH1 2 CH1 3 CH1 4 CH1 5 CH1 6 OE CLK Ctrl_B0 3 Ctrl_B1 4 Ctrl_B2 7 Ctrl_B3 8 Ctrl_B4 1 3 Ctrl_B5 1 4 Ctrl_B6 1 7 Ctrl_B7 1 8 DM 7 4S3 74 WM D1 D2 D3 D4 D5 D6 D7 D8 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 2 5 6 9 12 15 16 19 CH2 5 CH2 6 CH2 7 CH2 8 CH2 9 CH3 0 CH3 1 CH3 2 DM 7 4S3 74 WM CH[1 ..3 2] R66 10 +5 VCC U1 2 B1 1 WR 1 1 AG ND +1 5V C37 1 0uF C38 1 0uF C22 .1 uF C23 .1 uF Ctrl_B0 3 Ctrl_B1 4 Ctrl_B2 7 Ctrl_B3 8 Ctrl_B4 1 3 Ctrl_B5 1 4 Ctrl_B6 1 7 Ctrl_B7 1 8 D OE CLK D1 D2 D3 D4 D5 D6 D7 D8 SHV [0.. 1] Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 2 SHV 0 5 SHV 1 6 Clr_ trip 9 12 15 16 19 D DM 7 4S3 74 WM Title Size HV Controller Nu mber Revisio n A2 Date: File: 1 2 3 4 5 6 7 2 00 3-12 -16 Sheet 2o f C:\Do cuments and Settin gs\..\HV Con tro ller.SCH Draw nDO By:C 8 8 Fig. 1.1 Schematic of the HV Controller module The functional block diagram is illustrated in Figure1.2. Each block can be found in the Figure 1.1. Their positions are listed below: Input control relay B3~B4 Current tripper A2~A3 Voltage tripper A4~A6 Control registers C5~D7 Control logic unit C1~C3 Dispatcher B4~C4、B5 There are three input control relays, used for current limiting when the high voltage is switched on and discharging the capacitors when the high voltage is switched off. Any exception such as over-voltage or HV-short would cause switching off the high voltage and discharging capacitors automatically by proper operation of these relays. The control signals are generated from the “Control logic unit” block, which is the logic combination of 3 bits control signals from control register Add0 and 2 trip signals from “Current tripper” and “Voltage tripper”. When the system is tripped, and the Bit2 of the Add0 register is set to '1', a trip interrupt occurs, and high voltage is switched off. The trip thresholds of “Current tripper” and "Voltage tripper" can be set via the corresponding varistor. Analog outputs of these thresholds are also provided for monitoring, 6 together with monitoring signals of the high voltage and its total consumption current. HV Current trip threshold HV Current monitor 1 HV input Input control relay Current tripper Dispatcher 32 Control logic unit Control word[0..7] Address[0..2] HV_OUT[1..32] HV voltage trip threshold voltage tripper HV voltage monitor 4 Tripped INT Control registers 32 WR Fig. 1.2 Block diagram of HV Controller The "Dispatcher" block, in which there are 32 channels of relays, can switch on/off each HV output channel independently. The “Control registers” latch all control signals from MCU. Over voltage/current and safety indications are implemented in this block. Two varistors at 'A3' and 'A6' in Figure 1.1, used for setting HV trip thresholds, are placed in the front panel. The 1G resistor at 'A4', used for monitoring the high voltage, needs high voltage rating >= 3kV. There are 2 isolation amps used for isolating high voltage, and their rating isolation voltages are 2500V RMS. All reed relays’ switching voltage must be >= 3kV. The 32 relays in dispatcher block are “Form B (normal close)” reed relays, and thus they do not consume much power at normal working state. Among the input control relays, K3, used for discharging capacitors, is also “Form B” reed relay, while K1 and K2 are “Form A (normal open)” relays. (http://www.meder.com) The “HV Control” timing sequence chart is as following. Add[2..0] 0 Ctr_B[7..0] 1 2 3 4 00 0 X 0 00 05 07 06 XX t2 t3 t4 t5 WR t1 t6 t1: initialization t2: HV ramp,>150s t3: HV ON, >20ms t4: HV ON t5: measuring period t6: Switvh off HV >150s Fig. 1.3 Timing sequence chart for HV controller 7 There are five control registers in this module. The function table is as below1: Add0 Add1 Add2 Add3 Add4 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 X X X X X Bit1 Bit0 0=Clear trip symbol 0=K2 open 0=K1 open 1=trip enable 1=K2 close 1=K1 close 0=CH8 close 0=CH7 close 0=CH6 close 0=CH5 close 0=CH4 close 0=CH3 close 0=CH2 close 0=CH1 close 1=CH8 open 1=CH7 open 1=CH6 open 1=CH5 open 1=CH4 open 1=CH3 open 1=CH2 open 1=CH1 open 0=CH16 close 0=CH15 close 0=CH14 close 0=CH13 close 0=CH12 close 0=CH11 close 0=CH10 close 0=CH9 close 1=CH16 open 1=CH15 open 1=CH14 open 1=CH13 open 1=CH12 open 1=CH11 open 1=CH10 open 1=CH9 open 0=CH24 close 0=CH23 close 0=CH22 close 0=CH21 close 0=CH20 close 0=CH19 close 0=CH18 close 0=CH17 close 1=CH24 open 1=CH23 open 1=CH22 open 1=CH21 open 1=CH20 open 1=CH19 open 1=CH18 open 1=CH17 open 0=CH32 close 0=CH31 close 0=CH30 close 0=CH29 close 0=CH28 close 0=CH27 close 0=CH26 close 0=CH25 close 1=CH32 open 1=CH31 open 1=CH30 open 1=CH29 open 1=CH28 open 1=CH27 open 1=CH26 open 1=CH25 open 1.4 Reed Relay 1 2 3 4 A A OU T OU T R85 Vcc 41 B IN Ref S K1 RS349 -18 53 IN R86 DS4 1 D2 B 2 51 0K GREE N 1N 41 48 ON R87 Q1 2N 39 04 1. 5K DGND C IN ON DG ND Vcc IN OU T OU T C ON DG ND C81 Vcc 4. 7uF Title D Size Reed Relay D Nu mb er Revisio n A4 Date: File: 1 2 20 03 -12-1 5 Sheet 3o f 8 C:\Docu men ts and Settings \.. \Reed relay .SCH Drawn DOC By: 3 4 Fig. 1.4 Schematic of the Reed Relay The schematic of the reed relays is shown in Figure 1.4. As is mentioned in section 1.3, all reed relays’ switching voltage must great than 3000V RMS. 1 K3 and CH1~CH32 use “Form B” Reed relays, K1 and K2 use “Form A” relays。 8 2 MUX 2.1 General description MUX implements switching between capacitance and leakage current measurements and multiplexing channels. There are 1024 input channels from 32 HV boards under testing. By writing the registers, either the capacitance of one certain capacitor, or the leakage current of one certain board is output at 'CAPACITANCE' or 'V_ILEAKCAP'. This module also includes the input protection circuits and preamplifiers for the leakage current measurement. 2.2 Specification 2.2.1 I/O specification NAME Description I/O TYPE ADD[0..2] Control registers address Input TTL Ctrl_B[0..7] Control word bus Input TTL WR Control word write enable Input TTL DGND Digital Ground Input GND HVBI[1..1024] HV board channels input Input 0~3V Input GND HV_GND NOTE V_ILEAKCAP Capacitor leakage current output Output 0~15V V_ILEAKBRD HV board leakage current output Output 0~15V CAPACITANCE HV board measurement input Output <3V +15V DC power supply Power +15V Typ:109.7mA Max:225mA -15V Power -15V Typ:86.5mA Max:185.6mA +5V Power +5V Typ: 130.9mA max: 221.4mA -5V Power -5V Typ: 65mA Max: 112mA GND Power GND capacitance 3 2.2.3 Power dissipation typical: 3.923W max: 6.097W 2.3 Schematic 1 2 ILE AKBRD [1.. 32 ] ILE AKBRD [1.. 32 ] HV BI[1.. 10 24 ] AD D[0 ..2 ] A C[1. .10 24 ] C[1. .32 ] HV _G ND AD D[0 ..2 ] AD Dr[0 ..4 ] FS C[1. .32 ] HV _G ND AD D[0 ..4 ] FS Ctrl_B[0 ..7 ] Ctrl_B[0 ..7 ] C[33 ..6 4] HV _G ND C[1. .32 ] HV _G ND DG ND DG ND AD Dr[0 ..4 ] FS +5 V +5 V AD D[0 ..4 ] FS -5V -5V ILE AK1 CAP1 ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[25 7. .28 8 ] HV _G ND +3 V -3V +5 V GN D +1 5V -15 V +1 5V GN D C[65 ..9 6] HV _G ND +1 5V AD Dr[0 ..4 ] FS C[1. .32 ] HV _G ND AD D[0 ..4 ] FS -15 V -15 V CAPA CIT ANCE V_ ILE AKCA P V_ ILE AKBRD CAPA CIT ANCE ILE AK2 CAP2 +3 V -3V +5 V GN D +1 5V -15 V C[28 9. .32 0 ] HV _G ND ILE AK3 CAP3 +3 V -3V +5 V GN D +1 5V -15 V C[32 1. .35 2 ] HV _G ND C[97 ..1 28 ] HV _G ND V_ ILE AKBRD AD Dr[0 ..4 ] FS C[1. .32 ] HV _G ND AD D[0 ..4 ] FS ILE AK4 CAP4 +3 V -3V +5 V GN D +1 5V -15 V C[35 3. .38 4 ] HV _G ND HV _G ND HV _G ND Switch5 Switch.Sch Do c C[12 9. .16 0 ] C[1. .32 ] HV _G ND HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS B Switch6 Switch.Sch Do c C[16 1. .19 2 ] C[1. .32 ] HV _G ND HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS Switch7 Switch.Sch Do c C[19 3. .22 4 ] C[1. .32 ] HV _G ND HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS Switch8 Switch.Sch Do c C[22 5. .25 6 ] C[1. .32 ] HV _G ND HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS +3 V -3V +5 V GN D +1 5V -15 V C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS Switch1 2 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS Switch1 3 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V ILE AK5 CAP5 +3 V -3V +5 V GN D +1 5V -15 V C[38 5. .41 6 ] HV _G ND ILE AK6 CAP6 +3 V -3V +5 V GN D +1 5V -15 V C[41 7. .44 8 ] HV _G ND ILE AK7 CAP7 +3 V -3V +5 V GN D +1 5V -15 V C[44 9. .48 0 ] HV _G ND ILE AK1 3 C[64 1. .67 2 ] CAP1 3 HV _G ND +3 V -3V AD Dr[0 ..4 ] +5 V FS GN D +1 5V -15 V ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V AD D[0 ..4 ] FS Switch1 4 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS Switch1 5 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS Switch2 3 Switch.Sch Do c ILE AK1 5 C[70 5. .73 6 ] C[1. .32 ] CAP1 5 HV _G ND HV _G ND +3 V -3V AD Dr[0 ..4 ] AD D[0 ..4 ] +5 V FS FS GN D +1 5V -15 V ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V AD D[0 ..4 ] FS Switch1 6 Switch.Sch Do c ILE AK8 CAP8 +3 V -3V +5 V GN D +1 5V -15 V ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[48 1. .51 2 ] HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS Switch2 2 Switch.Sch Do c ILE AK1 4 C[67 3. .70 4 ] C[1. .32 ] CAP1 4 HV _G ND HV _G ND +3 V -3V AD Dr[0 ..4 ] AD D[0 ..4 ] +5 V FS FS GN D +1 5V -15 V ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V AD D[0 ..4 ] FS C[1. .32 ] HV _G ND ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V ILE AK1 7 CAP1 7 +3 V -3V +5 V GN D +1 5V -15 V C[76 9. .80 0 ] HV _G ND ILE AK1 8 CAP1 8 +3 V -3V +5 V GN D +1 5V -15 V C[80 1. .83 2 ] HV _G ND ILE AK1 9 CAP1 9 +3 V -3V +5 V GN D +1 5V -15 V C[83 3. .86 4 ] HV _G ND ILE AK2 0 CAP2 0 +3 V -3V +5 V GN D +1 5V -15 V C[86 5. .89 6 ] HV _G ND ILE AK1 6 C[73 7. .76 8 ] CAP1 6 HV _G ND +3 V -3V AD Dr[0 ..4 ] +5 V FS GN D +1 5V -15 V ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V AD D[0 ..4 ] FS C[1. .32 ] HV _G ND AD D[0 ..4 ] FS C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V ILE AK2 5 CAP2 5 +3 V -3V +5 V GN D +1 5V -15 V 7 8 AD Dr[5 ..9 ] C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V ILE AK2 6 CAP2 6 +3 V -3V +5 V GN D +1 5V -15 V Switch2 7 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V ILE AK2 7 CAP2 7 +3 V -3V +5 V GN D +1 5V -15 V Switch2 8 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V ILE AK2 8 CAP2 8 +3 V -3V +5 V GN D +1 5V -15 V +1 5V S1 A0 S2 A1 S3 A2 S4 A3 S5 A4 S6 S7 CS S8 WR S9 EN S10 S11 D S12 S13 VD D1 S14 VD D2 S15 VSS S16 GN D S17 S18 S19 S20 S21 S22 S23 S24 S25 S26 S27 S28 S29 S30 S31 S32 AD Dr5 AD Dr6 AD Dr7 AD Dr8 AD Dr9 GN D FS 43 CAPA CIT ANCE +5 V GN D -15 V ILE AK2 1 CAP2 1 +3 V -3V +5 V GN D +1 5V -15 V C[89 7. .92 8 ] HV _G ND ILE AK2 2 CAP2 2 +3 V -3V +5 V GN D +1 5V -15 V C[92 9. .96 0 ] HV _G ND ILE AK2 3 CAP2 3 +3 V -3V +5 V GN D +1 5V -15 V C[96 1. .99 2 ] HV _G ND C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V V_ ILE AK1 7 V_ ILE AK1 8 V_ ILE AK1 9 V_ ILE AK2 0 V_ ILE AK2 1 V_ ILE AK2 2 V_ ILE AK2 3 V_ ILE AK2 4 V_ ILE AK2 5 V_ ILE AK2 6 V_ ILE AK2 7 V_ ILE AK2 8 V_ ILE AK2 9 V_ ILE AK3 0 V_ ILE AK3 1 V_ ILE AK3 2 Repeat(p re_amp ,1, 32 ) p re_ amp.SCH DO C ILE AK[1 ..3 2] Switch2 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V ILE AK3 0 CAP3 0 +3 V -3V +5 V GN D +1 5V -15 V ILE AK HV _G ND +1 5V GN D -15 V +5 V -5V 27 VD D EN S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15 S16 A0 A1 A2 A3 VE E NC NC NC D GN D 18 2 1 17 16 15 14 AD Dr9 AD Dr5 DM 7 4A ADLS04 Dr6 BSJ AD Dr7 AD Dr8 A 2 3 13 28 1 2 GN D U2 2 +1 5V AD 73 2 ILE AK2 9 CAP2 9 +3 V -3V +5 V GN D +1 5V -15 V 19 20 21 22 23 24 25 26 11 10 9 8 7 6 5 4 DG 40 6CW I Switch2 9 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V 1 V_ ILE AK1 V_ ILE AK2 V_ ILE AK3 V_ ILE AK4 V_ ILE AK5 V_ ILE AK6 V_ ILE AK7 V_ ILE AK8 V_ ILE AK9 V_ ILE AK1 0 V_ ILE AK1 1 V_ ILE AK1 2 V_ ILE AK1 3 V_ ILE AK1 4 V_ ILE AK1 5 V_ ILE AK1 6 AD Dr[5 ..9 ] U1 6A U2 1 U2 0 CAP1 CAP2 CAP3 CAP4 CAP5 CAP6 CAP7 CAP8 CAP9 CAP1 0 CAP1 1 CAP1 2 CAP1 3 CAP1 4 CAP1 5 CAP1 6 CAP1 7 CAP1 8 CAP1 9 CAP2 0 CAP2 1 CAP2 2 CAP2 3 CAP2 4 CAP2 5 CAP2 6 CAP2 7 CAP2 8 CAP2 9 CAP3 0 CAP3 1 CAP3 2 Switch2 6 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V Repeat(ILE AK ) Repeat(V _ILE AK ) HV _G ND 1 19 20 21 22 23 24 25 26 11 10 9 8 7 6 5 4 V_ ILE AK V_ ILE AK[1 ..3 2] -15 V 27 VD D EN S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15 S16 A0 A1 A2 A3 VE E NC NC NC D GN D 18 AD Dr9 17 16 15 14 AD Dr5 AD Dr6 AD Dr7 AD Dr8 V_ ILE AKCA P 2 3 13 28 B 1 2 GN D DG 40 6CW I +1 5V GN D -15 V +5 V -5V Switch1 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS Switch2 4 Switch.Sch Do c C[1. .32 ] HV _G ND 6 Switch2 5 Switch.Sch Do c Switch2 1 Switch.Sch Do c C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS AD D[0 ..4 ] FS Switch2 0 Switch.Sch Do c ILE AK1 2 C[60 9. .64 0 ] C[1. .32 ] CAP1 2 HV _G ND HV _G ND +3 V -3V AD Dr[0 ..4 ] AD D[0 ..4 ] +5 V FS FS GN D +1 5V -15 V ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V AD D[0 ..4 ] FS C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS Switch1 9 Switch.Sch Do c ILE AK1 1 C[57 7. .60 8 ] C[1. .32 ] CAP1 1 HV _G ND HV _G ND +3 V -3V AD Dr[0 ..4 ] AD D[0 ..4 ] +5 V FS FS GN D +1 5V -15 V ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V AD D[0 ..4 ] FS C[51 3. .54 4 ] HV _G ND Switch1 8 Switch.Sch Do c ILE AK1 0 C[54 5. .57 6 ] C[1. .32 ] CAP1 0 HV _G ND HV _G ND +3 V -3V AD Dr[0 ..4 ] AD D[0 ..4 ] +5 V FS FS GN D +1 5V -15 V ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V AD D[0 ..4 ] FS Switch1 1 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V Switch4 Switch.Sch Do c V_ ILE AKCA P ILE AK9 CAP9 ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V AD D[0 ..4 ] FS Switch1 0 Switch.Sch Do c ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V 5 Switch1 7 Switch.Sch Do c C[1. .32 ] HV _G ND AD Dr[0 ..4 ] FS Switch3 Switch.Sch Do c GN D 4 Switch9 Switch.Sch Do c Switch2 Switch.Sch Do c WR WR 3 Switch1 Switch.Sch Do c AD D[0 ..4 ] FS ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V ILE AK3 1 CAP3 1 +3 V -3V +5 V GN D +1 5V -15 V ILE AK2 4 CAP2 4 +3 V -3V +5 V GN D +1 5V -15 V ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V C[99 3. .10 2 4] HV _G ND AD Dr[0 ..4 ] FS C[1. .32 ] HV _G ND AD D[0 ..4 ] FS ILE AK CAPA CIT ANCE +3 V -3V +5 V GN D +1 5V -15 V 1 ILE AK3 2 CAP3 2 +3 V -3V +5 V GN D +1 5V -15 V -15 V C 27 VD D EN S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15 S16 A0 A1 A2 A3 VE E AD Dr[5 ..9 ] U1 6A U3 1 +1 5V V_ ILE AKBRD 1 1 9 V_ ILE AKBRD 2 2 0 V_ ILE AKBRD 3 2 1 V_ ILE AKBRD 4 2 2 V_ ILE AKBRD 5 2 3 V_ ILE AKBRD 6 2 4 V_ ILE AKBRD 7 2 5 V_ ILE AKBRD 8 2 6 V_ ILE AKBRD 9 1 1 V_ ILE AKBRD 10 1 0 V_ ILE AKBRD 11 9 V_ ILE AKBRD 12 8 V_ ILE AKBRD 13 7 V_ ILE AKBRD 14 6 V_ ILE AKBRD 15 5 V_ ILE AKBRD 16 4 Switch2 Switch.Sch Do c NC NC NC D GN D 18 2 1 17 16 15 14 AD Dr9 AD Dr5 DM 7 4A LS04 BSJ AD Dr6 AD Dr7 AD Dr8 2 3 13 28 1 2 GN D C DG 40 6CW I B[6. .7] Ad d[0 ..2 ] U1 9 Ad d0 Ad d1 Ad d2 1 2 3 R72 +5 V A B C 6 4 5 4 .7K DG ND U1 7 OE 1 OE 2A OE 2B 15 14 13 12 11 10 9 7 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 B6 B7 B6 WR 1 11 Ctrl_B0 Ctrl_B1 Ctrl_B2 Ctrl_B3 Ctrl_B4 Ctrl_B5 Ctrl_B6 Ctrl_B7 3 4 7 8 13 14 17 18 SN7 4L S1 3 8D U1 8 B7 WR OE CLK D1 D2 D3 D4 D5 D6 D7 D8 2 AD Dr0 5 AD Dr1 6 AD Dr2 9 AD Dr3 1 2 AD Dr4 15 16 19 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Ctrl_B0 Ctrl_B1 Ctrl_B2 Ctrl_B3 Ctrl_B4 Ctrl_B5 Ctrl_B6 Ctrl_B7 1 11 OE CLK 3 4 7 8 13 14 17 18 D1 D2 D3 D4 D5 D6 D7 D8 Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 2 AD Dr5 5 AD Dr6 6 AD Dr7 9 AD Dr8 1 2 AD Dr9 1 5 FS 16 19 U3 2 +1 5V AD Dr[0 ..4 ] DM 7 4S3 74 WM DM 7 4S3 74 WM Ctrl_B[0 ..7 ] VCC +5 V C39 C40 C41 C42 C43 C48 C49 C50 C51 C52 .0 1u F .0 1u F .0 1u F .0 1u F .0 1u F 1 uF 1 uF 1 uF 1 uF 1 uF Repeat(p re_amp _b rd,1 ,3 2) p re_ amp.SCH DO C GN D ILE AKBRD [1.. 32 ] DG ND R73 10 +1 5V GN D U2 3 GN D -5V C53 C54 C44 C45 1 uF 1 uF .0 1u F .0 1u F C56 C57 C46 C47 U2 4 GN D IN OU T SHD N SET R68 1 0K +5 V GN D +3 V -3V R74 2 00 K M AX 17 35 C58 1 uF -15 V 1 uF 1 uF .0 1u F .0 1u F C55 1 uF C60 4 .7u F ILE AKBRD HV _G ND +1 5V GN D -15 V +5 V -5V R67 1 0K D 1 AD Dr[5 ..9 ] Repeat(ILE AK BRD)Repeat(V _ILE AK BRD) HV _G ND V_ ILE AKBRD 17 1 9 V_ ILE AKBRD 18 2 0 V_ ILE AKBRD 19 2 1 V_ ILE AKBRD 20 2 2 V_ ILE AKBRD 21 2 3 V_ ILE AKBRD 22 2 4 V_ ILE AKBRD 23 2 5 V_ ILE AKBRD 24 2 6 V_ ILE AKBRD 25 1 1 V_ ILE AKBRD 26 1 0 V_ ILE AKBRD 27 9 V_ ILE AKBRD 28 8 V_ ILE AKBRD 29 7 V_ ILE AKBRD 30 6 V_ ILE AKBRD 31 5 V_ ILE AKBRD 32 4 V_ ILE AKBRD V_ ILE AKBRD [1.. 32 ] -15 V 27 VD D EN S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15 S16 A0 A1 A2 A3 VE E D GN D AD Dr9 17 16 15 14 AD Dr5 AD Dr6 AD Dr7 AD Dr8 V_ ILE AKCBRD 2 3 13 28 1 2 GN D DG 40 6CW I +1 5V GN D -15 V +5 V -5V D IN POK GN D SHD N OU T FB M AX 88 80 R69 R70 1K 1K GN D R71 1 00 K C59 NC NC NC 18 Title MUX GN D Size 1 uF 1 Nu mber Revisio n A2 Date: File: 2 3 4 5 6 2 00 3-12 -16 Sheet 4o f C:\Do cuments and Settin gs\..\M UX .SCHDODraw C n By: 7 8 8 Fig. 2.1 Schematic of MUX ILEAKBRD[1..32] Preamp [1..32] Multiplexer V_ILEAKBRD Switch[1..32] ileak_cap[1..32] 1 Preamp [1..32] Multiplexer V_ILEAKCAP HVBI[1..1024] 32 Capacitance[1..32] Multiplexer Multiplexer CAPACITANCE 5 Control word[0..7] Address[0..2] Control registers 5 WR Fig. 2.2 Block Diagram of MUX 10 The module MUX has a large number of input channels, 1024+32 in total. To cut down on circuit and cost, multiplexers and switches are employed. The same as HV Controller module, it is that this module also have two registers, ADD5 and ADD6, use the same bus with the HV Controller module and others. The register ADD5 corresponds with channel address on each HV board, and the ADD6 is used to select different board and test mode. The function table is as below: Add5 Bit7 Bit6 Bit5 X X X Bit4 Bit3 Bit2 Bit1 Bit0 Channel address on one HV board ADDr4 Add6 ADDr2 ADDr1 ADDr0 HV board address 0=capacitance mode X ADDr3 X 1=leakage mode ADDr9 ADDr8 ADDr7 ADDr6 ADDr5 There are 32 SWITCH modules in this module, which sum up leakage of all 32 capacitors of one HV board in the “leakage mode”. The module SWITCH connects with one pre_amp. Thirty-two pre_amps output through one multiplexer. In the “capacitance mode”, the module SWITCH selects each single capacitor of one HV board, according to the register ADD5. Then, all 32 capacitance test channels from 32 SWITCH modules multiplex one channel by one multiplexer. Both of the two multiplexers select different HV board according to the “HV board address” in the register Add6. Besides we mentioned above, there are two voltage supplies, +/-3V, in this module, which are used for supplying clamp reference of the module SWITCH. Positions of these modules in Fig. 2.3.1 are listed as following: SWITCH : A2~C5 Control registers : C2~C5 Pre_amp : D5~D6 Multiplexer : A7~D7 +/-3V supplies : D2~D4 2.4 Switch 2.4.1 General description The module SWITCH belong to MUX, there are 32 SWITCH modules in total in each MUX module. This module sum all 32 channels leakage current for each HV board, and select channel for capacitance mode (FS=0). The MUX module input protection also is implemented in the SWITCH module. 11 2.4.2 Specification 2.4.2.1 I/O specification NAME Description I/O TYPE NOTE C[1..32] HV board channel input Input 0~3V ILEAK HV board leakage current output Output 0~1.5mA CAPACITANCE HV board capacitance output Output <3V ADD[0..4] HV board channel address Input TTL FS Measurement mode Input TTL 1/0=leakage/capacitance +3V Power supply Power +3V Max:3mA -3V Power -3V +5V Power +5V Typ:20uA Max: 24uA +15V Power +15V Typ:0.72mA Max:2mA -15V Power -15V Typ:1uA Max:0.8mA GND Power GND 2.5.2.3 Power dissipation typical: 10.9mW max: 42.1mW 12 2.4.3 Schematic 1 2 4 5 6 7 8 C[1. .32 ] C[1. .32 ] A 3 ILE AK ILE AK HV _G ND +3 V +3 V U2 9 +3 V IN1 IN2 IN3 IN4 IN5 IN6 IN7 IN8 IN9 IN1 0 IN1 1 IN1 2 IN1 3 IN1 4 IN1 5 IN1 6 IN1 7 IN1 8 IN1 9 IN2 0 IN2 1 IN2 2 IN2 3 IN2 4 IN2 5 IN2 6 IN2 7 IN2 8 IN2 9 IN3 0 IN3 1 IN3 2 HV _G ND D3 A BAV 19 9W D3 B BAV 19 9W D4 A BAV 19 9W D4 B BAV 19 9W D5 A BAV 19 9W D5 B BAV 19 9W D6 A BAV 19 9W D6 B BAV 19 9W U3 0 C1 C2 C3 C4 FS1 D7 A BAV 19 9W D7 B BAV 19 9W D8 A BAV 19 9W U3 1 IN1 IN2 IN3 IN4 S1 S2 S3 S4 D8 B BAV 19 9W ILE AK O1 O2 O3 O4 GN D NC V+ V- C32 C31 C30 C29 GN D +1 5V -15 V FS3 D9 A BAV 19 9W M AX 32 7 D9 B BAV 19 9W D1 0A BAV 19 9W -3V -3V +3 V D1 1A BAV 19 9W D1 1B BAV 19 9W D1 2A BAV 19 9W D1 0B BAV 19 9W D1 3A BAV 19 9W D1 3B BAV 19 9W D1 4A BAV 19 9W D1 6B BAV 19 9W ILE AK O1 O2 O3 O4 GN D NC V+ V- D1 4B BAV 19 9W C28 C27 C26 C25 +1 5V -15 V FS3 D1 7A BAV 19 9W M AX 32 7 D1 7B BAV 19 9W D1 8A BAV 19 9W D2 0A BAV 19 9W D1 8B BAV 19 9W IN1 IN2 IN3 IN4 S1 S2 S3 S4 A AD D[0 ..4 ] GN D FS 43 FS CAPA CIT ANCE +5 V CAPA CIT ANCE +5 V GN D GN D AD 73 2 O1 O2 O3 O4 GN D NC V+ V- ILE AK GN D B +1 5V -15 V M AX 32 7 -3V +3 V D1 9B BAV 19 9W +1 5V -15 V -3V GN D -3V D1 9A BAV 19 9W GN D U3 3 IN1 IN2 IN3 IN4 S1 S2 S3 S4 FS1 D1 6A BAV 19 9W ILE AK M AX 32 7 U3 2 C5 C6 C7 C8 D1 5B BAV 19 9W O1 O2 O3 O4 GN D NC V+ V- +3 V D1 2B BAV 19 9W B D1 5A BAV 19 9W IN1 IN2 IN3 IN4 S1 S2 S3 S4 AD D[0 ..4 ] AD D0 AD D1 AD D2 AD D3 AD D4 S1 A0 S2 A1 S3 A2 S4 A3 S5 A4 S6 S7 CS S8 WR S9 EN S10 S11 D S12 S13 VD D1 S14 VD D2 S15 VSS S16 GN D S17 S18 S19 S20 S21 S22 S23 S24 S25 S26 S27 S28 S29 S30 S31 S32 +3 V D2 0B BAV 19 9W D2 1A BAV 19 9W D2 1B BAV 19 9W D2 2A BAV 19 9W D2 2B BAV 19 9W U3 8 U3 4 C9 C10 C11 C12 FS2 D2 3A BAV 19 9W D2 3B BAV 19 9W D2 4A BAV 19 9W D2 4B BAV 19 9W 1 4 10 13 U3 5 IN1 IN2 IN3 IN4 S1 S2 S3 S4 ILE AK O1 O2 O3 O4 GN D NC V+ V- C24 C23 C22 C21 GN D +1 5V -15 V FS4 D2 5A BAV 19 9W M AX 32 7 D2 5B BAV 19 9W D2 6A BAV 19 9W D2 6B BAV 19 9W IN1 IN2 IN3 IN4 S1 S2 S3 S4 O1 O2 O3 O4 GN D NC V+ V- ILE AK +5 V R88 1 0K FS GN D +1 5V -15 V 2 5 9 12 GN D 7 M AX 32 7 OE 1 OE 2 OE 3 OE 4 A1 A2 A3 A4 1 4 +5 V VCC 3 FS1 6 FS2 8 FS3 1 1 FS4 Y1 Y2 Y3 Y4 GN D DM 7 4L S12 6AM -3V -3V +3 V C D2 7A BAV 19 9W D2 7B BAV 19 9W D2 8A BAV 19 9W +3 V D2 8B BAV 19 9W D2 9A BAV 19 9W D2 9B BAV 19 9W D3 0A BAV 19 9W C D3 0B BAV 19 9W U3 6 C13 C14 C15 C16 FS2 D3 1A BAV 19 9W D3 1B BAV 19 9W D3 2A BAV 19 9W U3 7 IN1 IN2 IN3 IN4 S1 S2 S3 S4 D3 2B BAV 19 9W ILE AK O1 O2 O3 O4 GN D NC V+ V- C20 C19 C18 C17 GN D +1 5V -15 V FS4 D3 3A BAV 19 9W M AX 32 7 D3 3B BAV 19 9W D3 4A BAV 19 9W -3V +5 V HV _G ND R89 GN D +1 5V C10 0 1 uF C82 .0 1u F C10 1 1 uF D3 4B BAV 19 9W IN1 IN2 IN3 IN4 S1 S2 S3 S4 O1 O2 O3 O4 GN D NC V+ V- ILE AK GN D +1 5V -15 V M AX 32 7 -3V +1 5V C83 .0 1u F C10 2 1 uF C10 3 1 uF C10 4 1 uF C10 5 1 uF C10 6 1 uF C10 7 1 uF C10 8 1 uF C10 9 1 uF C84 .0 1u F C85 .0 1u F C86 .0 1u F C87 .0 1u F C88 .0 1u F C89 .0 1u F C90 .0 1u F C91 .0 1u F C11 0 1 uF C11 1 1 uF C11 2 1 uF C11 3 1 uF C11 4 1 uF C11 5 1 uF C11 6 1 uF C11 7 1 uF C92 .0 1u F C93 .0 1u F C94 .0 1u F C95 .0 1u F C96 .0 1u F C97 .0 1u F C98 .0 1u F C99 .0 1u F 10 D D -15 V -15 V Title Size Switch Nu mber Revisio n A2 Date: File: 1 2 3 4 5 6 7 2 00 3-12 -15 Sheet 5o f C:\Do cuments and Settin gs\..\Switch.SchD oc Draw n By: 8 8 Fig. 2.3 Schematic of Switch sub-module HV Board Channel In [1..32] protection 32 Leakage current Switch Multiplexer Capacitance Test mode select Channel address[0..4] 5 Fig. 2.4 Block diagram of Switch sub-module The module SWITCH located in the inner of the module MUX. It consists of a “protection”, a “Switch” and a “Multiplexer” block. The functional block “protection” employs 64 low leakage diode packages and one +/-3V reference. The “Test mode select” determine whether all 32 input channels switch to leakage or not. The “MUX” is used for multiplexing the following capacitance test circuit. By the given “Channel address on one board”, the “MUX” will switch the corresponding channel to test state. 13 2.5 Pre_amp 1 2 3 4 A A GN D R93 4. 7K R97 2K R98 47 K R96 13 12 R90 1M 4 11 EX T/CL K IN +V INT /CLK OUT EX T CLK B EX TCLK A 1 2 20 K +15 V +5V ILE AK 5 1M R92 1M C12 8 HV _GN D HV _GN D 3 6 10 nF -5V 7 6 R94 V_ ILEA K Repeat(V _ILE AK) 3 5 4. 7K 14 IN/EXT NC(GU ARD) NC(GU ARD) CLM -V RTN CL K B 4 R91 U3 9 8 OP1 77FS 2 C12 7 10 0n F 10 Repeat(IL EAK) B 1 C12 6 10 0n F 7 U4 0 C12 9 22 uF 9 8 -15 V GN D ICL76 50 CSD C +15 V +15 V HV _GN D +5V R95 GN D C11 8 1u F C11 9 0. 01u F C12 2 1u F C12 3 0. 01u F +5V C C12 0 1u F C12 1 0. 01u F C12 4 1u F C12 5 0. 01u F 10 GN D -15 V -15 V -5V -5V Title D Size Pre_amp D Nu mb er Revisio n A4 Date: File: 1 2 3 20 03 -12-1 5 Sheet 6o f C:\Docu men ts and Settings \.. \pre_ amp .SCH DOC Drawn By: 8 4 Fig2.5 Schematic of Preamplifier The pre_amp module converts the leakage current into voltage, and amplifies it to proper range. The gain of the amplifier could be adjusted by near 10 times. 14 3 Capacitor 3.1 General description The module CAPACITOR is used for measuring HV board channel’s capacitance. It simply uses two comparators to implement timing measurement. The time difference of the VCAP1’s (VSQUARE) and the VCAP2’s rise edges represent the capacitance of the HV board channel under testing. And both comparators reference level is supplied by the simple long time constant RC circuit instead of the precise voltage reference. This module use single +5V power supply. 3.2 Specification 3.2.1 I/O specification PARAMETER SYMBOL TYPE NOTE Timing pulse input VSQUARE TTL Typical width: ~380us DGND DGND VCAP1 TTL VCAP2 TTL Test pulse output CAPACITANCE <3V Power supply +5V +5V GND GND Timing pulse output Typ:0.7mA Max:1.4mA 3.2.2 Accuracy Design requirement: <1pf It’s up to following time measurement circuit in MCU. To obtain accuracy 1pf, the following timing measurement circuit’s accuracy must be better than 1us. User should calibrate each channel before using this tester. 3.2.3 Power dissipation typical: 3.5mW max: 7mW 15 3.3 Schematic 1 2 3 4 A A VSQU ARE VCAP1 U1 R1 CAPACITA NCE 1. 3M GN D B OU TA VCC INA - OU TB INA + INBGN D INB+ +5V VCAP2 B M AX9 10 7 C1 .0 1uF C3 .1 uF R2 GN D R3 1M HV _GN D HV _GN D C2 .0 1uF R4 +5V +5V 63 0K C4 .1 uF GN D 0 GN D R5 0 DG ND C C Title D Size Capacitor D Nu mb er Revisio n A4 Date: File: 1 2 20 03 -12-1 5 Sheet 7 of C:\Docu men ts and Settings \.. \Capacitor.SCHD Drawn OC By: 3 8 4 Fig. 3.1 Schematic of Capacitor Test timing pulse comparator1 Delay timing pulse1 HV board under testing Voltage reference comparator2 Delay timing pulse2 Fig. 3.2 Block diagram of Capacitor The module “CAPACITOR” is used for measuring the capacitance of the capacitor embedded HV board. One voltage reference is employed to adjust the compare voltage for comparators. MCU send the timing test pulse to comparator1, comparator1 will output a fine square pulse to one capacitor embedded HV board, via one 1.3 Meg Ohm serial resistor and send one timing pulse VCAP1 to MCU. The serial resistor connect to comparator2 , comparator will output delayed 16 timing pulse . This delay, in other words, time interval of timing pulses, is relative to capacitance. To ensure 1pf accuracy, the following time measurement accuracy must be better than 1us. In the other hand, we can adjust the voltage reference to obtain the best accuracy. The typical reference voltage is 2.7V. The varistor, used for adjusting the voltage reference, lies in B3 in the Figure. 3.3. In addition, it should be placed on the front panel when layout. Wave forms in the Figure. 3.3 as followers: Fig. 3.3 Simulation results of capacitance measurement 3.4 Caution Ensure the voltage at the point called CAPACITANCE, at B1 in the Figure 3.3, is not exceeding 3V at all, otherwise protection circuit could be activated. You could decrease the width of test timing pulse to make it right. 17 4 Monitor 4.1 General description This module is used to switch several monitor outputs, which comprise temperature, humidity, HV voltage, HV current and HV trip thresholds. The same bus as HV controller is used in it. This module also supplies the power for pt100 and s6000 sensors. It use +/5V and +/-15V DC power supply. The VMON is the buffered analog output. 4.2 Specification 4.2.1 I/O specification PARAMETER SYMBOL TYPE NOTE Control registers address ADD[0..2] TTL Control word bus Ctrl_B[0..7] TTL Control word write enable WR TTL Digital Ground DGND DGND Temperature monitor TEMPERATURE 0~1V Humidity monitor RH 0~1V HV voltage monitor HV_VINPUTMON 0~1V HV current monitor HV_IMON 0~1V HV voltage trip threshold HV_VTRIP 0~1V HV current trip threshold HV_ITRIP 0~1V Monitor output VMON 0~10V Power supply +15V +15V Typ:2.8mA Max:5.5mA -15V -15V Typ:2.7mA Max:5mA +5V +5V Typ:33.3mA Max:55mA GND GND 4.2.2 Accuracy 4.2.3 Power dissipation 18 typical: 249mW max: 432.5mW 4.3 Schematic 1 2 3 4 U2 5 19 20 21 22 23 24 25 26 11 10 9 8 7 6 5 4 51 K C61 1u F R83 V_ RH 51 K C62 1u F HV _IM ON C63 1u F -15 V27 B VD D EN S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11 S12 S13 S14 S15 S16 A0 A1 A2 A3 +5V A 4. 7K 17 16 15 14 A0 A1 A2 A3 -15 V R76 2 3 13 NC NC NC 5 U2 6 OP1 77FS 6 3 1K 2 VM ON 8 1 +15 V 28 D VE E HV _VM ON R78 18 4 R82 V_ temperatu re 7 +15 V 1 A R84 20 K 12 GN D B DG 406 CWI C64 1u F GN D R77 R75 1K 10 K C65 HV _ITRIP 15 0p F C66 1u F +15 V -15 V HV _VT RIP C79 1u F C67 1u F GN D C68 1u F +5V C69 1u F C70 1u F C71 1u F DG ND C72 1u F C73 1u F C74 0. 1uF C75 0. 1uF C76 0. 1uF C77 0. 1uF C78 0. 1uF C C U2 7 U2 8 AD D0 AD D1 AD D2 AD D[0.. 2] Ctrl_B[0..7 ] WR DG ND AD D[0.. 2] Ctrl_B[0..7 ] WR DG ND +15 V -15 V +5V +15 V -15 V +5V +5V 1 2 3 R79 4. 7K R80 6 4 5 4. 7K DG ND 8 R81 10 A B C OE 1 OE 2A OE 2B GN D VCC Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 16 +5V WR 1 11 15 14 13 12 11 10 9 7 Ctrl_B0 Ctrl_B1 Ctrl_B2 Ctrl_B3 Ctrl_B4 Ctrl_B5 Ctrl_B6 Ctrl_B7 3 4 7 8 13 14 17 18 DG ND 10 74 AC13 8SC GN D GN D 20 OE VCC CLK D0 D1 D2 D3 D4 D5 D6 D7 2 5 6 9 12 15 16 19 O0 O1 O2 O3 O4 O5 O6 O7 +5V A0 A1 A2 A3 GN D 74 ACQ3 74 SC Title D V_ pt100 su pply V_ s6 000 su pply Monitor D +5V Size Nu mb er Revisio n A4 Date: File: 1 2 20 03 -12-1 5 Sheet 8o f C:\Docu men ts and Settings \.. \M on ito r.SCH DOC Drawn By: 3 8 4 Fig. 4.1 Schematic of Monitor Vtripped Itripped Humidity sensor Humidity sensor HV current monitor HV voltage monitor Control word[0..7] Address[0..2] Control registers Monitor output mux buffer 4 WR Fig 4.2 Block diagram of Monitor The module MONITOR is one of the simplest modules, it just implements that six monitor inputs via multiplexer and buffer connect to the following circuit. The buffer can set different amplification times to suit the following input. The “Control registers” is a register named ADD7, 18 and its address is 07. The same bus, which comes from the MCU, as other modules, it is used for updating the register, for selecting the corresponding monitor. The function table is as following: Bit7 Bit6 Bit5 Bit4 X X X X Bit3 Bit2 Bit1 Bit0 Monitor address Add7 A3 A2 A1 A0 Only six channels is used in this module, user can connects other ten monitors. This module also supplies DC power for Pt100 and S6000 sensors. We can find all these functional blocks in the Fig. 4.3.1. mux : A2~B2 buffer : A3~B3 control registers : C2~D3 19 5 MCU 5.1 General description 5.2 Specifications 5.2.1 I/O specification NAME Description I/O TYPE NOTE ADD[0..2] Control register address Output TTL Ctrl[0..7] Control word bus Output TTL WR Control word write enable Output TTL INT HV tripped interrupt Input TTL 1=HV tripped V_ILEAKCAP Leakage current of cap Input analog 0-10V, need 10bit ADC V_ILEAKBRD Leakage current of board Input analog 0-10V, need 10bit ADC VSQUARE for capacitance meas. Output TTL VCAP1 start signal for time counting Input TTL VCAP2 end signal for time counting Input TTL VMON Monitor signal Input analog DGND GND Output GND RS232 RS232 interface I/O digital Power Power Power Power 0-10V, need 10bit ADC DB-9 * Data transfer speed: 640bps (Leakage current meas.) / 1024xlengthof(counter) bps 5.2.2 Accuracy 5.2.3 Power dissipation 5.3 Schematic 5.4 Caution 5 6 Power 6.1 General description 6.2 Specifications 6.2.1 I/O specification NAME Description I/O TYPE NOTE +15V +15V power supply Power DC Typ. 372.5mA Max. 3110.5mA -15V -15V power supply Power DC Typ. 89.2mA Max. 190.6mA +5V +5V power supply Power DC Typ. 341.1mA Max. 551.5mA -5V -5V power supply Power DC Typ. 65mA Max. 112mA GND GND Power DC Power1,2 Tester Power Supply Power AC AC220,50Hz Power Consumption of MCU part excluded, Need Upgrade!!! 6.2.2 Accuracy 6.2.3 Power dissipation Typ:8.956W Max: 52.834W Power Consumption of MCU part excluded, Need Upgrade!!! 21 6.3 Schematic 6.4 Caution 16 7 Accessories: Motherboard, Cabling, and Connectors 7.1 Motherboard 7.2 Cabling 7.3 Connectors 17