VLSI array processing syllabus

advertisement

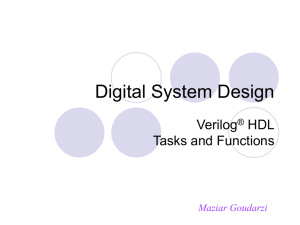

國立中興大學 電機工程研究所碩士專班 超大型積體電路訊號處理架構 課程簡介 (2013, Fall) 一、授課老師 黃穎聰 e-mail:hwangyt@dragon.nchu.edu.tw course web site: http:// socdsp.ee.nchu.edu.tw 二、上課時間 Monday 06:20PM~9:00PM EE201 三、課程內容介紹 This course is designed to give you a comprehensive coverage of the VLSI architecture designs with emphasis on digital signal processing applications. The lecture materials are divided into three major parts, i.e. DSP algorithms, DSP architecture design and hardware description language (HDL). HDL part serves as fundamentals of modern digital IC designs. Computer simulation homework assignments will be given along with the HDL lectures. The DSP architecture design issues will be addressed only after sufficient HDL backgrounds are gained. The basics of DSP will be taught and various architecture design techniques will be elaborated. The detailed contents of this course include Part 1. DSP algorithms introduction to VLSI digital signal processing (ch 1) basics of DSP algorithms (ch 2,3) Part 2. Advanced HDL coding advanced Verilog coding Verilog coding versus synthesis RTL coding guidelines Part 3. DSP Architecture Designs pipelining and parallel processing (ch 4) retiming (ch 5) unfolding and folding (ch 6,7) basics of FPGA (ch 8) FIR filter design example (ch 9) 四、課程要求 The grading of this course is based on homework assignments, labs and exams. 1 1. Homework assignments There are two types of homework assignments, that is, regular - this is the ordinary written homework assignment, mostly from the problems of the textbook simulation - you will be asked to use Verilog to simulate and verify small design 2. Exams Midterm exam – This will cover the HDL materials Final exam – This will cover the DSP architecture materials 五、評分標準 (tentative) homework assignments 40% 30% mid-term exam 30% final exam 六、教科書 “ Verilog HDL – a guide to digital design and synthesis,” 2nd Edition, by Samir Palnitkar, Prentice Hall, 2003 (全華圖書) “VLSI Digital Signal Processing Systems – Design Implementation,” by Keshab Parhi, John Wiley & Sons, 1999 and 七、上課講義 The lecture note (in .pdf format) can be downloaded from the SOC DSP Lab web page prior to each lecture. A password (VDSP2013N) will be required to access the materials. 2