Specification - the GMU ECE Department

advertisement

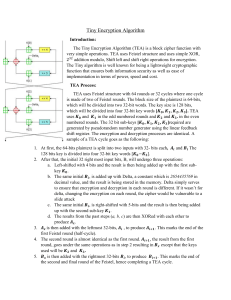

Hardware Implementation of TEA (Tiny Encryption Algorithm) Anoop Kumar Palvai Final Project specifications: Aim: TEA is a cryptographic algorithm designed to minimize the memory footprint and maximize the speed. It is a feistel type cipher which uses operations from mixed (orthogonal) algebraic groups. This project presents the implementation of the Tiny Encryption Algorithm (TEA) in hardware using VHDL. Introduction: Many symmetric block ciphers have been presented in recent years. The TEA is a compromise for safety, ease of implementation, lack of specialized tables, and reasonable performance. The motivation of this project is to implement the algorithm in hardware using the language VHDL. Algorithm to be implemented: The Tiny Encryption Algorithm is a Feistel type cipher that uses operations from mixed (orthogonal) algebraic groups. A dual shift causes all bits of the data and key to be mixed repeatedly. The key schedule algorithm is simple; the 128-bit key K is split into four 32-bit blocks K = (K [0], K [1], K [2], K [3]). TEA seems to be highly resistant to differential cryptanalysis and achieves complete diffusion (where a one bit difference in the plaintext will cause approximately 32 bit differences in the cipher text). Time performance on a workstation is very impressive. Inputs and Outputs: The input to the system will be 64 bits of plain text/cipher text and 128 bit key. The output of the system is a 64 bit encrypted cipher of the original plaintext or decrypted plaintext. Languages and Tools to be used: This project involves coding of the Encryption and Decryption routines of TEA in VHDL language with target implementation on FPGA.The tools used to implement the routines are Aldec active VHDL, VHDL test bench. Evaluation of module: Evaluation of the module will be done by calculating the time taken for the generation of cipher text. Simulation Experiments: Comparing the intermediate results of the code and the output of the device and verify whether the device is functioning according to the design. Possible Areas of Change: Target implementation of the code, Simulator in use, Testing the functionality and performance of the circuits. Mile Stone Chart: September 26th: Submission of initial project specifications. Selection of the modules and tools used to implement. October 3rd: Final project specification, submission by E-mail. October 10th: Thorough with the algorithm and VHDL. October 17th, 1st progress report: Implementing the algorithm for encryption. November 7th: Implementing the algorithm for decryption. November 14th, 2nd progress report: Testing and optimizing the code. December 5th, final progress report: Performance evaluation based on the speed and power. Draft version of the final PowerPoint presentation December 19th, in the time of submission: Detailed documentation of the project and presentation complying with requirements. Contents of final report: 1. Abstract 2. Introduction 4. Explanation of the algorithm 5. Implementation of the algorithm 6. Results 7. Conclusion 8. Future work 9. References References: 1. David J. Wheeler. Roger M. Needham, “TEA, a Tiny Encryption Algorithm”. www.cix.co.uk/~klockstone/tea.pdf. 2. Vikram Reddy Andem, “A Cryptanalysis of Tiny Encryption Algorithm”. www.cs.ua.edu/SecurityResearchGroup/VRAndem 3. Wikipedia, “Description of Tiny Encryption Algorithm, XTEA & Block TEA”. www.en.wikipedia.org/wiki/Tiny_Encryption_Algorithm 4. Dukjae Moon, Kyugdeok Hwang, Wonil Lee, Sangjin Lee, and Jongim Lim, “Impossible Differential cryptanalysis of reduced round XTEA and TEA”. www.portal.acm.org/citation.cfm?id=741090&dl=ACM&coll=&CFID=15151515&CFTOKEN= 6184618 5. Simon Sheperd, “A description, with source code, of the high-speed TEA cipher algorithm”. www.simonshepherd.supanet.com/tea.htm 6. David Wheeler, Roger Needham, “Extended Tiny Encryption Algorithm: article”. This paper addresses some minor flaws in the original TEA. www.angelcode.com/refdb/category/52.asp 7. Feistel. H. (1973, May), “Cryptography and computer privacy”. Scientific American.