Supplementary Material_Revised

advertisement

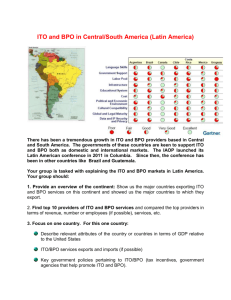

Supplementary material for Trap characterization of silicon nitride thin films by a modified trap spectroscopy technique Kousik Midya1a), Subhabrata Dhar2 and Anil Kottantharayil1 1 Department of Electrical Engineering, 2Department of Physics; Indian Institute of Technology Bombay, Mumbai-400076, India. Email address: kmidya@iitb.ac.in, anilkg@ee.iitb.ac.in In this section, different experimental results supplementary to those presented in the paper are provided. ITO is not a commonly used material as gate electrode. The discussion starts with the comparison of performance of ITO as gate electrode with other standard materials. Then, trap spectroscopy measurement with ITO/TiN gate is discussed, where thin TiN layer is used as diffusion barrier. The experiment is performed to examine whether trap levels in the silicon nitride layer, found in our study, are inherent in nitride layer or introduced by the ITO. ITO/TiN is less transparent than ITO. Detrapping efficiency of ITO and ITO/TiN gate electrode are compared. We also present the result of photo-IV experiment performed on Si/Si3N4/ITO structure to demonstrate that the charges are distributed in the bulk of the nitride. I. Electrical characterization of Si3N4 layer with different metal gates to verify influence of ITO on nitride layer: Metal-Nitride-Semiconductor (MNS) structure was used for characterization. TiN is widely used as a metal diffusion barrier in CMOS technology. We have introduced a thin (10nm) TiN layer between dielectric and ITO to verify the influence of ITO on electrical characteristic of underlying Si3N4 layer. TiN was deposited by reactive sputtering at 350 W with Ar : N2 = 20 sccm: 20sscm. ITO was deposited by RF sputtering at a power of 60W with substrate temperature of 400C. The devices were compared with Al gated devices, in which the Al was deposited by thermal evaporation system. Comparisons of current – voltage (IV) characteristics for three different gates are shown in Fig. A. Breakdown voltages are comparable for all cases. Leakage current has been improved significantly for ITO gate with respect to Al gate, whereas no difference is seen between the ITO/TiN and Al gates. Fig. A. IV characteristics for silicon nitride thin film with Al, ITO/TiN, ITO as gate electrode. CV graph for all the cases is shown in the inset. The inset shows the capacitance – voltage (CV) graph for all the three cases. A slight fluctuation of the Cmax (∆Cmax~0.01 µF/cm2) value is well within the error bar associated with the estimation of the device area. Work function of Al, TiN and ITO have been considered as 4.1eV, 4.6eV1) and 4.5eV2) respectively. The difference in VFB for CVs (~0.57V) with Al and ITO/TiN gate is almost equal to the work function difference between Al and TiN (~0.5eV). Breakdown field (calculated from IV measurement), Dit, Qox(calculated from CV measurement) are listed in the table A. Table A: Parameters extracted from electrical measurement for different gate materials Gate material Al ITO ITO/TiN Breakdown field (MV/cm) 7.8 7.7 8.9 11 11 Dit (cm-2eV-1) 2 10 1.1 1011 3.9 10 QOX (cm-2) 1.5 1012 1.2 1012 1.4 1012 From these results it can be concluded that the ITO, ITO/TiN and Al gates are comparable in terms of their influence on the nitride. Note that, Al gate is very widely used as a gate dielectric in MOS devices for fundamental studies. II. Trap spectroscopy measurement of Si3N4 layer with ITO/TiN gate stack: Additionally, trap spectroscopy experiment was performed with ITO/TiN gate stack to find out whether the gate structure has any influence on the trap characteristics of silicon nitride. The transmission spectra of ITO/TiN showed lower transmittance for this stack compared to ITO alone. Fig. B: Flat band voltage as a function of excitation energy after 30 minutes of illumination with 10 nm TiN/80 nm ITO gate stack. In trap spectroscopy experiment it has been observed that with the introduction of TiN layer, the saturation time is increased from 12 minute to 1hr. For this experiment we have scanned excitation energy from 0.4 eV to 1.6 eV with 0.1 eV increments. Device was excited for 30 minute at each photon energy. The result is described in the Fig. B. It is observed that photon energy causing shift in VFB is almost matching with the experiments reported in the manuscript using ITO as the gate. Major trap levels are again observed at 0.5 eV and 1.1 eV. So, it can be concluded that trap levels in nitride layers are intrinsic property of Si3N4 and not introduced by ITO layer. III Comparison of detrapping transient for ITO and ITO/TiN gate: The presence of a prominent trap level at energy 0.5 eV has already been observed in nitride layer. Fig C: Detrapping transient for ITO and ITO/TiN gate at excitation energy 0.5 eV. To compare the detrapping efficiency for ITO and ITO/TiN gate, shift in flat band voltage of the programmed device was monitored as a function of illumination time for excitation energy 0.5eV. The result is shown in the Fig. C. The result shows, shift in VFB almost saturates after 12 min for ITO gate. But, for ITO/TiN gate saturation occurs after around 60 min. IV. Photo-IV measurement to estimate physical distribution of charge in the nitride film: Purpose of this work was to find the energy position of the trap and to obtain a gross measure of trap density lying in LPCVD silicon nitride thin film in Si/Si3N4/ITO structure. It is well documented that traps in the silicon nitride film is not positioned only at Si/dielectric interface, but distributed in the bulk of the film3,4). Moreover to estimate the location of the charge centroid in nitride layer used in our study, photo-IV measurements were carried out following the method by R. F. DeKeersmaecker and D. J. DiMaria5). In this work they studied trapping and detrapping characteristics of As+ doped SiO2 layer, embedded in Al(semitransparent)-SiO2-Si structure, by CV and photo-IV measurements. To measure photo-current in their MOSCap structure (Si-SiO2Al) photon energy of 5 (4.5) eV was used for +ve (-ve) gate bias. For our study, Si/Si3N4/ITO structure has been used to estimate physical distribution of traps in the nitride layer. CBSi3N4VBSi=2.9 eV and CBSi3N4-CBITO=2.3 eV. CB stands for conduction band and VB stands for valance band. Initially photocurrent was measured as a function of positive (negative) gate bias under illumination by 405 nm/3.1 eV (532 nm/2.3 eV) laser. After that, device was programmed by -15 V gate bias for 1 sec. After programming, photocurrent was again measured in same condition as described above. The result is shown in Fig. D. Fig. D: Photocurrent as a function of gate voltage before and after charging of the nitride layer. Programming of the device was done by -15 volt gate bias for 1 sec. For a fixed photocurrent the shift in gate voltage before and after programming can be expressed as VG VGb VGa VG VGb VGa 1 L x Q x and Q where, (+ or -) refers to polarity of the gate voltage, a and b refers to the state before and after charging, Q is the integral of the trapped charge density over the dielectric thickness and x is the position of the trapped charge centroid measured from metal/dielectric interface. From the above expression it’s clear that VG strongly depends on the position of the charge centroid in the dielectric. VG is not sensitive to traps lying at Si3N4/ITO interface and VG is not sensitive to the trap levels lying at Si/Si3N4 interface. So, the significant shift in photocurrent after programming for both positive and negative gate bias clearly indicates that traps in nitride layer are distributed in bulk of the dielectric. References: 1 S. A. Vitale, J. Kedzierski, P. Healey, P. W. Wyatt, and C. L. Keast, IEEE Trans.on Elec. Dev., 58 (2011), 419. 2 Y. Park, V. Choong, Y. Gao, B. R. Hsieh, and C. W. Tang, Appl. Phys. Lett. 68 (1996), 2699. 3 V. J. Kapoor and R. A.Turi: J. Appl. Phys. 52 (1981) 311. 4 M. Naich, G. Rosenman and Y. Roizin, Thin Solid Films 471 (2005) 166. 5 R. F. DeKeersmaecker and D. J. DiMaria: J. Appl. Phys., 51 (1980) 1085.