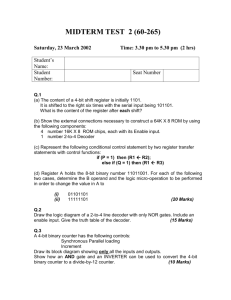

HW #7

advertisement

DOGUS UNIVERSITY Department of Electronics and Communication Engineering ECE 102 Assignment #7 1. Mano 6-6. Design a 4-bit shift register with parallel load using D flip- flops. There are two control inputs: shift and load. When shift = 1, the content of the register is shifted by one position. New data is transferred into the register when load = 1 and shift = 0. If both control inputs are equal to 0, the content of the register does not change. 2. Mano 6-7. Draw the logic dia gram of a 4-bit register with four D flip- flops and four 4 1 multiplexers with mode selection inputs s1and s0. The register operates according to the following function table: s1 0 0 1 1 s0 0 1 0 1 Register Operation No change Complement the four outputs Clear register to 0 (synchronous with the clock) Load parallel data 3. Mano 6-10. Design a serial 2’s complementer with a shifter register and a flipflop. The binary number is shifted out from one side and it’s 2’s complement shifted into the other side of the shift register. 4. Mano 6-13. Show that a BCD ripple counter can be constructed using a 4-bit binary ripple counter with (active low) asynchronous clear and a NAND gate that detects the occurrence of count 1010. 5. Mano 6-17. Design a 4-bit binary synchronous counter with D flip- flops. 6. Mano 6-19. The flip-flop input equations for a BCD counter using T flip-flops are given in section 6-4. Obtain the input equations for a BCD counter that uses (a) JK flip- flops and (b) D flip- flops. Compare the three designs to determine which one is the most efficient. 7. Mano 6-25. It is necessary to generate six repeated timing signals T0 through T5 similar to the ones shown in Fig. 6-17(c). Design the circuit using (a) flip- flops only; (b) a counter and a decoder. 8. Mano 6-27. Design a counter with the following repeated binary sequence: 0, 1, 2, 3, 4, 5, 6. Use JK flip- flops. 9. Mano 6-28. Design a counter with the following repeated binary sequence: 0, 1, 2, 4, 6. Use D flip-flops