Problem 4 (20 points): Floating Point Numbers

advertisement

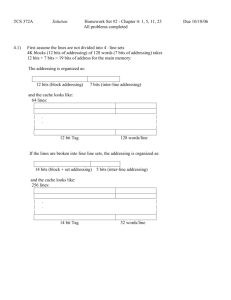

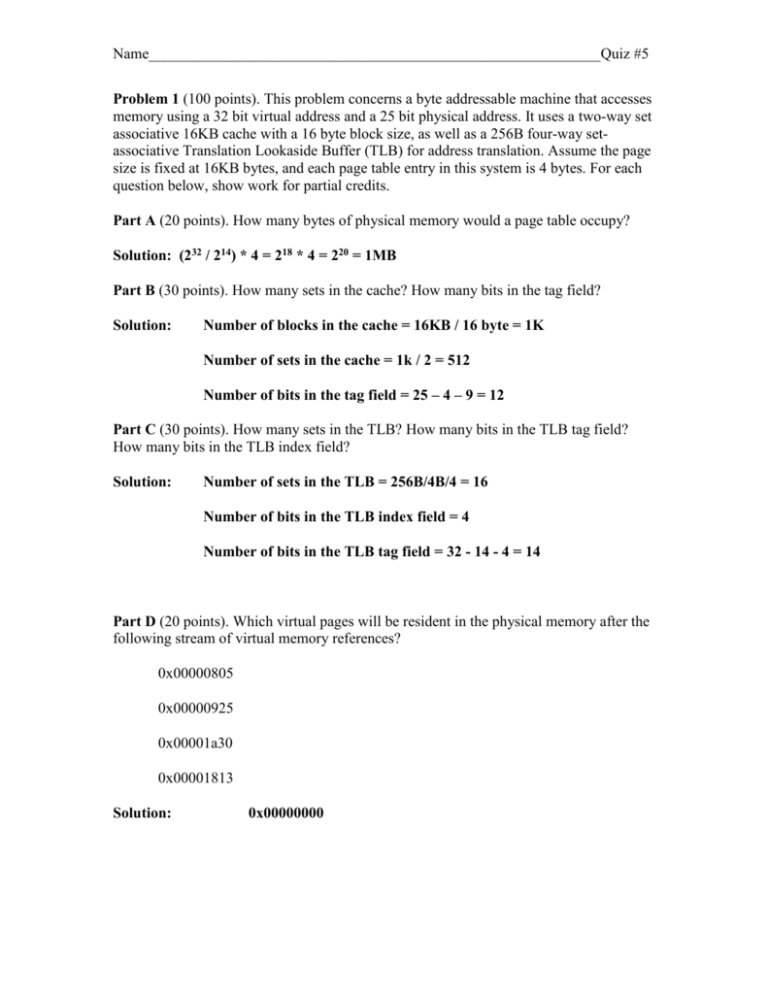

Name____________________________________________________________Quiz #5 Problem 1 (100 points). This problem concerns a byte addressable machine that accesses memory using a 32 bit virtual address and a 25 bit physical address. It uses a two-way set associative 16KB cache with a 16 byte block size, as well as a 256B four-way setassociative Translation Lookaside Buffer (TLB) for address translation. Assume the page size is fixed at 16KB bytes, and each page table entry in this system is 4 bytes. For each question below, show work for partial credits. Part A (20 points). How many bytes of physical memory would a page table occupy? Solution: (232 / 214) * 4 = 218 * 4 = 220 = 1MB Part B (30 points). How many sets in the cache? How many bits in the tag field? Solution: Number of blocks in the cache = 16KB / 16 byte = 1K Number of sets in the cache = 1k / 2 = 512 Number of bits in the tag field = 25 – 4 – 9 = 12 Part C (30 points). How many sets in the TLB? How many bits in the TLB tag field? How many bits in the TLB index field? Solution: Number of sets in the TLB = 256B/4B/4 = 16 Number of bits in the TLB index field = 4 Number of bits in the TLB tag field = 32 - 14 - 4 = 14 Part D (20 points). Which virtual pages will be resident in the physical memory after the following stream of virtual memory references? 0x00000805 0x00000925 0x00001a30 0x00001813 Solution: 0x00000000 Name: ___________________________________________________________Quiz #5 Problem 2 (100 points). Part (a) (20 points): Given below is a series of address references as word addresses. Assuming a direct mapped cache with 16 one-word blocks that is initially empty. Label each reference in the list as a hit or a miss and show the final contents of the cache. Hit or Miss identification Reference 17 9 6 5 43 4 11 9 56 19 1 23 35 Hit (H) or Miss (M) H Final State of the cache: Block Number 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Address 1 35 4 5 6 23 56 9 11 2 Name: ___________________________________________________________Quiz #5 Part (b) (20 points): Using the series of references given in part (a), show the hits or misses and the final state of the direct mapped cache that is initially empty with four words blocks and a total size of 16 words. Hit or Miss identification Reference 17 9 6 5 43 4 11 9 56 19 1 23 35 Hit (H) or Miss (M) M M M H h h h Final State of the cache: Block Number 0 1 2 3 Word 0 32 20 56 - Word 1 33 21 57 - Word 2 34 22 58 - Word 3 35 23 59 - 3 Name: ___________________________________________________________Quiz #5 Part (c) (20 points): For a two-way set associative cache, compute its size in bits given the following specifications: Physical byte address: 40 bits Cache size: 32KB Block size: 2 words (8 bytes) Extra bits: Valid bit and dirty bit Compute the total number of bits required to implement this cache. # of blocks = 32KB / 8B = 4K # of sets = 4k/2 = 2k # of bits for index = 11 # of bits for tag = 40 – 3 – 11 = 26 # of bits within each block = 26 + 2 + 64 = 92 Size of the cache = 92 * 4K = 368 * 1024 Part (d) (20 points): Consider a computer system with the following specifications: Instruction class Integer arithmetic and logic Load Store Branch Floating Point Frequency (%) 40 20 10 10 20 Clock Cycles 5 12 15 5 30 In order to increase the CPU throughput, you decide to add a data cache. The data cache has a 98% hit ratio and a miss penalty of 25 clock cycles for both load and store instructions. The cache access time is 4 clock cycles and 5 clock cycles for load and store instructions respectively including hit detection. Use the average memory access time to calculate the speed up of the CPU with data cache against the CPU without the data cache. No data cache: 5 * 40% + 12 * 20% + 15 * 10% + 5 * 10% + 30 * 20% = 11.9 With data cache: 98% * (4 * 20% + 5 * 10%) + 2% (10% + 20% ) * 25 = 9.924 4 Name: ___________________________________________________________Quiz #5 Part (e) (20 points): A certain computer system has 32-bit words, a virtual address space of 4 GB and a physical address spaces of 512MB. The page size for this system is 8KB. There are 2 status bits: valid and dirty for each entry in the page table. Compute the following: 1. The size of each entry in the page table in bits. 2. The total number of entries in the page table. 3. The size of the page table in bits. Can you map the virtual address 0xB1E45FAC to its physical location in the main memory? 1. Page offset = 13, Physical page number = 29-13 = 16, thus each entry has 16+2 bits. 2. 2 ^ (32 – 13) = 2 ^ (19) 3. 2 ^ (19) * 18 5