lab 5 – linear integrated-circuit phase-locked loop

advertisement

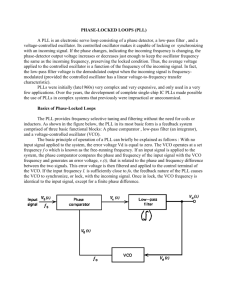

LAB 5 – LINEAR INTEGRATED-CIRCUIT PHASELOCKED LOOP 1. Introduction A phase-locked loop (PLL) is a closed-loop feedback control system in which the feedback signal is a frequency rather than a Voltage. In this experiment, the operation of the XR-2212 phase-locked loop is examined. The XR-2212 is an ultrastable monolithic phase-locked loop system especially designed for data communications and controlsystem applications. See the XR-2122 data sheet for a description of its operation. 2. Materials Required Equipment 111- protoboard dc power supply (+12 V dc) medium-frequency signal generator (1 MHz) 11- standard oscilloscope (10 MHz) assortment of test leads and hookup wire Parts List 1121- XR-2212 phase-locked loop 1 k-Ohm resistor 10 k-Ohm resistors 22 k-Ohm resistor 1123- 100 k-Ohm resistor 0.002 F capacitor 0.01 F capacitor 0.1 F capacitor +12 V dc 1 fi 10 V+ 0.1 F 2 Pre amp 6 7 9 Comp Op amp Det 16 + 15 Internal Reference 8 fo Signal Gen 1K Amp VCO 5 11 0.1 F XR-2212 GND 4 3 13 14 C0* 12 R0* R1 22 K * See the text for the values of R0 and C0. Figure 1. XR-2212 Phase-locked Loop. C1 0.002 F LAB 5 – LINEAR INTEGRATED-CIRCUIT PHASE-LOCKED LOOP 3. Pre-lab Print the XR-2212 data sheet and bring it with you to the lab session. In the Phase-locked Loop Parameters section of the data sheet, find and record the equations for the following: (a) theoretical VCO center frequency, f0, (b) internal reference Voltage, VREF, (c) loop tracking bandwidth, f/f0, (d) phase comparator conversion gain, K, (e) VCO conversion gain, K0, and (f) total loop gain, KT. 4. VCO Operation In this section, we examine the operation of the Voltage-controlled oscillator (VCO) in the XR-2212. 1. Construct the phase-locked loop circuit shown in Figure 1, but don’t connect R1 to pin 12. This opens the loop and allows the VCO to operate at its free-running frequency. 2. Complete the table below for the values shown for R0 and C0. Use the appropriate design equation from the XR-2212 data sheet to calculate the theoretical frequencies. R0 C0 10 k 33 k 10 k 0.01 F 0.01 F 0.1 F Theoretical Frequency, kHz Measured Frequency, kHz Per Cent Difference 3. For the phase-locked loop circuit shown in Figure 1, set R0 = 10 k and Co = 0.01 F. 4. Connect resistor R1 to pin 12 and set the signal-generator output to a 4-Vp-p sine wave. Set the signal generator frequency to the VCO free-running frequency and verify that the VCO is phase-locked to the signal generator. 5. Measure the PLL reference Voltage on pin 11 and compare the measured value to VREF calculated from the XR-2212 design equation. 6. Measure the phase comparator output Voltage (Vd) on pin 10 and compare it to the measured and theoretical Voltages found in step 5. (Since the VCO is operating at its free-running frequency, we expect these to be close.) 5. Loop Acquisition, Pull-in Range, and Hold-in Range In this section we examine the loop acquisition, pull-in ranger, and hold-in range of a phase-locked loop and these are affected by R1 and C1. Loop acquisition is the process the PLL undergoes when it locks onto an external input frequency. The PLL is said to be locked when the VCO output frequency equals the external input frequency. The pull-in range is that range of input frequencies over which the PLL will acquire lock. The peakto-peak pull-in range is often called the capture range. The lowest frequency at which lock will occur is called the lower capture frequency, and the highest frequency at which lock will occur is called the upper capture frequency. The hold-in range is the peak range 2 LAB 5 – LINEAR INTEGRATED-CIRCUIT PHASE-LOCKED LOOP of input frequencies over which the PLL will remain locked onto once lock has occurred. The peak-to-peak hold-in range is often called the lock range. The lowest frequency to which the PLL will track is called the lower lock limit, and the highest frequency to which the PLL will track is called the upper lock limit. The difference between the upper and lower lock limits is called the loop tracking bandwidth. 1. For the phase-locked loop circuit shown in Figure 1, set R0 = 10 k and Co = 0.01 F. 2. Set the signal-generator output to a 4-Vp-p sine wave. Set the signal generator frequency to the VCO free-running frequency and verify that the VCO is phaselocked to the signal generator. 3. Measure the lower capture frequency (fcl) as follows. (1) Decrease the signal generator frequency until the VCO loses lock. (2) Slowly increase the signal generator frequency, while observing both the VCO output signal and the signal generator output signal, until lock occurs. (Be careful here, because the VCO will also lock onto fi/2, 2fi/3, 3fi/2, 2fi, etc. Throughout this lab you are looking for the frequencies where the VCO locks into fi.) (3) Repeat (1) and (2) until you are sure you have found the lowest frequency where lock occurs. 4. Measure the upper capture frequency (fcu) as follows. (1) Increase the signal generator frequency until the VCO loses lock. (2) Slowly decrease the signal generator frequency, while observing both the VCO output signal and the signal generator output signal, until lock occurs. (3) Repeat (1) and (2) until you are sure you have found the highest frequency where lock occurs. 5. Measure the lower lock limit (fll) as follows. (1) Set the signal generator frequency so that the PLL is locked. (2) Slowly decrease the signal generator frequency, while observing both the VCO output signal and the signal generator output signal, until the PLL loses lock. (3) Repeat (1) and (2) until you are sure you have found the lowest frequency to which the PLL will track. 6. Measure the upper lock limit (flu) as follows. (1) Set the signal generator frequency so that the PLL is locked. (2) Slowly increase the signal generator frequency, while observing both the VCO output signal and the signal generator output signal, until the PLL loses lock. (3) Repeat (1) and (2) until you are sure you have found the highest frequency to which the PLL will track. 7. Determine the loop-tracking bandwidth using the following formula: f Bt fn where f = flu - fll (Hertz) fn = VCO free-running frequency (Hertz) 8. Compare the loop-tracking bandwidth measured in step 7 to the theoretical value calculated from the XR-2122 design equations. 9. Replace R1 with a 100-k resistor and repeat steps 3 through 8. 3 LAB 5 – LINEAR INTEGRATED-CIRCUIT PHASE-LOCKED LOOP 10. Restore R1 to 22 k, replace C1 with a 0.01 F capacitor, and repeat steps 3 through 8. 6. Phase Comparator and VCO Conversion Gains In this section we examine the conversion gains for the XR-2212’s phase comparator and VCO. The VCO conversion gain (ko) is the change in VCO output frequency per unit of Voltage change at the VCO input. (i.e., ko = f/V). The phase comparator conversion gain (k) is the change in the phase-comparator output Voltage per unit of phase difference (error) at the phase-comparator input (i.e., k = V/). When the external input frequency is equal to the VCO free-running frequency, there is a 90° phase difference them. This 90° phase difference is called the bias or offset phase. For input frequencies above and below the VCO free-running frequency, the phase difference between the input frequency and the VCO output frequency varies proportionately. This shift in phase from the 90° offset is the phase error (e). e produces a Voltage at the phase comparator output (Vd). Vd is coupled back to the VCO input, where it causes the VCO output frequency to shift until it equals the external input frequency. 1. For the phase-locked loop circuit shown in Figure 1, set R0 = 10 k, C0 = 0.01 F, R1 = 22 k, and C1 = 0.002 F. 2. Set the signal-generator output to a 4-Vp-p sine wave. Set the signal generator frequency to the VCO free-running frequency and verify that the VCO is phaselocked to the signal generator. 3. Vary the signal generator frequency in 1-kHz steps over the PLL tracking range. At each frequency record the resulting values of Vd and the phase difference, e, between the signal generator sine wave output and the VCO square wave output, using an oscilloscope. (Some lab scopes can calculate phase. If yours can’t, measure the time difference, td, and calculate the phase = tdf360 degrees, where td is the time difference in seconds and f is the frequency in Hz. It is convenient to have Excel calculate this for you.) 4. Using Excel, plot the frequencies found in step 3 vs. Vd, and fit a straight line to f these points. The slope of this line is the VCO conversion gain, kO . (Excel V has a regression tool to find the slope, see the note, “Linear Regression,” on the ECET 314 CD-ROM. Unfortunately, the lab computers don’t have this tool, but you may be able to use it on your own PC. Without the regression, you can identify a straight-line section of the characteristic on your Excel plot and use points at the extremes of this section.) Compare this value to the theoretical one from the XR-2212 design equations. 5. Using Excel, plot values of Vd vs. the phase differences, and fit a straight line to V these points. The slope of the line is the phase detector conversion gain, k . Compare this value to the theoretical one from the XR-2212 design equations. 4 LAB 5 – LINEAR INTEGRATED-CIRCUIT PHASE-LOCKED LOOP 7. Discussion Questions 1. Which passive components determine the VCO free-running frequency? 2. Which passive components determine the upper and lower lock limits? 3. Which passive components affect the upper and lower capture frequencies? 5