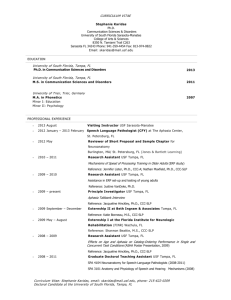

Rama Chander Rao Sriram`s Resume

advertisement

RAMA CHANDER RAO SRIRAM 3708, Dulcinea Blvd, #119, Tampa, FL - 33613 Phone: (813) 389-9402(Cell) E-mail: rsriram@csee.usf.edu Webpage: www.csee.usf.edu/~rsriram Summary Trained and experienced in EDA design tools like Cadence, Synopsys, and Mentor Graphics. Hands on experience in HDL, scripting, and high-level programming languages. Characterization and Design of CMOS Digital and Analog Circuits. Comprehensive understanding of circuit design through research work and a part time job as an instructor for electronics lab. Self-motivated individual with strong leadership and team work skills. Exceptional Presentation, Communication, Organizational skills, and attention to detail. Education Master of Science in Electrical Engineering University of South Florida (USF), Tampa, FL. Jan’03 - Dec’ 05 (expected) Bachelor of Technology in Electrical and Electronics Engineering Kakatiya University, Warangal, India. Jul’ 98 - May’ 02 Technical Expertise Programming Languages: HDL Languages: Assembly Languages: Scripting Languages: EDA Design Tools: Synopsys: Cadence: C, C++, JAVA VHDL, Verilog HDL Intel 8085/8086 Perl, Tcl/Tk Mentor Graphics: Altera: Other: Operating Systems: Applications: Web Design: Avant! HSpice, Nanosim Virtuoso, Analog Artist, NC Launch, NC Verilog 3.2, VerilogXL, Spectre, Orcad PSpice Modelsim MAXPLUS II Agilent ADS, Magic 7.1 UNIX, MS DOS, Windows, Sun Solaris, LINUX Mathcad 12, Matlab Dreamweaver MX 2004, Fireworks, Flash, CSS, ASP, HTML Research Experience The Global Positioning System (GPS) is a world wide radio navigation companion comprised of constellation of 24 satellites and various ground stations. A design feasibility analysis for a single chip GPS receiver for use in compact navigation devices was carried out. My part of analysis comprised of designing an analog front end for a GPS receiver with L1 band application. The analog layout design for front end blocks such as LNA, OpAmp, and A/D Converter was implemented in CMOS technology using MAGIC 7.1 layout tool and simulations were done using Avant! HSpice. The design trade-offs such as noise, power, gain, frequency, supply voltage, and linearity were investigated up. Work Experience College of Arts and Sciences Computing, USF, Tampa, FL Jan’ 03 to Present Computer Lab Technician: Work profile included installation of computers, software upgrades, hardware troubleshooting, and blackboard support. ITC Limited, Bhadrachalam Paperboard Division, India Sept’ 02 to Dec’ 02 Team Member: Worked on development and improvement of paper production machine, and performed a comparative analysis of peer projects with the same objectives. Teaching Experience Teaching Assistant: Electrical Engineering, USF, Tampa, FL Aug’ 05 to Present Aug’ 04 to May’05 Introduction to Electrical Systems: Provide knowledge base of PSpice and other related tools in their projects. Grade assignments, quizzes, and exams Electrical Engineering, USF, Tampa, FL Jan’ 04 to May’ 04 Electronics – II: Helped students with CAD tools, and other electronic design/verification equipment for their projects. Graded assignments, quizzes, and exams. Instructor: Electrical Engineering, USF, Tampa, FL May’ 05 to Aug’05 Electronics Lab: Inculcated research based approach among students by giving them an opportunity to do individual research project. Provided exposure to CAD tools and electronic design/verification equipments. Evaluated very highly by the students. Projects and Papers Layout design using Cadence Virtuoso layout tool followed by HSpice simulations targeted for low power: An 8 - bit synchronous up-counter with parallel load and asynchronous reset capability. An 8 - bit positive edge triggered universal shift register. An 8 - bit Conditional sum and Carry select CMOS adders. VHDL based designs followed by simulations using Altera MAXPLUS-II: A 32-bit carry look ahead and ripple carry adders. A 16-bit conditional sum adder as a hierarchal unit consisting of four 4-bit conditional sum adders that interact through a carry look ahead adder. High-level language based implementations: “Statistical Estimation of Average Power Dissipation in Sequential Circuits” based on distribution-independent power estimation (DIPE) tool for sequential benchmark circuits. A 3-D look-up table based on “Power modeling for high-level power estimation” for various sequential benchmark circuits. Digital solution of short circuit currents in a power system network based on Building algorithm. Survey Paper Presentations per the academic requirement: “Software Power Optimization” that can be done at various levels. “IC Planarization Techniques” emphasizing non-CMP methods. “PC-AT based real time closed loop speed control of a single phase induction motor”. Relevant Coursework Graduate Level: Digital CMOS VLSI Design Low Power VLSI Design VLSI/ULSI Multilevel Interconnection Processes Semiconductor Device Physics I & II Integrated Circuit Processing Statistical Design Models (Design of Experiments) Random Process in Electrical Engineering Undergraduate Level: Digital Circuits and Logic Design Linear Integrated Circuits Electronic Devices and Circuits Microprocessors and their Applications Digital Signal Processing Control Systems Engineering Extra Curricular Activities Special Events Coordinator for Students of India Association (SIA) in USF (2004-05). Organized and ran events which were attended by nearly 600 people including performers and audience. Voted best multi cultural student organization of the year. Web Designer for Intercultural Organization (ICO) in USF (www.ctr.usf.edu/intercul) Vice President of Indian Students for Technical Education (ISTE), local chapter for Kakatiya Institute of Technology and Science (KITS), Warangal, India References Available upon request