Exam1-sol

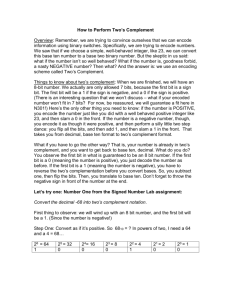

advertisement

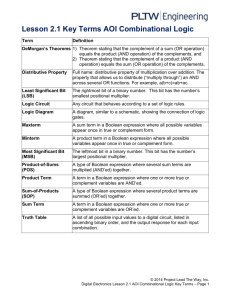

CSE207-Fall 01 Computer Science & Engineering 10/04/2001 Digital Logic Design K. YETONGNON UTEB 352 EXAM 1 Solutions Name _______________________________ Section ____________ Marks Q1 _______/35 Q2 _______/30 Q3 _______/35 Total ________________/ Note: Please answer all the following questions on these sheet (use the backs if necessary). Make sure you show all work. Partial credits can not be given for incorrect answers if solutions or methods are not presented clearly. This is a comprehensive exam that is intended to test skills, knowledge and understanding of the material covered in chapters 2,3 and 4. Good luck. Enjoy! Question 1: Number systems and Codes (Use back of previous page to show work on problems of question #1) 1.1. Convert the following unsigned numbers to the equivalent base 10 numbers a) (110110.1101)2 = 25 + 24 + 22 + 21 + 2-1 + 2-2 + 2-4 = 54.8125 b) (532.142)8 = 5x82 + 3x81 + 2x80 + 1x8-1 + 4x8-2 + 2x8-3 = 346.1914 c) (5CD.3F)16 = 5x162 + 12x161 + 13x160 + 3x16-1 + 15x16-2 = 1485.2375 1.2 Perform the following base r addition a) 10110112 + 00110112 11101102 b) 4567. 728 c) AA2F16 + 564. 238 + 985416 5354 .158 1428316 1.3 Perform the following subtractions using 2 complement a) 10110112 b) - 01110112 - 0 010112 10110112 + 10001012 10100000 0 010002 0010002 (2's complement) 1101012 1111012 (2's complement) 1.4. Representation of signed numbers Convert the following decimals to their equivalent binary representation in signmagnitude, signed 1's complement and signed 2's complement forms. For each form, use 6 bits. Decimal 7 -23 -11 Sign-magnitude 000111 110111 101011 1's complement 000111 101000 110100 2's complement 000111 101001 110101 1.5 Write the decimal equivalent of the following signed numbers using the polynomial expansion method: a) 001110 (1s complement) = _____ 14 ______ 10 b) 1111110 (2s complement) = ______ -2 ______10 c) 10011 (1s complement) = ______-12 _____ 10 d) 001110 (2s complement) = ______ 14 ____ 10 Work a) b) c) d) 23 + 22 + 21 = 14 - (26 ) + 25 + 24 + 23 + 22 + 21 + 0 = -64 + 32 + 16 + 8 + 4 + 2 = -64 +62 = -2 - (24 -1) + 0 +0 + 21 + 20 = -16 + 1 + 2 + 1 = -15 + 2 + 1 = -12 23 + 22 + 21 = 14 Question 2: Boolean algebra 2.1 F = = = = = = = Find the complement F' of corresponding logic circuit. ((BC)'(A + (CD)')')' ((BC)')' + ( (A + (CD)')')' BC + (A + (CD)') BC + A + (CD)' BC + A + C' + D' (B + C')(C + C') + A + D' A + B + C' + D' F = (BC)'(A + (CD)')' and reduce it. Draw the Find the dual expression Fd of the logic expression F A,B,C,D are litterals. 2.2 = BC'(A + CD')' , where F = BC'(A + CD')' = (BC')(A + (CD')' = (B + C') + (A(C + D'))' Given a logic expression F = A,B,C(0,1,2,4,6) 2.3 a) Write the canonical product of sums expression (POS) for the logic expression F F= (A+B+C)(A+B+C')(A+B'+C)(A'+B+C)(A'+B'+C) b) Use a truth table to find the canonical sum of products (SOP) expression for the logic function F = (A + B)C A B C F 0 0 0 0 0 0 1 0 0 0 1 1 0 1 0 1 0 0 0 1 1 0 1 1 0 1 1 1 1 1 1 0 b) Use Boolean algebra to find the canonical sum of products (SOP) expression for the logic function F = (A + B)C. (A+B)C = AC + BC = A(B+B')C + (A+A')BC = ABC + AB'C + ABC + A'B = ABC + AB'C + A'BC Question 3: CLN design (An extra sheet is provided for showing your work) 3.1 Combinational logic circuit Design a combinational logic circuit CLN to compute the sum S = X + Y in base 4 as follows: Input consist of two base 4 digits X and Y. Each digit is encoded by a 2-bit binary number. Output S is a base 4 number (one or more base 4 digits) that represents the sum S=X+Y X S CLN Y a) Complete the following table to display the value of S = X+Y for each input combination X 0 1 2 3 0 0 1 2 3 1 1 2 3 10 2 2 3 10 11 Y S 3 3 10 11 12 b) Discuss how to encode the output S The output consists of two base 4 digits. Each digit can be encoded over 2 binary bits. Four bits are needed to encode the output: s0, s1, s2, s3 Noting that bit S3 is 0, we can also encode the output over 3 bits. 3.2 Write a truth table for the circuit CLN. Rename the input bits from a0 (least significant or rightmost bit) to a3. Label the output bits s0 (least significant or rightmost bit), s1, … a3 a2 a1 a0 s3 s2 s1 s0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 0 0 1 0 0 1 1 0 1 1 0 0 0 1 0 0 0 1 1 0 1 1 1 0 1 0 0 1 0 0 0 0 0 1 0 1 0 0 1 0 0 1 1 1 1 0 0 1 1 0 1 0 1 0 0 0 1 0 1 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 0 1 1 1 1 1 1 0 1 0 0 1 1 0 1 1 0 3.3 a) Derive a canonical sum of products expression for each output variable. S3 = 0 S2 = m7 + m10 + m11 + m13 + m14 + m15 = a3'a2a1a0 + a3a2'a1a0' + a3a2'a1a0 + a3a2a1'a0 + a3a2a1a0' + a3a2a1a0 S1 = m2 + m3 + m5 + m6 + m8 + m9 + m12 + m15 = a3'a2'a1a0' + a3'a2'a1a0 + a3'a2a1'a0 + a3'a2a1a0' + a3a2'a1'a0' + a3a2'a1'a0 + a3a2a1'a0' + a3a2a1a0 S0 = m1 + m3 + m4 + m6 + m9 +m11 + m12 + m14 a3'a2'a1'a0 + a3'a2'a1a0 + a3'a2a1'a0' + a3'a2a1a0' + a3a2'a1'a0 + a3a2'a1a0 + a3a2a1'a0' + a3a2a1a0' 3.3 b) Draw a logic diagram for the output variables found in 3.3.a. Draw diagrams (as drill exercise)……. 3.4 Reduction of logic expression: a) Using Boolean algebra, give a reduced or simplified expression for bit s0 (least significant or rightmost bit) of S. S0 = = = = = a3'a2'a1'a0 + a3'a2'a1a0 + a3'a2a1'a0' + a3'a2a1a0' + a3a2'a1'a0 + a3a2'a1a0 + a3a2a1'a0' + a3a2a1a0' a3'a2'a1'a0 + a3a2'a1'a0 + a3'a2'a1a0 + a3a2'a1a0 + a3'a2a1'a0' + a3a2a1'a0' + a3'a2a1a0' + a3a2a1a0' a1'a0a2'(a3' + a3) + a2'a1a0(a3' + a3) + a2a1'a0'(a3' + a3) + a2a1a0'(a3' + a3) a0a2'(a1' + a1) + a2a0'(a1' + a1) a0a2' + a2a0' = a0 XOR a2 c) Draw logic diagrams for the expression found in 3.4.a) Draw the corresponding circuit