Zhen Fang - University of Utah

advertisement

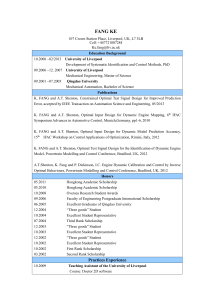

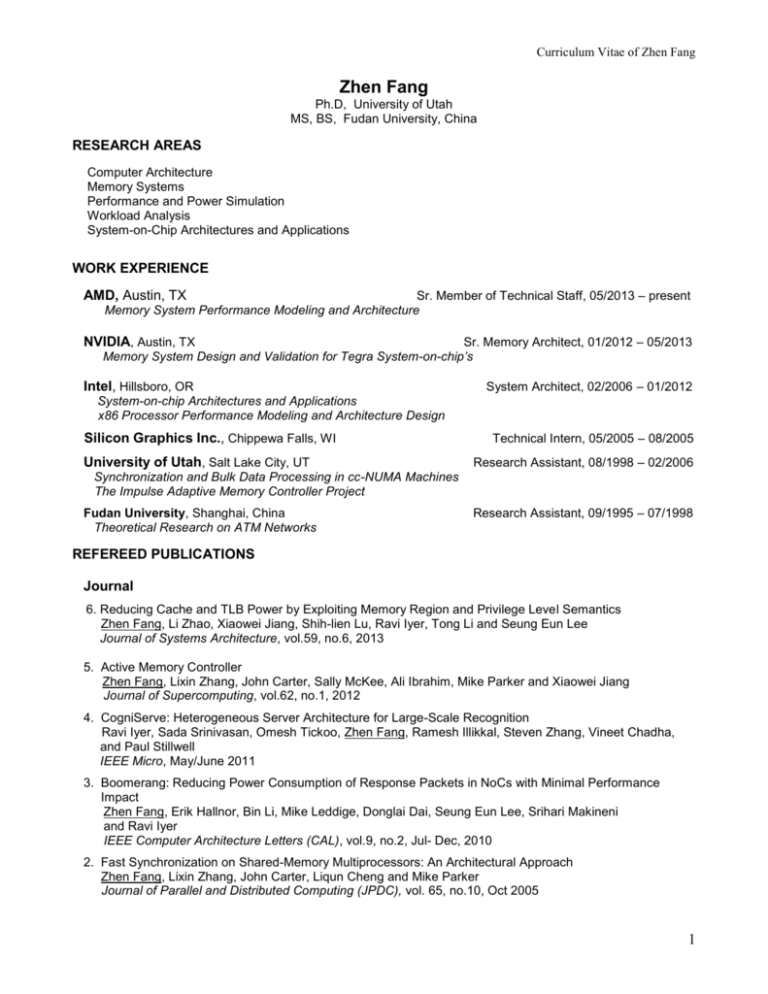

Curriculum Vitae of Zhen Fang Zhen Fang Ph.D, University of Utah MS, BS, Fudan University, China RESEARCH AREAS Computer Architecture Memory Systems Performance and Power Simulation Workload Analysis System-on-Chip Architectures and Applications WORK EXPERIENCE Sr. Member of Technical Staff, 05/2013 – present Memory System Performance Modeling and Architecture AMD, Austin, TX Sr. Memory Architect, 01/2012 – 05/2013 Memory System Design and Validation for Tegra System-on-chip’s NVIDIA, Austin, TX Intel, Hillsboro, OR System Architect, 02/2006 – 01/2012 System-on-chip Architectures and Applications x86 Processor Performance Modeling and Architecture Design Silicon Graphics Inc., Chippewa Falls, WI University of Utah, Salt Lake City, UT Technical Intern, 05/2005 – 08/2005 Research Assistant, 08/1998 – 02/2006 Synchronization and Bulk Data Processing in cc-NUMA Machines The Impulse Adaptive Memory Controller Project Fudan University, Shanghai, China Theoretical Research on ATM Networks Research Assistant, 09/1995 – 07/1998 REFEREED PUBLICATIONS Journal 6. Reducing Cache and TLB Power by Exploiting Memory Region and Privilege Level Semantics Zhen Fang, Li Zhao, Xiaowei Jiang, Shih-lien Lu, Ravi Iyer, Tong Li and Seung Eun Lee Journal of Systems Architecture, vol.59, no.6, 2013 5. Active Memory Controller Zhen Fang, Lixin Zhang, John Carter, Sally McKee, Ali Ibrahim, Mike Parker and Xiaowei Jiang Journal of Supercomputing, vol.62, no.1, 2012 4. CogniServe: Heterogeneous Server Architecture for Large-Scale Recognition Ravi Iyer, Sada Srinivasan, Omesh Tickoo, Zhen Fang, Ramesh Illikkal, Steven Zhang, Vineet Chadha, and Paul Stillwell IEEE Micro, May/June 2011 3. Boomerang: Reducing Power Consumption of Response Packets in NoCs with Minimal Performance Impact Zhen Fang, Erik Hallnor, Bin Li, Mike Leddige, Donglai Dai, Seung Eun Lee, Srihari Makineni and Ravi Iyer IEEE Computer Architecture Letters (CAL), vol.9, no.2, Jul- Dec, 2010 2. Fast Synchronization on Shared-Memory Multiprocessors: An Architectural Approach Zhen Fang, Lixin Zhang, John Carter, Liqun Cheng and Mike Parker Journal of Parallel and Distributed Computing (JPDC), vol. 65, no.10, Oct 2005 1 Curriculum Vitae of Zhen Fang 1. The Impulse Memory Controller Lixin Zhang, Zhen Fang, Mike Parker, Binu Mathew, Lambert Schaelicke, John Carter, Wilson Hsieh, and Sally McKee IEEE Transactions on Computers, vol.50, no.11, Nov 2001 Conference 18. Leveraging Heterogeneity in DRAM Main Memories to Accelerate Critical Word Access Niladrish Chatterjee, Manjunath Shevgoor, Rajeev Balasubramonian, Al Davis, Zhen Fang, Ramesh Illikkal and Ravi Iyer The 45th International Symposium on Microarchitecture (MICRO), 2012 17. Reducing L1 Caches Power By Exploiting Software Semantics Zhen Fang, Li Zhao, Xiaowei Jiang, Shih-lien Lu, Ravi Iyer, Tong Li and Seung Eun Lee International Symposium on Low Power Electronics and Design (ISLPED), 2012 16. A Speech Recognition Engine for Intel SoCs Anthony Chun, Jenny Chang, Zhen Fang, and Ravi Iyer Design & Test Technology Conference (DTTC), 2011 DTTC is Intel’s annual corporate-wide, internal technical conference Best Paper Award (total number of awards: 4, out of 126 presented and 200+ web-only technical papers) 15. Cost-Effectively Offering Private Buffers for SoCs and CMPs Zhen Fang, Li Zhao, Ravi Iyer, Carlos Flores Fajardo, German Fabila Garcia, Seung Eun Lee, Steven King, Xiaowei Jiang and Srihari Makineni The 25th International Conference on Supercomputing (ICS), 2011 14. Buffer-Integrated-Cache: A Cost-Effective SRAM Architecture for Handheld and Embedded Platforms Carlos Flores Fajardo, Zhen Fang, Ravi Iyer, German Fabila Garcia, Seung Eun Lee, and Li Zhao The 48th Design Automation Conference (DAC), 2011 13. ACCESS: Smart Scheduling for Asymmetric CMPs Xiaowei Jiang, Asit Mishra, Li Zhao, Ravi Iyer, Zhen Fang, Sada Srinivasan, Srihari Makineni, Paul Brett and Chita Das The 17th International Symposium on High Performance Computer Architecture (HPCA), 2011 12. Template-based Memory Access Engine for Atom-based SoCs Bin Li, Zhen Fang and Ravi Iyer The 16th Asia and South Pacific Design Automation Conference (ASP-DAC), 2011 Best Paper Award nomination 11. Performance Characterization and Acceleration of Optical Character Recognition on Handheld Platforms Sadagopan Srinivasan, Li Zhao, Lin Sun, Zhen Fang, Peng Li, Tao Wang, Ravi Iyer and Dong Liu IEEE International Symposium on Workload Characterization (IISWC), 2010 10. Using Checksum to Reduce Power Consumption of the Display System for Low-Motion Content Kyungtae Han, Zhen Fang, Paul Diefenbaugh, Richard Forand, Ravi Iyer and Donald Newell International Conference on Computer Design (ICCD), 2009 9. Accelerating Mobile Augmented Reality on a Handheld Platform Seung Eun Lee, Steven Zhang, Zhen Fang, Sadagopan Srinivasan, Ravi Iyer and Donald Newell International Conference on Computer Design (ICCD), 2009 8. Performance Characterization and Optimization of Mobile Augmented Reality on Handheld Platforms Sadagopan Srinivasan, Zhen Fang, Ravi Iyer, Steven Zhang, Mike Espig, Donald Newell, Daniel Cermak, Yi Wu, Igor Kozintsev and Horst Haussecker IEEE International Symposium on Workload Characterization (IISWC), 2009 7. Active Memory Operations Zhen Fang, Lixin Zhang, John Carter, Ali Ibrahim and Mike Parker International Conference on Supercomputing (ICS), 2007 2 Curriculum Vitae of Zhen Fang 6. Highly Efficient Synchronization Based on Active Memory Operations Lixin Zhang, Zhen Fang and John Carter International Parallel and Distributed Processing Symposium (IPDPS), 2004 5. A Low-Power Accelerator for the SPHINX3 Speech Recognition System Binu Mathew, Al Davis and Zhen Fang International Conf. on Compilers, Architecture and Synthesis for Embedded Systems (CASES), 2003 4. MPEG4: Fallacies and Paradoxes Zhen Fang and Sally McKee IEEE 5th Annual Workshop on Workload Characterization (WWC), 2002 3. Reevaluating Dynamic Superpage Promotion with Hardware Support Zhen Fang, Lixin Zhang, John Carter, Wilson Hsieh and Sally McKee The 7th International Symposium on High Performance Computer Architecture (HPCA), 2001 2. Online Superpage Promotion Revisited Zhen Fang, Lixin Zhang, John Carter, Sally McKee and Wilson Hsieh International Conf. on Measurement and Modeling of Computer Systems (SIGMETRICS), 2000 1. Prosperity of Non State Sectors and Recession of State-Owned Enterprises in China: A Proper View Jun Wang and Zhen Fang The 28th St. Gallen Symposium, Switzerland, 1998 PATENTS 1. Node Synchronization for Multiprocessor Computer Systems J. Carter, R. Passint, D. Dai, Z. Fang, L. Zhang and G. Thorson. US patent issued. 7,464,115 2. Method and Apparatus for Power Management of a Link Interconnect E. Hallnor, Z. Fang and H. Rotithor US patent issued. 8,090,967 3. Using Criticality Information to Route Cache Coherency Communications Z. Fang, L. Cheng and S. Vangal US patent issued. 8,131,944 4. Fast, User-Level Control of On-Die IO Devices Z. Fang, M. Wagh, J. Ajanovic, M. Espig and R. Iyer US patent issued.8, 225,069 5. A Novel Cacheline Replacement Policy to Optimize HD Video Encoding Z. Fang, E. Hallnor, N. Gupte and S. Zhang US patent issued. 8,316,184 6. Delegating a Poll Operation to Another Device M. Espig, Z. Fang, R. Iyer, and D. Harriman US patent issued. 8,364,862 7. Performance and Traffic Aware Heterogeneous Interconnection Network S. Vangal, N. Borkar and Z. Fang US patent issued. 8,379,659 8. Selective Searching in a Shared Cache L. Cheng, Z. Fang, J. Wilder, S. Srinivasan, R. Iyer and D. Newell US patent issued. 8,412,885 9. Providing Address Range Coherency Capability to a Device Z. Fang, D. Harriman and M. Leddige US and foreign patents pending 10. Automatically Using Superpages for Stack Memory Allocation L. Zhao, Z. Fang, R. Iyer and D. Newell US and foreign patents pending 11. Data Cache Memory Power Reduction Techniques Z. Fang, M. Chinthamani, L. Zhao, M. Kamble, R. Iyer, et. al US patent pending 12. Mechanisms to Reduce Power Consumption of Set-Associative I-Caches and I-TLBs Z. Fang, L. Zhao, R. Iyer, T. Li and D. Newell US patent pending 13. Using Motion Change Detection to Reduce Power Consumption of Display Systems K. Han and Z. Fang US and foreign patents pending 14. Affinity-Aware Direct Cache Access for Receive-Side Packet Processing 3 Curriculum Vitae of Zhen Fang Z. Fang, L. Zhao, S. Makineni, R. Iyer and G. Liao 15. Interrupt Return Instruction with Embedded Interrupt Service Functionality X. Jiang, Z. Fang, S. Makineni, R. Illikkal and R. Iyer US patent pending US patent pending 16. DRAM Compression Scheme to Reduce Power Consumption in Motion Comp. and Display Refresh Z. Fang, N. Gupte and X. Jiang US patent pending 17. Configurable Reduced Instruction Set Core S. Makineni, S. King, Z. Fang, R. Alexander, R. Iyer, et al. US and foreign patents pending 18. Embedded Branch Prediction Unit X. Jiang, S. Makineni, Z. Fang, Dmitri Pavlov and Ravi Iyer US and foreign patents pending 19. Hardware-Assisted Lazy Page Locking X. Jiang, Z. Fang, S. Makineni and R. Iyer US and foreign patents pending 20. Below-VccMin Data Stores for Mobile Platforms Z. Fang, S-L. Lu and R. Iyer US patent pending PERSONAL INFORMATION Email: fangzhen@gmail.com Visa status – China citizenship; US permanent resident 4