Template for Electronic Submission to ACS Journals

advertisement

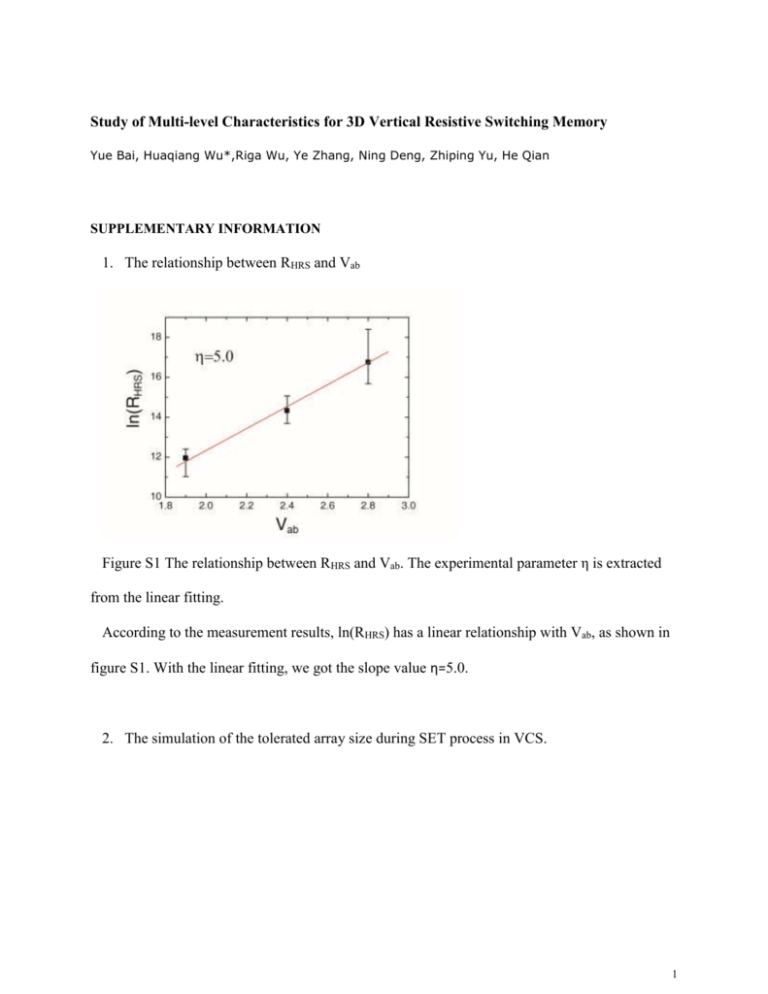

Study of Multi-level Characteristics for 3D Vertical Resistive Switching Memory Yue Bai, Huaqiang Wu*,Riga Wu, Ye Zhang, Ning Deng, Zhiping Yu, He Qian SUPPLEMENTARY INFORMATION 1. The relationship between RHRS and Vab Figure S1 The relationship between RHRS and Vab. The experimental parameter η is extracted from the linear fitting. According to the measurement results, ln(RHRS) has a linear relationship with Vab, as shown in figure S1. With the linear fitting, we got the slope value η=5.0. 2. The simulation of the tolerated array size during SET process in VCS. 1 Figure S2 The Rlevel1 after the set process versus different array size. Level2, level 3 and level 4 is achieved by VCS method. In VCS, the tolerated array size during SET process is simulated as shown in figure 2-1(a). The initial resistances of target cell are 10 MΩ, 1 MΩ and 100 kΩ in level 4, level 3 and level 2 respectively. The other devices have 10 kΩ resistance in the worst cases. In order to achieve level 1, the Ic = 160uA is used. It is shown that the initial resistance of target cell do not have a significant effect on tolerated array size. When we set the 50% resistance deviation, the tolerated array size is more than 104 bits. Furthermore, since level 1 is set in a range from 1 kΩ to 10 kΩ, the tolerated array size can be even larger. Therefore, the constraint of array size during SET process do not change the consequence that “the acceptable array size is more than 104 bits”. 2