Lab 1: Using LTSpice or Multisim for Simulation

advertisement

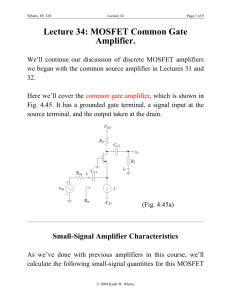

1 Lab 2: Part A NPN Common-Emitter Amplifier (See p. 4 for NMOS Common-Source Amplifier) Notes: 1) The following write-up is identical to Lab 6 in EE 3110-Fall 2014 (http://faculty.weber.edu/snaik/EE3110_labs.htm). You don’t have to include detailed analyses in your report. Please provide a table/summary that shows overall gain GV, and the values for RC & RE for your amplifier. 2) Note that VCC or V+ = 10 V (instead of 15 V as done in Lab 6 in EE3110), IC=0.5 mA (instead of 1mA) and RL= 100 kΩ (instead of 10 kΩ) which changes the original design. Objectives The purpose of this lab is to build an NPN-based common emitter amplifier that amplifies a small AC signal. This circuit will be used in Part B to analyze the frequency response. Fig. 1 NPN Common-Emitter amplifier circuit with coupling capacitors. Design the amplifier to achieve a small-signal gain of at least AV = -200 V/V and IC = 0.5 mA. Use V+=10 V, RSIG = 50 Ω, RL = 100 kΩ, RB1 =80 kΩ, and RB2 = 20 kΩ. Although there will be variations from transistor to transistor, you may assume β=100 in your calculations. Weber State University EE3110 Microelectronics I Suketu Naik 2 Fig. 1 shows an NPN Common-Emitter (Emitter is common between Base and Collector) amplifier circuit. Note that vSIG and RSIG represent the ac signal source and its internal resistance, respectively. For the calculation and simulation purposes, you will include RSIG; however you will omit it in the actual circuit on the breadboard. Also, note that for simulation purposes we will use 2N2222 but in the actual circuit it may change. You may need to adjust values of the other components as necessary in the actual circuit in order to meet the design specifications. Coupling capacitors CB and CL block DC voltages. Here CB blocks DC voltage, which is used to bias the base, from entering the ac signal source. CL blocks DC voltage, which is to bias the collector, from appearing at the load. Ideally if we apply a small ac signal at the base and we should obtain an ac signal at the collector with some amplification. 6.1 DC Analysis: Sketch DC model of the circuit in your lab book. Be sure to replace the three capacitors by open circuit. You can also omit VSIG, RSIG, and RL. What are the values of IB and IE? What is the value of VB? Determine the value of RE that produces vBE (base-emitter voltage drop)=0.7 V. What is VE? Note that at this point we know neither VCE nor RC. L1: Find IB, IE and RE. 6.2 AC (small-signal) Analysis: Sketch small-signal model of the circuit in your lab book. Replace the transistor with its smallsignal model, capacitors with short circuits, and V+ with an AC ground. Assume VA is large, and ignore rO. What would happen to RE? Label the voltage at base of the transistor as vi (with reference to ground). Note that this is the small-signal voltage at the gate. What are the values of gm and rπ. What is the ratio vi /vSIG? L2: Derive the expression for AV = vO /vi . What is the value of RC that produces a smallsignal gain of at least AV= - 200 V/V? What would be the overall gain GV? L3: What is the DC voltage at the collector? Does the transistor operate in active mode with this value? L4: What is the output resistance, Ro? 6.3 Simulation: Simulate your circuit with CG = CL = CS = 47 μF. Note that these values may have to change in the experiment. Use the values of RE and RC as determined by the previous calculations. Use vSIG = 10 mVpk-pk at 1 kHz. There should be no DC voltage at the input. L5: What are DC values: VBE, VCE, IB, IC, and IB? How closely do they match your calculations? Weber State University EE3110 Microelectronics I Suketu Naik 3 L6: What is AV and GV? How closely do they match your calculations? 6.4 Experiment: Assemble the circuit as calculated and simulated on the breadboard. You should not include RSIG because it represents the internal resistance of the function generator. Using the multimeter, measure the DC voltages of your circuit at the base (VB), emitter (VE), and collector (VC) of the transistor. Using the function generator, apply vSIG = 10 mVpk-pk at 1 kHz (if 10 mVpk-pk is not available then use the smallest possible value). Adjust other components as necessary in order to meet the required specification (AVmin = -200 V/V). L6: Generate the plots of vO and vI vs time. L7: What is the measured value of AV and GV? How does it compare with your calculations and simulation? Note that the biggest source of variations from your simulation results will be due to the variation in β. Q1: What is the maximum gain that you can achieve without distorting the output signal? Q2: Increase the input voltage amplitude until you start seeing distortion in the output voltage. Can you optimize the circuit so that the transistor provides the maximum gain without distortion at this value of input voltage? If time permits, measure Ro as follows (it is important to know Ro so that you would know what the next stage or the load sees as the overall amplifier resistance.) Optional: Replace RL with 1 MΩ resistor and repeat the AC measurements. Note the amplitude of the output waveform. Now adjust RL such that the output amplitude is 50% of what it was for 1 MΩ load. This new value of RL is the output resistance Ro. How does it compare with your calculations and simulations? Note that this value of Ro cannot be greater than RC. What is Rin (looking into the base of the transistor)? Weber State University EE3110 Microelectronics I Suketu Naik 4 Lab 2: Part A NMOS Common-Source Amplifier (See p. 1 for NPN Common-Emitter Amplifier) Notes: 1) The following write-up is identical to Lab 5 in EE 3110-Fall 2014 (http://faculty.weber.edu/snaik/EE3110_labs.htm). You don’t have to include detailed analyses in your report. Please provide a table/summary that shows overall gain GV, and the values for RD & RS for your amplifier. 2) Note that VDD = 10 V (instead of 15 V as done in Lab 6 in EE3110), IC=0.5 mA (instead of 1mA) and RL= 100 kΩ (instead of 10 kΩ) which changes the original design. 1. Objectives The purpose of this lab is to create an NMOS-based common source amplifier that amplifies a small AC signal. Fig. 1 NMOS common-source amplifier circuit with coupling capacitors. Fig. 1 shows an NMOS Common-Source (Source is common between Gate and Drain) amplifier circuit. Note that vSIG and RSIG represent the ac signal source and its internal resistance, respectively. For the calculation and simulation purposes, you will include RSIG; however you Weber State University EE3110 Microelectronics I Suketu Naik 5 will omit it in the actual circuit on the breadboard. Also, note that for simulation purposes we will use 2N7002 but in the actual circuit we will be using 2N7000TA.You may need to adjust values of the other components as necessary in the actual circuit in order to meet the design specifications. Coupling capacitors CG and CL block DC voltages. Here CG blocks DC voltage, which is used to bias the gate , from entering the ac signal source. CL blocks DC voltage, which is to bias the drain, from appearing at the load. Ideally if we apply a small ac signal at the gate and we should obtain an ac signal at the drain with some amplification. Design the amplifier to achieve a small-signal gain of at least AV = -5 V/V and ID = 0.5 mA. Use VDD=10 V, kn = 0.7 mA/V2, RSIG = 50 Ω, RL = 100 kΩ, and RG1 = RG2 = 3 MΩ. 5.1 DC Analysis: Follow example 5.10 (please pay attention to the feedback RG which we don’t have). Sketch DC model of the circuit in your lab book. Be sure to replace the three capacitors by open circuit. You can also omit RSIG and RL. What is VG? What is VOV? What is VS? What is the value of gm? gm (transconductance) an important parameter which determines how output current modulates given some input voltage. What is VGS? What is RS? Note that at this point we know neither VDS nor RD. L1: Find VOV, gm, VGS, and RS. 5.2 AC (small-signal) Analysis: We will use the hybrid-π model for the analysis. Follow example 5.10 (please pay attention to the feedback RG which we don’t have). Sketch small-signal model of the circuit in your lab book. Replace the transistor with its smallsignal model, capacitors with short circuits, and VDD with an AC ground. What is rO? (Use VA=70 V). What would happen to RS? Label the voltage at gate of the transistor as vi (with reference to ground). Note that this is the small-signal voltage at the gate. What is the ratio vi /vSIG? L2: Derive the expression for AV = vO /vi . What is the value of RD that produces a smallsignal gain of at least AV= - 5 V/V? Weber State University EE3110 Microelectronics I Suketu Naik 6 L3: What is the DC voltage at the drain? Does the transistor operate in saturation with this value? 5.3 Simulation: Simulate your circuit with CG = CL = CS = 47 μF. Note that these values may have to change in the experiment. Use the values of RD and RS as determined by the previous calculations. Use vSIG = 50 mVpk-pk at 1 kHz. There should be no DC voltage at the input. L4: What are DC values: VGS, VDS, and ID? How closely do they match your calculations? L5: What is AV? How closely does it match your calculations? 5.4 Experiment: Assemble the circuit as calculated and simulated on the breadboard. You should not include RSIG because it represents the internal resistance of the function generator. Using the multimeter, measure the DC voltages of your circuit at the gate (VG), source(VS), and drain (VD) of the transistor. Using the function generator, apply vSIG = 50 mVpk-pk at 1 kHz (if 50 mVpk-pk is not available then use the smallest possible value). Adjust other components as necessary in order to meet the required specification (AVmin = -5 V/V). L6: Generate the plots of vO and vI vs time. L7: What is the measured value of AV and GV? How do they compare with your calculations and simulation? Q1: What is the maximum gain that you can achieve without distorting the output signal? Q2: Increase the input voltage amplitude until you start seeing distortion in the output voltage. Can you optimize the circuit so that the transistor provides the maximum gain without distortion at this value of input voltage? If time permits, measure Ro as follows (it is important to know Ro so that you would know what the next stage or the load sees as the overall amplifier resistance.) Optional: Replace RL with 1 MΩ resistor and repeat the AC measurements. Note the amplitude of the output waveform. Now adjust RL such that the output amplitude is 50% of what it was for 1 MΩ load. This new value of RL is the output resistance Ro. How does it compare with your calculations and simulations? Note that this value of Ro cannot be greater than RD. What is Rin (looking into the gate of the transistor)? Weber State University EE3110 Microelectronics I Suketu Naik