ee201-j11 - School of Electronic Engineering

advertisement

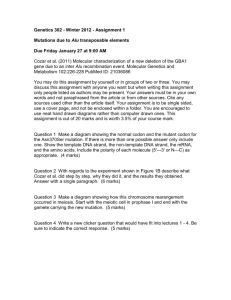

DUBLIN CITY UNIVERSITY SEMESTER TWO EXAMINATIONS 2011 MODULE: Digital Circuits & Systems EE201 (Title & Code) COURSE: BEng BEng BEng BEng YEAR: 2 EXAMINERS: ELECTRONIC ENGINEERING ICE DIGITAL MEDIA ENGINEERING MECHATRONIC ENGINEERING Dr Seán Marlow [x5120] Prof Peter Ashburn Prof T Anderson Prof D Linton Prof Robin Clarke TIME ALLOWED: 2 Hours INSTRUCTIONS: Answer 4 questions [from 5] PLEASE DO NOT TURN OVER THIS PAGE UNTIL YOU ARE INSTRUCTED TO DO SO The use of programmable or text storing calculators is expressly forbidden. Please note that where a candidate answers more than the required number of questions, the examiner will mark all questions attempted and then select the highest scoring ones. ___________________________________________________________________ EE201 PAGE 1 OF 3 Semester Two Examinations 2011 QUESTION 1 [TOTAL MARKS: 25] 1(a) [14 Marks] Draw a logic diagram of a 4-channel, 1-bit Multiplexer and show how it can be used to implement the logic function, F = !A!B!C + ABC, ! = NOT. 1(b) [11 Marks] Design a 3-line to 8-line decoder from only 4-channel demultiplexers. [End of Question 1] QUESTION 2 [TOTAL MARKS: 25] 2(a) [14 Marks] Show two ways to design a 4-bit Adder/Subtractor and explain which you think is best from an environmental point of view. 2(b) [11 Marks] How could your 4-bit Adder/Subtractor, with any other components you wish, be used to design a 4-bit ALU which can perform the ADD, SUBTRACT, NOR and AND operations? [End of Question 2] QUESTION 3 [TOTAL MARKS: 25] 3(a) [10 Marks] Show how the number of states in a synchronous sequential circuit can be reduced. Explain why such a reduction of states may benefit the environment. 3(b) [15 Marks] Design a sequential circuit whose output, Z = 1 only if the input sequence, X = 10010 (overlapping input sequences are allowed). Use D-type Flip-Flops and any logic gates you may need. [End of Question 3] ___________________________________________________________________ EE201 PAGE 2 OF 3 Semester Two Examinations 2011 QUESTION 4 [TOTAL MARKS: 25] 4(a) [11 Marks] How can a 1-bit, 1-word SRAM be built from J-K Flip-Flops and any gates you may need? Explain how you would write data into your SRAM. 4(b) [14 Marks] Show how you could use your 1-bit, 1-word SRAM to build a 2-bit, 4-word SRAM. [End of Question 4] QUESTION 5 [TOTAL MARKS: 25] 5(a) [8 Marks] Draw a NMOS circuit which performs the logic function, F = !(AB+C). 5(b) [9 Marks] Draw a CMOS circuit which performs the logic function, F = !(AB+C). 5(c) [8 Marks] If Ron = 100kΩ for load MOSFETs, Ron = 1kΩ for switching MOSFETs and Roff = 1010 Ω for all MOSFETs, calculate the power dissipated in each circuit in 5a and 5b for A=B=C=1 and VDD = 10 Volts. [End of Question 5] [END OF EXAM] ___________________________________________________________________ EE201 PAGE 3 OF 3 Semester Two Examinations 2011