MCOR_Design_Guidelines

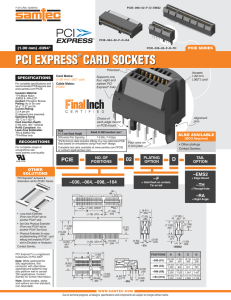

advertisement

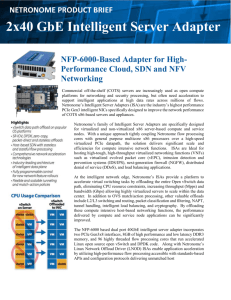

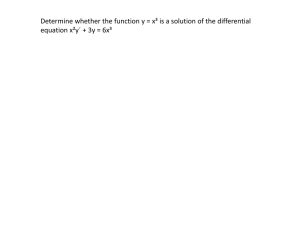

Ans: Please refer to attached PDF [ COMExpressPnP_DG_09.pdf] Section 6 and Section 7. Section-6 is basic layout design considerations and Section-7 highlights the routing considerations for PCIe and LAN signals. I am also attaching COMX-CAR-P1_DG_Rev1.doc . Please refer to Section – 7 for routing considerations. List of PCIe Differential Net names: PCIE_CLK_REF+ PCIE_CLK_REFPCIE_CLK3+ PCIE_CLK3PCIE_TX2+ PCIE_TX2PCIE_RX2+ PCIE_RX2PCIE_CLK1+ PCIE_CLK1PCIE_TX0+ PCIE_TX0PCIE_RX0+ PCIE_RX0PCIE_CLK2+ PCIE_CLK2PCIE_TX1+ PCIE_TX1PCIE_RX1+ PCIE_RX1I have attached a PCIe design guideline document with the email. Also given below are some general rules to be followed when routing PCIe pairs PCIe pairs need to be length-matched within a given pair (intra-pair), but the different pairs do not need to be closely matched (inter-pair).The following items should be observed when routing PCIe signals on the carrier board: Differential Impedance: 85 ohm ± 15% Differential pair-to-pair spacing: minimum 20mils, Differential pair to clock/high speed periodic signals: minimum 50 mils Length matching between differential pairs (intra pair): 5 mils, Differential pair to other signals spacing: minimum 20 mils Ground reference if possible Spacing from differential pair to plane edge: minimum 40 mils, but if the space allowed is bigger, so much the better For the differential pair trace width and spacing, refer the stack up structure and impedance table from PCB vendor. Maximum number of vias is six on each differential signal TX+ and TX- signals should maintain symmetry when changing layers. No tight bend, use two 45° bends instead of 90° routing. Trace length compensation should be added to the short side after each bend. PCI Express layout guidelines List of OTHER Differential Pairs: [LAN] SFP_EVR_CLK+ SFP_EVR_CLKEVR_DIFF_TX+ EVR_DIFF_TXEVR_DIFF_RX+ EVR_DIFF_RXGBE0_MDI3+ GBE0_MDI3GBE0_MDI2+ GBE0_MDI2GBE0_MDI1+ GBE0_MDI1GBE0_MDI0+ GBE0_MDI0NetJ6_11 NetJ6_10 NetJ6_5 NetJ6_4 NetJ6_3 NetJ6_2 NetJ6_8 NetJ6_9 LAN Trace Routing Guidelines There is another signal called the LPC_CLK Layout considerations for LPC _CLK Routing Rules for Single-Ended Interfaces The following is a list of suggestions for designing with single-ended signals. This should help implement these interfaces while providing maximum COM Express carrier board performance. Do not route traces under crystals, crystal oscillators, clock synthesizers, magnetic devices, or ICs that use or generate clocks. Avoid tight bends. When it becomes necessary to turn 90°, use two 45° turns or an arc instead of making a single 90° turn. Stubs on signals should be avoided because stubs will cause signal reflections and affect signal quality. Keep the length of high-speed clock and periodic signal traces that run parallel to high-speed signal lines at a minimum to avoid crosstalk. Based on EMI testing experience, the minimum suggested spacing to clock signals is 50 mil. Route all traces over continuous planes with no interruptions (ground reference preferred). Avoid crossing over anti-etch, if at all possible. Crossing over anti-etch (split planes) increases inductance and radiation levels by forcing a greater loop area. Route digital power and signal traces over the digital ground plane. Position the bypassing and decoupling capacitors close to the IC pins with wide traces to reduce impedance. 9. Are there any nets, which should be routed as 50 ohm impedance single-ended traces? If so, please identify them or let me know how to identify them on the schematic. Ans: There are two nets for 50 Ohm Impedance NetP5_2 [ Net going from P5 to R101] NetP6_2 [Net Going from P6 to R105] 10. Do you have a particular layer stack-up that you would like for me to use for this board? There appears to be about 42 different voltage nets and 3 ground nets on this board. Ans: Please refer to Attached PDF [COMExpressPnP_DG_09.pdf ] Section -6. I am also attaching COMX-CAR-P1_DG_Rev1.doc . Please refer to Section – 5 and Section -6 for Board stack up. Eight-Layer Stack-up This figure is an example of an eight layer stack-up. Layers L1, L3, L6 and L8 are used for signal-routing. Layers L2 and L7 are solid ground planes, while L4 and L5 are used for power. Microstrip layers 1 and 8 reference solid ground planes on layers 2 and 7, respectively. Inner signal layers 3 and 6 are asymmetric striplines that route differential signals. These signals are referenced to layers 2 and 7 to meet the characteristic impedance target for these traces. To reduce coupling to layers 4 and 5, specify thicker prepreg to increase layer separation.