technical program 2015

advertisement

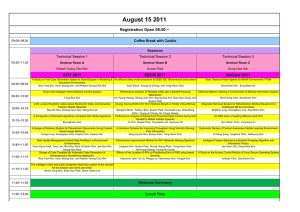

TECHNICAL PROGRAM TUESDAY, MAY 19 Session 1 Plenary Session 8:30 – 9:30 Welcome Didier Louis, Chair (EUR) 2015 IITC/MAM Conference Keynote Address Dr. Marie – Noëlle Séméria, CEO, Leti Session 2 Process Integration 10:00 – 12:10 2.1 (Invited) High Performance Cu/Low-k Interconnect Strategy beyond 10nm Logic Technology, R.-H. Kim, B.H. Kim, J.N. Kim, J.M. Baek, J.J. Lee, J. Hwang, J.H. Hwang, S.Y. Yoo, T.-J. Yim, K.-M. Chung, K.H. Park, T. Ozinda, E.B. Lee, S.D. Nam, Y.W. Cho, H.J. Choi, J.S. Kim, I.S. Kim, S.H. Ahn, S.H. Park, M.-C. Kim, B.U. Yoon, J.H. Ku, S.S. Paak, N.-I. Lee, S. Choi, H.-K. Kang and E.S. Jung, Samsung Electronics Co. Ltd., Gyeonggi-do, Korea. 2.2 Low-k Interconnect Stack with multi-layer Air Gap and Tri-Metal-Insulator-Metal Capacitors for 14nm High Volume Manufacturing, K.Fischer, M.Agostinelli, C.Allen, D.Bahr, M.Bost, P.Charvat, V.Chikarmane, Q.Fu, C.Ganpule, M.Haran, M.Heckscher, H.Hiramatsu, E.Hwang, P.Jain, I.Jin, R.Kasim, K.S.Lee, H.Liu, R.McFadden, S.Nigam, R.Patel, C.Pelto, P.Plekhanov, M.Prince, C.Puls, S.Rajamani, D.Rao, P.Reese, A.Rosenbaum, S.Sivakumar, B.Song, K.Sreenivas, M.Uncuer, S.Williams, M.Yang, P.Yashar, S.Natarajan, Intel Corporation 2.3 Progress in Thin Wire Back-End Of-Line Development, R. Seidel, G. Bonsdorf, E. Clauss, J. Daleiden, K. Donegan, F. Feustel, M. Hauschildt, B. Hintze, F. Koschinsky, G. Marxsen, R. Naumann, C. Peters, U. Queitsch, G. Talut, D. Theiss, M. Zinke, GLOBALFOUNDRIES Dresden Module One LLC & Co. KG 2.4 Robust TiN HM Process to Overcome Under Etch Issue for SAV Scheme on 14nm node, Tzu-Hao Fu, Yuan-Fu Ke, Shih-Chun Tsai, Chun-Ling Lin, Kuo-Wei Chen, MingYung Huang, Gary Cho, San-Fu Lin, Ting-Jun Wang, Albert Cheng, United Microelectronics Corporation 2.5 (Invited) Modeling of size effect of electrical resistivity in metallic interconnects: A Monte Carlo Approach, Takashi Kurusu, Toshiba Corporation Session 3 Materials & Unit Processes I 13:45 – 15:30 3.1 (Invited) Plasma Etch Challenges at 14nm and Beyond Technology Nodes in the BEOL, Nicolas Posseme, CEA Leti 3.2 Cobalt Bottom-Up Contact and Via Prefill enabling Advanced Logic and DRAM Technologies, M. H van der Veen, K. Vandersmissen, D. Dictus*, S. Demuynck, R. Liu**, X. Bin**, P. Nalla**, A. Lesniewska, L. Hall**, K. Croes, L. Zhao**, J. Bömmels, A. Kolics**, Zs. Tökei, Imec, *Lam Research Belgium, **Lam Research Corp. 3.3 Theoretical investigation of in situ k-restore processes for damaged ultra-low-k materials, A. Förster, J. Schuster, C. Wagner*, S. Gemming**, Fraunhofer ENAS, *TU Chemnitz, **Helmholtz-Zentrum Dresden – Rossendorf 3.4 Low temperature thermal and plasma enhanced atomic layer deposition of Ruthenium using RuO₄ and H₂/H₂-plasma, Matthias M. Minjauw, Jolien Dendooven, Boris Capon, Christophe Detavernier, Marc Schaekers*, University of Ghent, *IMEC Session 4 Advanced Characterization & Modelling Techniques 15:30 – 16:45 4.1 Modulation of the Schottky Barrier Height for Advanced Contact Schemes, Mariela Menghini, Pia Homm, Chen-Yi Su, Jorge A. Kittl*, Ryuji Tomita**, Ganesh Hegde*, Joon-Gon Lee**, Sangjin Hyun**, Chris Bowen*, Mark. S. Rodder*, Valeri Afanas’ev, and Jean-Pierre Locquet, KU Leuven Leuven Belgium, *Samsung Semiconductor Inc., Austin, Texas USA, **Samsung Dongtan Korea. 4.2 Nanometre scale 3D nanomechanical imaging of semiconductor structures from few nm to sub-micrometre depth, O.V. Kolosov, F. Dinelli*, A. Robson, A. Krier, M. Hayne, V. I. Fal'ko, M. Henini**, Lancaster University, *CNR–INO, **The University of Nottingham 4.3 Numerical analysis of airgap stability under process-induced thermo-mechanical loads, H. Zahedmanesh, M. Gonzalez, Ivan Ciofi, K. Croes, J. Boemmels, Z. Tőkei, imec Session 5 Poster Session I 16:45 – 18:15 Advanced Characterization & Modelling Techniques P.1-1 Full 3D Reciprocal Space Map of thin polycrystalline films for microelectronic applications, T. Nguyen Thanh, N. Blanc, N. Boudet, E. Bourjot*,S. Zhiou*, V. Kovacova*, P.Rodriguez*, F. Nemouchi*, P. Gergaud*, E. Bourjot**, E. Bourjot***, Institut NEEL, *CEA-LETI, **ST Crolles, ***IM2NP Aix-Marseille P.1-2 In-situ electrical characterization of Pt/NiO/Pt resistive memory elementary cells during FIB milling: a step towards electrical tomography of nanofilaments, C. Guedj1, G. Auvert1,2, E. Martinez1, 1Univ. Grenoble Alpes, CEA, LETI, Grenoble, France and 2STMicroelectronics, Crolles, France P.1-3 Effect of the temperature on the strain distribution induced in silicon interposer by TSVs: a comparison between micro-Laue and monochromatic nanodiffraction, B. Vianne,*, C. Krauss, S. Escoubas, M.-I. Richard, S. Labat, G. Chahine**, T. Schüllli**, J.-S. Micha***, V. Fiori*, A. Farcy*, O. Thomas, Aix-Marseille Université IM2NP. *STMicroelectronics. **ID01 ESRF and *** CEA-CNRS CRG-IF BM32 ESRF P.1-4 Influence of the substrate on the solid-state reaction of ultra-thin Ni film with a In0.53Ga0.47As under-layer by means of Full 3D Reciprocal Space Mapping, Seifeddine Zhiou, Tanh-Tra Nguyen*, Philippe Rodriguez, Fabrice Nemouchi, Patrice Gergaud, CEA-LETI, *Inst. NEEL P.1-5 Atomic oxygen treatment of carbon containing low-k dielectric materials to facilitate manganese silicate barrier formation, J.Bogan, A.P. McCoy, C. Byrne, R. O'Connor, G. Hughes, Dublin City University P.1-6 Stability of GeTe-based phase change material stack under thermal stress: reaction with Ti studied by combined in-situ x-ray diffraction, sheet resistance and atom probe tomography, Dominique Mangelinck, Magali Putero, Marion Descoins, Carine Perrin-Pellegrino, IM2NP, CNRS, Aix-Marseille Université, Marseille, France P.1-7 Numerical simulation of nano-indentation induced fracture of low-k dielectric thin films using the cube corner indenter, H. Zahedmanesh, K. Vanstreels, M. Gonzalez, imec P.1-8 Modeling and Analysis of Vertical Noise Coupling between Clock Tree and Channel Routing Wire in 3D Mixed Signal Integration, Shiwei Wang, Huanyu He*, Yingtao Ding, Jian-Qiang Lu*, Beijing Institute of Technology, *Rensselaer Polytechnic Institute P.1-9 Thin amorphous silicon oxide ICPECVD layer on gold surface for Surface Plasmon Resonance measurements, Etienne Herth*, Rabah Zeggari**, Jean-Yves Rauch*, Fabien Remy-Martin*, Wilfrid Boireau*, *Femto-ST,**FEMTO-Engineering Materials & Unit Processes P.2-1 Simple Test Vehicle for Metal Fill and Resistance of Sub-8nm Nanowire, S. H. Sung, J. Chawla, C. Carver, R. Chebiam, J. Clarke, C. Jezewski, T. Tronic, R. B. Turkot, H. J. Yoo, Components Research, Intel Corporation P.2-2 Optimized pore stuffing for enhanced compatibility with interconnect integration flow, J.-F. de Marneffe1, L. Zhang1,2, V. Rutigliani1, G. Noya3, Y. Cao4, A. Lesniewska1, O. Pedreira1, K. Croes1, C. Gillot5, Z. Tokei1, J. Boemmels1 and M. R. Baklanov1, 1IMEC, 2Katholieke Universiteit Leuven, 3Merck Performance Materials Manufacturing G.K., 4EMD Performance Materials Corp., and 5GLOBALFOUNDRIES P.2-3 Investigation of barrier formation and stability of self-forming barriers with CuMn, CuTi and CuZr alloys, Mathias Franz, Ramona Ecke, Christian Kaufmann*, Jakob Kriz** and Stefan E. Schulz*, Fraunhofer ENAS, *Technische Universität Chemnitz, ** Infineon Technologies Dresden GmbH P.2-4 Impact of UV wavelength and curing time on the properties of spin-coated low-k films, M. Redzheb, P. Van Der Voort, M. Krishtab*, S. Armini*, K. Vanstreels*, A. Franquet*, M. Baklanov*, L. Prager**, University of Gent, *imec, **Leibniz-Institut für Oberflächenmodifizierung P.2-5 Post-Etch Template Removal Strategy for Reduction of Plasma Induced Damage in Spin-On OSG Low-k Dielectrics, M. Krishtab, K. Vanstreels, M. Baklanov, S. De Gendt*, imec, *KU Leuven P.2-6 Atomic layer deposition of Ru-Mn alloy film as a diffusion barrier for seedless Cu interconnects, Hyun-Jung Lee1, Seung-Joon Lee1, Seungmin Yeo1, Yujin-Jang1, Taehoon Cheon1,2 , Tae Eun Hong3 and Soo-Hyun Kim1, 1Yeungnam University, Gyeongsan-si, Korea, 2Deagu Gyeonbuk Institute of Science & Technology, Daegu, Korea and 3Korea Basic Science Institute, Busan, Korea P.2-7 In situ cleaning/passivation of surfaces for contact technology on III-V materials, Philippe Rodriguez *, Laura Toselli* , Elodie Ghegin*,**, Fabrice Nemouchi* , Névine Rochat* , Eugénie Martinez*, *CEA LETI, **STMicroelectronics P.2-8 Characterisation of CuAl alloy for future interconnect technologies, C. Byrne, A.P. McCoy, J. Bogan, A. Brady and G. Hughes, Dublin City University, Dublin, Ireland P.2-9 A new dicobaltatetrahedrane precursor studied for the MOCVD of cobalt metal layers, M.Kaspar, T.Waechtler, S.E. Schulz, T. Gessner, C. Georgi*, H.Lang*, Center for Microtechnologies Technische Universität Chemnitz and Fraunhofer ENAS, *Technische Universität Chemnitz Faculty of Science P.2-10 Atomic layer deposition of Ru thin films using O2 or H2 molecules as a reactant as a seed layer for Cu electroplating, Seung-Joon Lee, Minyoung Lee, Taehoon Cheon, Soo-Hyun Kim, Masayuki Saito*, Kazuharu Suzuki*, Shunichi Nabeya*, Jeongyeop Lee**, Sangdeok Kim**, and Seungjin Yeom**, Yeungnam Univ., *TANAKA,**SK Hynix P.2-11 Process Development of Replacement Metal Gate Tungsten Chemical Mechanical Polishing on 14nm Technology Node and Beyond, J.C. Lin, H.J. Liu, W.C. Lin, C.H. Lin, T.H. Hung, K.R. Li, J.F. Lin, J.Y. Wang, C.C .Liu, J.Y Wu, United Microelectronics Corp. P.2-12 Cobalt compatible cleaning solutions for 14nm and beyond, K Courouble,L Broussous,S Zoll,K Haxaire, M Mellier, G Druais, STMicroelectronics P.2-13 Contribution of Molecular Simulation to the characterization of porous low-k materials, L. Broussous, M.Lépinay, B.Coasne*, C.Licitra**, F.Bertin**, V.Rouessac***, A.Ayral***, STMicroelectronics, Crolles, France, * CNRS-MIT, Cambridge, MA, USA, ** Univ. Grenoble Alpes - CEA, LETI, Grenoble, France, ***CNRS/ENSCM/UM, Montpellier France P.2-14 Direct Copper Electrodeposition on Novel CoMo Diffusion Barrier, Xu Wang, Li-Ao Cao, Xin-Ping Qu, Fudan University P.2-15 Sub-90nm Pitch Cu Low-k Interconnect Etch Solution Using RF Pulsing Technology, J H Liao, Yu Tsung Lai, Stan Wan, Brandon Kuo, Prabhakara Gopaladasu* David Wei* Sean Yao* Wesley Lin* Ivan Wang* Paul Lin*, Barrett Finch*, and Shashank Deshmukh*, United Microelectronics Corp., *Lam Research Corp. Process Integration P.3-1 Variability of Quadruple-Patterning Interconnect Processes, R. Baert, I. Ciofi, C. Wilson, V. Vega Gonzalez, J. Bömmels, Zs. Tökei, J. Ryckaert, P. Raghavan, A. Mercha, D. Verkest, IMEC P.3-2 Demonstration of New Planar Capacitor (PCAP) Vehicles to Evaluate Dielectrics and Metal Barrier Thin Films, Kevin L. Lin, Jeffrey Bielefeld, Jasmeet S. Chawla, Colin T. Carver, Ramanan Chebiam, James S. Clarke, Jacob Faber, Michael Harmes, Tejaswi Indukuri, Christopher Jezewski, Rahim Kasim, Mauro Kobrinsky, Nafees A. Kabir, Brian Krist, Narendra Lakamraju1, Hazel Lang, Ebony Mays, Alan M. Myers, John J. Plombon, Kanwal Jit Singh, Jessica Torres, Hui Jae Yoo, Intel Corporation P.3-3 Alternative ULK integration approach using a sacrificial layer in a standard dual damascene flow., B. Uhlig, J. Calvo, J. Koch, X. Thrun, R. Liske, Fraunhofer IPMSCNT, Dresden, Germany. P.3-4 A Study of Beol Resistance Mismatch in Double Patterning, Shaoning Yao, Larry Clevenger, Noah Zamdmer Reliability and Failure Analysis P.4-1 Evaluation of adhesion energy and its correlation to apparent strength for Cu/SiN interface in copper damascene interconnect structures, S. Kamiya1, 2, C. Chen1, N. Shishido1, 2, M. Omiya2, 3, K. Koiwa1, 2, H. Sato1, 2, M. Nishida1, 2, T. Suzuki4, T. Nakamura4, T. Nokuo2, 5 and T. Suzuki2, 5, 1Nagoya Institute of Technology, 2Japan Science and Technology Agency, 3Keio University, 4Fujitsu Laboratories Ltd., 5JEOL Ltd. P.4-2 Electromigration-limited Reliability of Advanced Metallization for Memory Devices, Kyung-Tae Jang, Yong-Jin Park, Min-Woo Jeong, Seung-Min Lim, Han-Wool Yeon, Ju-Young Cho, *Jin-Sub Shin, *Byoung-Wook Woo, *Jang-Yong Bae, *Yu-Chul Hwang, Young-Chang Joo, Seoul National University, *Samsung Electronics Corp. P.4-3 Compact Model for Solder Bump Electromigration Failure, H. Ceric, Christian Doppler*, S. Selberherr, Institute for Microelectronics, TU Wien and *Laboratory for Reliability Issues in Microelectronics WEDNESDAY, MAY 20 Sesson 6 Novel Systems & Emerging Technology I 8:00 – 9:45 6.1 (Invited) Self-organization and Emergence of Dynamical Structures in Neuromorphic Atomic Switch Networks, James K. Gimzewski*, Adam Z. Stieg, Masakazu Aono, Audrius Avizienis, Henry Sillin, Hsien-Hang Shieh, Renato Aguilera, Eric Sandouk, Eleanor Demis and Kelsey Scharnhorst, University of California, Los Angeles, CA, National Institute for Materials Science (NIMS), Ibaraki, Japan, University of Bristol, Bristol, UK 6.2 Nickel Silicide for Interconnects, Kevin L. Lin, Stephanie A. Bojarski, Colin T. Carver, Manish Chandhok, Jasmeet S. Chawla, James S. Clarke, Michael Harmes, Brian Krist, Hazel Lang, Mona Mayeh, Sudipto Naskar, John J. Plombon, Seung Hoon Sung, Hui Jae Yoo, Intel Corporation 6.3 Direct Etched Cu characterization for Advanced Interconnects, L. Wen, F. Yamashita*, B. Tang, K. Croes, S. Tahara*, K. Shimoda*, T. Maeshiro*, E. Nishimura*, F. Lazzarino, I. Ciofi, J. Bömmels, Z. Tőkei, imec Belgium, *Tokyo Electron Limited, Japan 6.4 Fabrication and characterization of piezoelectric microgenerators for flexible energy harvesting using P(VDF-TrFE) screen-formulated inks, E. Gusarova, B. Viala, A. Plihon, B. Gusarov*,** , L. Gimeno*,**, O. Cugat*,**, CEA ,*Univ. Grenoble G2Elab, **CNRS G2Elab Session 7 Contact and Silicide 10:15 – 12:00 7.1 (Invited) Anisotropic Nickel Silicidation of Silicon Nanowires and Transistor Applications, Walter Weber, Nam Lab Dresden 7.2 Influence of alloying elements on the phase formation of ultrathin Ni (<10nm) on Si(001) substrates, F.A. Geenen, K. Van Stiphout*, J. Jordan-Sweet**, A. Vantomme*, C. Lavoie**, C. Detavernier, Ghent University, * KU Leuven, ** IBM 7.3 Improved NiSi contacts on Si by CF4 plasma immersion ion implantation for 14nm node MOSFETs, Haitao Zhang, Julian Duchaine*, Frank Torregrosa*, Linjie Liu, Bernd Holländer, Uwe Breuer, Siegfried Mantl, Qing-Tai Zhao, Forschungszentrum Jülich and *IBS (ION-BEAM-SERVICES) 7.4 Nickel Silicide for Source-Drain Contacts from ALD NiO Films, Viljami Pore, Eva Tois, Raija Matero, Suvi Haukka, Marko Tuominen, Jacob Woodruff, Brennan Milligan, Fu Tang, Michael Givens, ASM Session 8 3D Integration & Packaging I 13:30 – 15:15 8.1 (Invited) Thermal management in 3D integrated circuits, Perceval Coudrain, STMicroelectronics 8.2 Demonstration of a cost effective Cu electroless TSV metallization scheme, K. Vandersmissen, F. Inoue, D. Velenis, Y. Li, S. Van Huylenbroeck, N. Heylen, H. Struyf, M.H. van der Veen, D. Dictus*, B. Frees*, M. Kondo**, T. Seino**, imec, *Lam Research Corp., **MLI 8.3 Thermal Impact Study of Block Folding and Face-to-Face Bonding in 3D IC, Y. Peng, M. Jung*, T. Song, Y. Wan**, S. Lim, Georgia Institute of Technology, *Intel Corp., **Google Inc. 8.4 Advanced Integrated Metallization Enables 3D-IC TSV Scaling, Jengyi Yu, Sanjay Gopinath, Praveen Nalla, Matthew Thorum, Larry Schloss, Daniela M. Anjos, Prashant Meshram, Greg Harm, Joe Richardson, Tom Mountsier,Lam Research Corp Session 9 Advanced Memories 15:15 – 16:40 9.1 (Invited) Interconnect for emerging new memories, Er-Xuan Ping, AMAT 9.2 (Invited), Resistive switching in oxides for nonvolatile memories and neuromorphic computing, Sabina Spiga, CNR IMM MDM 9.3 Influence of alloying the copper supply layer on the retention of CBRAM, W. Devulder, K. Opsomer*, M. Jurczak*, L. Goux*, C. Detavernier, Ghent University, Imec Session 10 Poster Session II 16:40 – 18:10 3D Integration & Packaging P.5-1 Cobalt UBM for fine pitch microbump applications in 3DIC, Jaber Derakhshandeh, Inge De Preter, Kevin Vandersmissen, Dries Dictus1, Luca Di Piazza2, Lin Hou3, Stefano Guerrieri2 George Vakanas4, Silvia Armini, Robert Daily, Alicja Lesniewska, Yannick Vandelaer3, Myriam Van De Peer, John Slabbekoorn, Kenneth June Rebibis, Andy Miller, Gerald Beyer and Eric Beyne, imec, 1Lam Research, 2Micron Technology, 3KU Leuven and 4Intel Corp P.5-2 Withdrawn P.5-3 Low-Cost, Single-Step Hybrid Bond/Barrier Films for Cu Bondlines in Advanced Packaging, Qiran Xiao, Brian Watson, Reinhold H. Dauskardt, Stanford University P.5-4 Copper-Copper Direct Bonding: Impact of Grain Size, P. Gondcharton1,2, B. Imbert 1,2, L. Benaissa1,2 and M. Verdier1,3, and 1Univ. Grenoble Alpes, , 2CEA, LETI and 3CNRS, SIMAP P.5-5 Withdrawn P.5-6 Aluminum-Capped Copper Bond Pads for Ultrasonic Heavy Copper WireBonding on Power Devices, D. Gross, S. Haag, M. Reinold, M. Schneider-Ramelow*, K.-D. Lang**, Robert Bosch GmbH, *Fraunhofer IZM, **Technische Universität Berlin P.5-7 Fabrication, Assembly, Failure Estimations of for Ultra-Thin Chips Stacking by Using Pre-Molding Technology, Chang-Chun Lee, Yu-Min Lin*, Yan-Yu Liou, ChauJie Zhan*, Tao-Chih Chang*, Chung Yuan Christian University and *Industrial Technology Research Institute P.5-8 Low Temperature Bonding of Cu/Pd-Pd/Cu Interconnects for Three-Dimensional Integration Applications, Yan-Pin Huang, Yu-San Chien, Ruoh-Ning Tzeng, and Kuan-Neng Chen, National Chiao Tung University P.5-9 Experimental characterization of TSV liquid cooling for 3D integration, M. Park, S. Kim, S. E. Kim,S eoul National University of Science and Technology P.5-10 Si interposer with high aspect ratio copper filled TSV for system integration, C. Song, K. Xue, S. Yang, Z. Yong, H. Li, X. Jing, U. Lee*, W. Zhang, NCAP and *Samsung Electronics Co., Ltd. P.5-11 Analysis of Thermal Effects of Through Silicon Via in 3D IC using Infrared Microscopy, Y. Shin, S. E. Kim, S. Kim, Seoul National University of Science and Technology P.5-12 High-Voltage Monolithic 3D Capacitors based on Through-Silicon-Via Technology, S. Gruenler, G. Rattmann, T. Erlbacher, A. J. Bauer, L. Frey*, Fraunhofer IISB, *University of Erlangen-Nuremberg P.5-13 Solution of Warpage Improvement for Embedded Interposer Carrier Integrated into 3D-ICs Packaging, Chang-Chun Lee, Ren-Chin Cheng*, Yu-Min Lin*, Hsing-Ning Liu, Yan-Yu Liou, Tao-Chih Chang*, Chung Yuan Christian University and *Industrial Technology Research Institute P.5-14 Enhancement of Cu Through-Silicon-Via(TSV) Filling Rate by Applying Pulse wave form Current, Sanghyun Jin*, Sungho Seo*, Geon Wang*, Jaehong Lim**, Bongyoung Yoo*, *Hanyang University, Ansan, Korea and **Korea Institute of Materials Science, Changwon, Korea Advanced Memories P.6-1 The role of carbon as an interfacial materials for OxRAM memories, A. Delamoreanu, P. Gonon, E. Jalaguier*, C. Vallée, LTM CNRS, *LETI CEA P.6-2 Back End of Line Copper Metal Anti-Fuse, Huai-Fu Tu, Chang-Chien Wong, ChingHsiang Tseng, Chung-Ming Lee, Chi-Horn Pai, United Microelectronics Corporation Contact and Silicide P.7-1 Ni silicides formation: use of Ge and Pt to study the diffusing species, lateral growth and relaxation mechanisms., Mike El Kousseifi, Khalid Hoummada, Thierry Epicier*, Dominique Mangelinck, IM2NP, CNRS and *MATEIS, UMR P.7-2 TC Degradation and Root-Cause Analysis of SACVD BPSG Film for Robust IC Fabrication, Jongwoo Park, Miji Lee, Han Byul Kang, Dong Keun Lee, Jung Dong Kim and Sangwoo Pae, Samsung Electronics Co., Ltd. P.7-3 Study of Ni-germanide phase formation in Ge(001) with Pd or Pt interlayer, S.M.C. Miranda, F.A. Geenen*, C. Detavernier*, K. Temst, A. Vantomme, KU Leuven,*Ghent University P.7-4 Influence of Nitrogen Implantation on the Ni-Si Reaction, K. van Stiphout, J. Demeulemeester,C. Detavernier*, K. Temst, A. Vantomme, KU Leuven, *Ghent Universi Novel Systems & Emerging Technology P.8-1 Selective Co Growth on Cu for Void-Free Via Fill, J Jun-Fei Zheng, Philip Chen, Tomas H. Baum, Ruben R. Lieten, William Hunks, Steven Lippy, Asa Frye, Weimin Li, James O’Neill, Jeff Xu*, John Zhu*, Jerry Bao*, Vladimir Machkaoutsan*, Mustafa Badaroglu*, Geoffrey Yeap*, Gayle Murdoch**, Jürgen Bömmels**, and Zsolt Tőkei**, Entegris® Inc. *Qualcomm Technologies Inc., **IMEC P.8-2 Solid state reaction of Ni thin film on n-InP susbtrate for III-V laser contact technology, E. Ghegin *,**, F. Nemouchi**, J. Lábár***, S. Favier*, C. Perrin****, K. Hoummada****, S. Gurbán***, P. Gergaud**, * STMicroelectronics, ** CEA, LETI, MINATEC, *** MTA EK MFA,**** Aix Marseille Université P.8-3 A 300mm Si Photonics Platform for Optical Interconnection, T. Mogami, T. Horikawa, K. Kinoshita, H. Sasaki, K. Morito, K. Kurata, Photonics Electronics Technology Research Association (PETRA) P.8-4 Process Control and Monitoring in Device Fabrication for Optical Interconnection using Silicon Photonics Technology, Tsuyoshi Horikawa*,**, Daisuke Shimura**, Seok-Hwan Jeong**, Masatoshi Tokushima**, Keizo Kinoshita**, Tohru Mogami**, *National Institute of Advanced Industrial Science and Technology (AIST), **Photonics Electronics Technology Research Association (PETRA) P.8-5 Carbon nanotubes TSV grown on an electrically conductive ZrN support layer, S. Vollebregt, S. Banerjee, F.D. Tichelaar, R. Ishihara, Delft University of Technology P.8-6 Uniform Growth of Multilayer Graphene on SiO2 by Solid-phase Precipitation Involving Carbon doped Cobalt with Copper Capping Layer, S. Sano, K. Kitamura, Y. Matsumoto, T. Sakai*, K. Ueno, Shibaura Institute of Technology, *Low-power Electronics Association and Project P.8-7 Ab-initio calculations of edge roughness effects on electrical properties of graphene nanoribbon interconnects with non-equilibrium Green’s function, Katsuya Yabusaki, Aizuddin Mohamad, Tadashi Sakai*, and Yuji Awano, Keio University, *Low-power Electronics Association & Project (LEAP) P.8-8 Nanostructured Material Formation for Beyond Si Devices, H. L. Chang, C. T. Chang and C. T. Kuo, National Chiao Tung University P.8-9 Carbon Nanomaterials Based TSVs for Dual Sensing and Vertical Interconnect Application, S. Sofela, H. Younes, M. Jelbuldina, I. Saadat, A. Al Ghaferi, Masdar Institute of Science and Technology THURSDAY, MAY 21 Session 11 Reliability and Failure Analysis 8:30 - 1015 11.1 (Invited) Reliability models and lifetime extrapolation for interconnect technologies, Kristof Croes, IMEC 11.2 Low Voltage IMD-TDDB lifetime model for Advanced Future Logic Technology Nodes, Tae-Young Jeong, Jinseok Kim, Yunhee Jo, Kyuho Tak, Miji Lee, Sari Windu, Hyunjun Choi, Yuri Choi, Yunkyung Jo, Sangwoo Pae, Jongwoo Park, Samsung Electronics Co., Ltd 11.3 A Flexible Top Metal Structure to Improve Ultra Low-K Reliability, K.F. Cheng, C.L. Teng, H.Y. Huang, H.C. Chen, C.W Shih, T.H. Liu, C.H. Tsai, C.W. Lu, Y.H. Wu, H.H. Lee, M.H. Lee, M.H. Hsieh, B.L. Lin, S.Y Hou, C.J. Lee, H.H. Lu, T.I. Bao, S.L. Shue, C.H. Yu, Taiwan Semiconductor Manufacturing Company 11.4 Re-think Stress migration phenomenon with Stress measurement in 12years, Hideya Matsuyama1, Takashi Suzuki2, Tomoji Nakamura2, Motoki Shiozu3 ,Hideo Ehara4, 1Fujitsu Semiconductor Ltd. Tokyo, Japan. 2Fujitsu Laboratory Ltd. Atsugi Kanagawa Japan, 3Mie Fujitsu Semiconductor Ltd. Mie,Japan, 4Fujitsu Semiconductor Ltd. Tokyo, Japan. Session 12 Novel Systems & Emerging Technology II 10:45 – 12:05 12.1 (Invited) Nanocarbon interconnects: Demonstration of properties better than Cu and remaining, Shintaro Sato, Fujitsu 12.2 Graphene wires as alternative interconnects, I.Asselberghs1, M. Politou1,2, B. Soree1,2, S. Sayan1,3, D. Lin1, P. Pashaei1,2, C. Huyghebaert1, P. Raghavan1, I. Radu1, Z. Tokei1, 1IMEC, Leuven, Belgium, 2KU Leuven, Leuven, Belgium. 3Intel Corporation, Santa Clara, CA 12.3 Electrical Properties of 30 nm Width Bi-Layer Interconnects of Multi Layer Graphene and Ni, Taishi Ishikura, Atsunobu Isobayashi, Daisuke Nishide, Ban Ito, Tatsuro Saito, Takashi Matsumoto, Yuichi Yamazaki, Hisao Miyazaki, Masahito Watanabe, Naoshi Sakuma, Akihiro Kajita and Tadashi Sakai,Low-power Electronics Association & Project (LEAP) Session 13 3D Integration & Packaging II 13:13 – 14:50 13.1 Reliability Study of Liner/Barrier/Seed Options for Via-middle TSV’s with 3 Micron Diameter and Below, Y. Li, S. Van Huylenbroeck, Ph. Roussel, M. Brouri*, S. Gopinath**, D. M. Anjos**, M. Thorum**, J. Yu**, G. P. Beyer, E. Beyne, K. Croes, Imec, Leuven, Belgium, *Lam Research Corporation, Leuven, Belgium, **Lam Research Corporation, Fremont, CA USA 13.2 Wafer Level Metallic Bonding: Voiding Mechanisms in Copper Layers, B. Imbert, P. Gondcharton, L. Benaissa, F. Fournel, M. Verdier*, Univ. Grenoble Alpes, CEA, LETI, MINATEC Campus, *Univ. Grenoble Alpes, CNRS, SIMAP 13.3 3D IC Power Benefit Study Under Practical Design Considerations, Taigon Song, Moongon Jung*, Yang Wan**, Yarui Peng, Sung Kyu Lim, Georgia Institute of Technology, *Intel Corp., **Google Inc. Session 14 Materials & Unit Processes II 14:50 – 16:30 14.1 Resistivity of sub-30 nm Copper Lines, J. M. Roberts, A. P. Kaushik, J. S. Clarke, Intel Corporation 14.2 Alternative integration of ultralow-k dielectrics by template replacement approach, L. Zhang, J.-F. de Marneffe, N. Heylen, G. Murdoch, Z. Tokei, J. Boemmels, S. De Gendt, M. R. Baklanov, L.Zhang* and S. De Gendt, * IMEC, Beliugm and *KULeuven, Belgium 14.3 Optimizing ULK Film Properties to Enable BEOL Integration with TDDB Reliability, E.Todd Ryan, D. Priyadarshini*,S.M. Gates*, H. Shobha*, J. Chen*, K. Virwani*, A. Madan*, E. Adams*, E. Huang*, E. Liniger*, A. Grill, D. Collins**, M. Stolfi**, K.S. Yim** and A. Demos**, GLOBALFOUNDRIES, *IBM and **Applied Materials 14.4 Experimental investigations on a plasma assisted in situ restoration process for sidewall damaged ultra low-k dielectrics, N. Köhler, T. Fischer, S. Zimmermann*, S. E. Schulz*