Experiment #3 - California State University, Northridge

advertisement

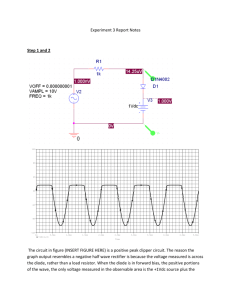

Experiment #3: Clipper and Clamper Circuits Friday Group Dr. Somnath Ari Mahpour 9-25-09 and 10-2-09 Teddy Ariyatham Due 10-9-09 Jayson dela Cruz Table of Contents Objective .............................................................................................................................. 3 Tools .................................................................................................................................... 3 Theory .................................................................................................................................. 3 Preliminary Calculations ..................................................................................................... 4 Discussion and Results ........................................................................................................ 5 Steps 1 and 2: Single Positive Peak Clipper .................................................................... 5 Steps 3 and 4: Single Negative Peak Clipper .................................................................. 7 1 Volt Input: ................................................................................................................. 7 2 Volt Input: ................................................................................................................. 8 3 Volt Input: ................................................................................................................. 9 4 Volt Input: ............................................................................................................... 10 Step 5: Zener Diode Clipper (10V Input) ...................................................................... 11 Steps 6 and 8: Clamper Circuit ...................................................................................... 12 0.1 µF Capacitor:........................................................................................................ 12 470 µF Capacitor:....................................................................................................... 13 Step 7: Clamper Circuit ................................................................................................. 14 Step 9: Clamper Circuit (10µF): .................................................................................... 15 Conclusion ......................................................................................................................... 16 Objective This laboratory experiment explores the applications of the diode. The purpose of this experiment is to observe the clipping and clamping functions found in our circuit designs. The designs that are required to be implemented and built is the zener diode clipper circuit and various forms of the clamper circuit. Tools - Oscilloscope - Functional generator - Power supply - Diodes: D1N4002 and D1N746A (zener) - Capacitors: 0.1 µF and 10µF - Resistors: 1kΩ and 15 kΩ Theory When observing the circuits, one can see that the both the clipping and clamping functions will occur. Clipping entails that the ends of the wave forms become cut off or “clipped.” There are several different cases that are explored in this experiment with respect to clipping. A case of clipping would occur in the forward active region. For example, a diode’s voltage threshold value is 0.7V. If one were to apply it across the diode, the clipping would occur at 0.7V since that is its threshold voltage. By adding a battery, the threshold is raised. Adding a 1V battery next to the diode will now create a total threshold voltage of 1.7V. Applying anything greater than 1.7V as an input would cause a clipping at 1.7V. Anything less than that threshold value will pass right through, thus resulting in no clipping occurring. When introducing a capacitor into the circuit clamping occurs. This essentially shifts the DC offset up or down depending on the direction of the diode. As we will see when testing circuits with different capacitances, forward active mode will determine whether there will be a full shift or if the circuit will be partially scaled down (i.e. squashed). The direction of the diode will also determine whether there will be a positive or negative shift on the y-axis. Preliminary Calculations Discussion and Results Steps 1 and 2: Single Positive Peak Clipper Figure 2.1: PSPICE Model 12V 8V 4V 0V -4V -8V -12V 0s 0.5ms 1.0ms 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms 4.5ms 5.0ms V(R1:2,0) Time Figure 2.2: PSPICE Simulation The circuit in figure 2.1 is a positive peak clipper circuit. The reason the graph output resembles a negative half wave rectifier is because the voltage measured is across the diode, rather than a load resistor. When the diode is in forward bias, the positive portions of the wave, the only voltage measured in the observable area is the +1Vdc source plus the diode voltage which is 0.7V when forward biased. This accounts for the positive wave output of +1.7Vdc. The oscilloscope images to the corresponding circuit can be found attached (Figure 1.1 and Figure 1.2). Steps 3 and 4: Single Negative Peak Clipper 1 Volt Input: Figure 4.1: PSPICE Model 1.0V 0.5V 0V -0.5V -1.0V 0s 0.5ms 1.0ms 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms 4.5ms 5.0ms V(R1:2,0) Time Figure 4.1b: PSPICE Simulation The clipping circuit in figure 4.1 shows a negative peak clipper circuit, but the graph seems to show the entire sine wave. The negative peak isn’t clipped because the input voltage wasn’t greater than the 1.7V it would take to put the diode into linear/active mode. Therefore the diode stays in saturation mode and the full 1V is read across the voltmeter leads. 2 Volt Input: Figure 4.2: PSPICE Model 2.0V 1.0V 0V -1.0V -2.0V 0s 0.5ms 1.0ms 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms 4.5ms 5.0ms V(R1:2,0) Time Figure 4.2b: PSPICE Simulation Figure 4.2 shows the same circuit as figure 4.1 except with a 2V input rather than a 1V input. The positive section shows the full 2V amplitude because the diode is reverse biased. The negative half of the wave is greater than the 1.7 volts required to activate the diode, but in the process, it loses 1.7V of its potential, according to KVL. Therefore the difference between the leads is -1.7V, resulting in a clipped sin wave. 3 Volt Input: Figure 4.3: PSPICE Model 3.0V 2.0V 1.0V 0V -1.0V -2.0V -3.0V 0s 0.5ms 1.0ms 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms 4.5ms 5.0ms V(R1:2,0) Time Figure 4.3b: PSPICE Simulation Figure 4.3 shows the same circuit as figure 4.1 except with a 3V input rather than a 2V input. The positive section shows the full 3V amplitude, while the bottom section again only shows the -1.7V difference between the positive and negative leads. 4 Volt Input: Figure 4.4: PSPICE Model 4.0V 2.0V 0V -2.0V -4.0V 0s 0.5ms 1.0ms 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms 4.5ms 5.0ms V(R1:2,0) Time Figure 4.4b: PSPICE Simulation Figure 4.4 shows the same circuit as figure 4.1 except with a 4V input rather than a 3V input. he positive section shows the full 3V amplitude, while the bottom section again only shows the -1.7V difference between the positive and negative leads. This circuit is always going to be clipped at -1.7V because any voltage greater than 1.7V will activate the diode, therefore negating any difference in potential between the two voltmeter leads. Step 5: Zener Diode Clipper (10V Input) Figure 5.1: PSPICE Model 4.0V 2.0V 0V -2.0V -4.0V 0s 0.5ms 1.0ms 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms 4.5ms 5.0ms V(D1:2,0) Time Figure 5.2: PSPICE Simulation Figure 5.1 is a zener diode clipper circuit. Zener diodes are diodes with a relatively low breakdown voltage. This graph represents the voltage across a reverse biased zener diode until the source voltage “overtakes” the zener breakdown voltage. Once this happens, the voltage potential quickly flat-lines. According to the graph, the breakdown voltage of these zener diodes is somewhere around 3V. When 10V positive is applied to the circuit, the 10V is read by the positive lead, while 10V-0.7V-3V = 6.3V is read across the output. This causes a voltage difference of 3.7 to be read as output, which is close to the value we obtained in the simulation. Steps 6 and 8: Clamper Circuit 0.1 µF Capacitor: Figure 8.1: PSPICE Model 20V 10V 0V -10V -20V 0s 0.5ms 1.0ms V(C1:1,C1:2) V(R1:2,0) 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms 4.5ms 5.0ms Time Figure 8.2: PSPICE Simulation Figure 8.1 is a clamper circuit that uses a diode and a capacitor to apply a dc offset to the source wave. While the input wave is positive, all of the voltage goes into the capacitor, which is why no voltage shows during the positive output portions. While the input wave is negative, the capacitor discharges and stacks on top of the input, therefore amplifying it. This explains why the negative peak is more than the 10V input wave. 470 µF Capacitor: Figure 8.3: PSPICE Model 20V 10V 0V -10V -20V 0s 0.5ms 1.0ms V(C1:1,C1:2) V(C1:2,0) V(C1:1,0) 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms 4.5ms 5.0ms Time Figure 8.4: PSPICE Simulation This clamper circuit is identical to the previous clamper circuit, except that the capacitor has a greater capacitance, therefore holds more charge. During the first positive half wave, the capacitor becomes charged with 10V. From that point on, the capacitor acts like a battery, shifting the entire waveform down by 10V. Step 7: Clamper Circuit As seen in figure 7.1 (attached) the 10 µF caused a vertical shift. As opposed to the previous two clamper circuits, this shift is neither negative nor a positive with a cutoff, rather it merely has a positive vertical shift. The peak-topeak voltage is approximately the same, therefore, with respect to that nothing has changed, however, the DC offset must be considered. This capacitance value was just perfect to cause a DC offset of 10 volts. Step 9: Clamper Circuit (10µF): Figure 9.1: PSPICE Model 20V 10V 0V -10V -20V 0s 0.5ms 1.0ms V(C1:1,C1:2) V(C1:2,0) V(C1:1,0) 1.5ms 2.0ms 2.5ms 3.0ms 3.5ms 4.0ms 4.5ms 5.0ms Time Figure 9.2: PSPICE Simulation This clamper circuit act the same as the previous clamper circuit figure 8.3 except that the diode direction is flipped, and a battery is added behind the diode. Therefore the shifted value will be the capacitor charge (10V) - 0.7 voltage across the diode, - 1Vdc because of the battery. 10-.7-1 = 8.3V DC offset. Conclusion This laboratory experiment taught us many things about certain circuits, but more than that, it taught us how to problem solve. When running into various problems, we would pull out our notes from the corresponding lecture class and dissect the physics of all the units that were under testing. By following charts, equations, and lecture examples we were able to get through the experiment with a deep understanding of the material that had to be covered throughout the course of this experiment. In the work field we will find that this will frequently be the case, therefore, learning this skill before going out into the field is integral. Thus, we are brought here to gain these skills so we will be properly prepared to join the workforce when we finish our academic career here at California State University, Northridge.