experiment 8 - The Circuits and Biology Lab at UMN

advertisement

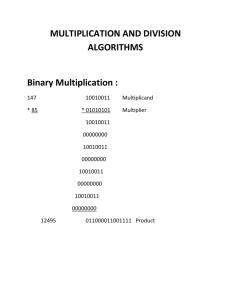

EXPERIMENT 8: BINARY MULTIPLIER PURPOSE In this experiment a system for multiplying binary numbers is designed and simulated. The system combines sequential circuits that control the operation of the multiplier with combinational circuits that perform arithmetic (addition) operations. MULTIPLICATION ALGORITHM The first step in developing the multiplier is to understand the algorithm used for multiplication. The basic algorithm to be used is the same as the one we use to multiply decimal numbers. We multiply each digit of the multiplier times the multiplicand to form a partial product and we add all of the partial products together to form the final product. This is illustrated on the left side of Fig. 8.1. Ordinarily, we produce all of the partial products and then add all of them together; however, this is not necessary and, instead, as each partial product is produced, it can be added to the sum of previous ones. Since adders in computers usually can only add two numbers together, the addition of partial products must be done in the latter way. Binary multiplication of positive numbers can be done using the same algorithm, but it is simpler since each partial product is either zero or equal to the multiplicand properly aligned with respect to the multiplicand. This is illustrated on the right side of Fig. 8.1 for a 4-bit multiplicand and 4-bit multiplier. 341 x 273 01023 23870 + 68200 93093 ->Multiplicand ->Multiplier ->Partial product1 ->Partial product2 ->Partial product3 ->Final product 0110 x 1101 0000110 0000000 0011000 0110000 1001110 ->Multiplicand ->Multiplier ->Partial product1 ->Partial product2 ->Partial product3 ->Partial product4 ->Final product Figure 8.1 Basic Multiplication Algorithm. As presented in Fig. 8.1 the addition of the partial products requires an adder that is twice as long as the length of the multiplicand and multiplier. Since a portion (almost half) of each partial product is 0, this is inefficient. (Note that the nonzero portion of each addition is just for the same number of bits as contained in the multiplicand, except for a possible carry into the next more significant position.) The double length adder can be avoided by shifting the accumulated partial products to the right with respect to the multiplicand rather than shifting the multiplicand to the left with respect to the accumulated partial products. Fig. 8.2 illustrates this algorithm. 8.1 An example of this algorithm is shown in Fig. 8.5. The initial partial sum is zero. Since bit 0 of the multiplier is 1, the first partial product (PP0) equals the multiplicand. This is added to the left half of the initial partial sum, and the partial sum is shifted right. Since bit 1 of the multiplier is 0, PP1 is zero and after addition to the partial sum, the partial sum is shifted right. This is repeated for bits 2 and 3 of the multiplier. At each step the new PP is either zero or the multiplicand and it is added to the upper half of the partial sum. Then the partial sum is shifted 1 bit to the right. This Add and Shift algorithm is done once for each bit of the multiplier. Bit 0 0000 +0110 0110 0011 +0000 0011 0001 +0110 0111 0011 +0110 1001 0100 of Adder XXXX -> Initial partial sum (zero) ---- -> PP0 XXXX -> PP0 + partial sum (zero) 0XXX -> Shift partial sum right ---- -> PP1 0XXX -> PP1 + partial sum 10XX -> Shift partial sum right ---10XX -> PP2 + partial sum 110X -> Shift partial sum right ---110X -> PP3 + partial sum 1110 -> Shift partial sum right (final answer) Bit 0 of Partial Sum Figure 8.2 Add & Shift Multiply Algorithm OPERATION OF 4-BIT BINARY MULTIPLIER You are to design and simulate in Cadence Design Entry and Allegro AMS Simulator a binary multiplier that multiplies two unsigned 4-bit operands and generates an 8-bit product, using the “add-and shift” algorithm described above. An incomplete block diagram of the multiplier is shown in Fig. 8.3. Input A is the multiplier and Input B is the multiplicand. The partial sum is stored in an 8-bit shift register (composed of two 4-bit parallel loading shift registers). A 4-bit adder adds either zero or the multiplicand to the upper half of the partial sum. The shift register is used to shift the partial sum right. The multiplexer selects the bit of the multiplier being examined in each step of the algorithm, and the AND array determines one of the inputs to the adder. The remainder of the circuitry provides the control so that the system sequences through the proper steps to implement the add and shift algorithm. The control is divided into two parts: a counter 8.2 and the actual controller. The controller is a synchronous sequential circuit, often called a state machine. When the state machine controller receives a 0 to 1 transition on the “start” signal, it causes the system to sequence through the steps of the algorithm stopping with the final product in the 8-bit shift register. (The multiplicand and multiplier are supplied to the A and B inputs before the start signal changes to 1 and they remain there until the multiply is complete.) When the algorithm completes, the outputs of the system are the product in the shift register and the signal “done” from the controller. (“done” changes from 0 to 1 when the algorithm completes.) The system remains in this condition, holding the outputs, until the next 0 to 1 change on “start”. Note that “start” cannot change from 0 to 1 until “done” is 1. “start” must remain at 1 for one clock cycle, but it can remain at 1 for any number of clock cycles, even beyond the completion of the multiply. “reset” is an asynchronous reset line, which is only used when power is applied to place the controller in the proper initial state. The circuit should be developed and debugged using Cadence Design Entry. The final report should contain a complete schematic for the design with complete explanations for each part. You should pay special attention to the timings for the circuit elements. Most of the debugging problems may originate there. Input A Figure 8.3 Block Diagram Multiplier 4 of Done Start Reset Counter Controller 4-to-1 Mux Input B 4 AND Array 4 8-bit Shift Register 4-bit Adder 8 Product (Incomplete) 8.3 4 PRELAB Begin the design of the multiplier by adding more detail to the block diagram. The parts available for your design are D Flip-flops (74LS74A) 1 4-bit Up/Down Counter (74LS169) 1 4-to-1 MUX 1 4-bit Adder (74LS283) 2 4-bit Parallel Shift Registers (74LS194A) Various NAND/AND/OR/NOT gates 1) Determine the control signals that must be supplied to the shift registers and multiplexer from the control circuitry. (Note: The discussion of the algorithm above ignored the possibility of a carry being generated when a partial product is added to a partial sum. You need to determine how to handle this case.) 2) Determine how the counter can be used to control the multiplexer and to also count the number of add and shift steps. Identify the control inputs that must be supplied to it from the controller. Do the design so that it can be easily extended to 16-bit operands. 3) Determine a state diagram for controller. First, identify all of its inputs and outputs. Then determine the sequencing of states for the possible input changes that can be presented to the controller. (If needed, the controller can have both Mealy and Moore type outputs.) At most four states are required. PROCEDURE Design using Cadence Design Entry and Allegro AMS Simulator. 1) Complete the design of the controller. (a) Construct a state table from the state diagram. Eliminate any redundant states. (b) Assign state variables to the states. (c) Use D-type FFs and derive minimized excitation equations for the FFs using Karnaugh maps. 2) Use Cadence Design Entry to enter a schematic for the multiplier. 3) Simulate the operation of your circuit for two multiplications of 1011 (multiplicand) times (0111). For the first multiplication, make “start” remain high past the end of the multiplication. For the second multiplication, make “start” remain high for just two clock 8.4 cycles. In addition to the inputs and outputs for the multiplier, include the state variables in the waveforms so the operation of your state machine can be seen. 4) Demonstration the simulation to the lab TA. 5) Explain how to modify your design so that it would work for 16-bit operands rather than 4bit operands. 8.5 Experiment 8 – Binary Multiplier Final Report 1) Submit original copies of your state diagram, state tables, and Karnaugh maps with next state equations. Also include original copies of you circuit and a trace showing circuit operation for the two 1011 x 0111 multiplications. Be sure to annotate your waveform, e.g., identify the inputs (multiplier and multiplicand), the outputs (the product and “done”) and the state variables. 8.6