HCC_Register_DefinitionV1p1

advertisement

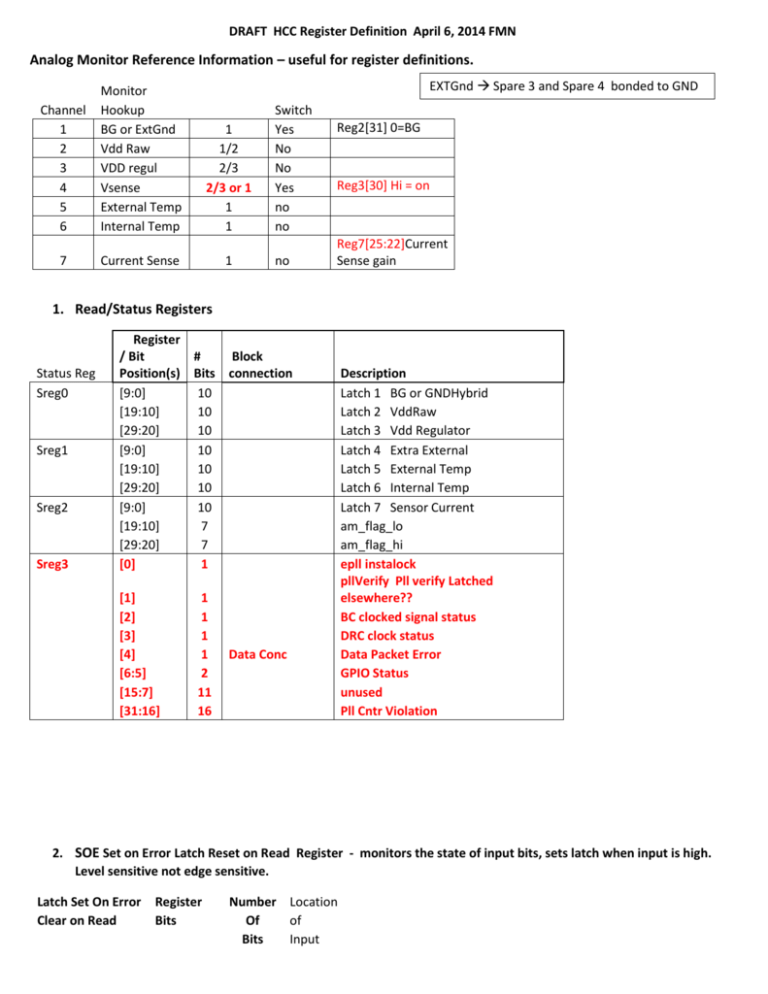

DRAFT HCC Register Definition April 6, 2014 FMN Analog Monitor Reference Information – useful for register definitions. EXTGnd Spare 3 and Spare 4 bonded to GND Channel 1 2 3 4 5 6 Monitor Hookup BG or ExtGnd Vdd Raw VDD regul Vsense External Temp Internal Temp 1 1/2 2/3 2/3 or 1 1 1 7 Current Sense 1 Switch Yes No No Yes no no no Reg2[31] 0=BG Reg3[30] Hi = on Reg7[25:22]Current Sense gain 1. Read/Status Registers Status Reg Sreg0 Sreg1 Sreg2 Sreg3 Register / Bit # Block Position(s) Bits connection [9:0] 10 [19:10] 10 [29:20] 10 [9:0] 10 [19:10] 10 [29:20] 10 [9:0] 10 [19:10] 7 [29:20] 7 [0] 1 [1] [2] [3] [4] [6:5] [15:7] [31:16] 1 1 1 1 2 11 16 Data Conc Description Latch 1 BG or GNDHybrid Latch 2 VddRaw Latch 3 Vdd Regulator Latch 4 Extra External Latch 5 External Temp Latch 6 Internal Temp Latch 7 Sensor Current am_flag_lo am_flag_hi epll instalock pllVerify Pll verify Latched elsewhere?? BC clocked signal status DRC clock status Data Packet Error GPIO Status unused Pll Cntr Violation 2. SOE Set on Error Latch Reset on Read Register - monitors the state of input bits, sets latch when input is high. Level sensitive not edge sensitive. Latch Set On Error Clear on Read Register Bits Number Location Of of Bits Input Low Lim Latch Hi Lim Latch epll Insta Lock pll verify Pll Soft Error SOE[6:0] SOE[13:7] SOE[14] SOE[15] SOE[16] 7 7 1 1 1 Sreg2[17:11] Sreg2[24:18] Sreg3[0] Sreg3[1] ?? Not Defin 3. Mask Register for Data Concentrator Error Bit – mirrors SOE Setting bit high in this register enables it to set the Data Concentrator Error Bit high when associated SOE latch bit goes high. Write Register Data Conc. Error Mask Register Low Lim Latch SOE[6:0] Hi Lim Latch SOE[13:7] epll Insta Lock SOE[14] pll verify SOE[17:15] Spare SOE[16] 7 7 1 3 1 Default 0 0 0 0 0 4. Autonomous Hybrid Low Power mode. LPH[11:0] the Hybrid clocks or regulators (GPIO bits 1 and 2) on Temp Limits Write Register Analog mon 5 is attached to External Temp sensor sense. Allow Hybrid Disables Disable Hybrid Clocks Default 0 0 0 0 0 0 0 0 0 0 0 0 Disable GPIO 1 Disable GPIO 2 Bit# LPH[0] 1 2 3 4 5 6 7 8 9 10 LPH[11] SOE[4] SOE[5] SOE[4] SOE[5] SOE[4] SOE[5] SOE[4] SOE[5] SOE[4] SOE[5] SOE[4] SOE[5] Analog mon 6 is hooked to internal temp Lo Lim Latch 5 Lo Lim Latch 6 Hi Lim Latch 5 Hi Lim Latch 6 Lo Lim Latch 5 Lo Lim Latch 6 Hi Lim Latch 5 Hi Lim Latch 6 Lo Lim Latch 5 Lo Lim Latch 6 Hi Lim Latch 5 Hi Lim Latch 6 5. HP High Priority Data Concentrator Register Bits HP[4:0] HP[5] HP[6] HP[7] HP[8] HP[9] HP[10] HP[12:11] HP[19:13] Location HW @ Sreg3[0] Sreg3[1] Sreg3[4] Sreg3[2] Sreg3[3] Sreg3[6:5] SOE[6:0] # bits 5 1 1 1 1 1 1 2 7 HCC address ePll instantLock PLL Verify Data Packet Error SEU detection Hybrid BC Clk Status Hybrid DRC Clk Status GP Bit Status Low Lim Latch 1-7 not used yet ‘and’ of enable and enabled temp error ‘and’ of enable and enabled temp error HP[26:20] HP[30:27] HP[31] SOE[13:7]: 7 4 1 High Lim Latch 1-7 Spares ‘OR’ unmasked Errors 6. General Write Register ( most recent changes are in RED) Write Registers with ReadBack Register / Bit Position(s) Reg0[3:0] Reg0[5:4] Reg0[9:6]; Reg0[17:10]; Reg0[19:18]; Reg0[23:20]; Reg0[27:24]; Reg0[31:28]; Reg1[4:0]; Reg1[9:5]; Reg1[14:10]; Reg1[16:15]; Reg1[20:17]; Reg1[23:21]; Reg1[24]; Reg1[25]; Reg1[26]; Reg1[27]; Reg1[28]; Reg1[29]; Reg1[30] Reg1[31] Reg2[15:0]; Reg2[16]; Reg2[20:17]; Reg2[30:21]; Reg2[31]; Reg3[9:0]; Reg3[19:10]; Reg3[29:20]; Reg3[30] Reg3[31] Reg4[9:0]; Reg4[19:10]; Reg4[29:20]; # Bits 4 2 4 8 2 4 4 4 5 5 5 2 4 3 1 1 1 1 1 1 1 1 16 1 4 10 1 10 10 10 1 1 10 10 10 Default value 5 0 B FF 1 ?? ?? ?? ?? ?? ?? 0 0 ?? 0 0 0 0 0 0 0 0 0 0 4 3FF 0 0 3FF 0 1 0 3FF 0 3FF Block connection ePllIcp EPllCap EPllRes ePllEnablePhase ePllReferenceFrequency ePllPhase320MHzA ePllPhase320MHzB ePllPhase320MHzC ePllPhase160MHzA ePllPhase160MHzB ePllPhase160MHzC sel_Fast clock sel_fdelay PLLverify_modeBits PLLverify_setLatch Enable PLL to Hybrid Enable DataConc EnableBCtoHybrid Enable DRC Sel_Rclk 0=80MHz?? dataCon_enable_8b_10b dataCon_mode_320 bg_s bg_en_ctrl am_ss am_limit1_hi sel_switch_VBG_AMgnd am_limit1_lo am_limit2_hi am_limit2_lo Autonomous Mon en_AM_Clock am_limit3_hi am_limit3_lo am_limit4_hi Description Current default 40uA Cap default 40pF Res. Default = 6K ( what about 4K) All phases enabled bit values '01 FCF Clock Rate 80 to 640 check 0= slow select delay setting for 640MHz clock TBD TBD PLL version of BC to Hybrid Switch from Power up to data conc mode BC clocked signals sent to hybrid Changed from Enable pre to Enable DRC Selects 80 or 160MHz Hybrid ReadData clock ?? Data Conc enable 8b 10b enable 0/1 --> 160/320MHz Select BG voltage. 1FFF= 600mV 1= Enable BG adjust 0=8pF 1=+.18p 2=+.35p 4=+.7p 8=+1.4pF ????? Different bit pos than others?? 0 = BG 1 = 0V ref 0 V or BG Ref 0V or BG Ref Switch on 2/3 Attenuator Ch4 Enable Autonomous Monitor Clock Reg4[31:30]; Reg5[9:0]; Reg5[19:10]; Reg5[29:20]; Reg5[31:30] Reg6[9:0]; Reg6[19:10]; Reg6[29:20]; Reg6[31:30] Reg7[9:0]; Reg7[13:10]; Reg7[17:14]; Reg7[21:18]; Reg7[25:22] Reg7[29:26] Reg7[30] Reg7[31] Reg8[2:0]; Reg8[3]; Reg8[6:4]; Reg8[7]; Reg8[10:8]; Reg8[13:11]; Reg8[16:14]; Reg8[19:17]; Reg8[22:20]; Reg8[25:23]; Reg8[28:26]; Reg8[31:29]; Reg9[2:0]; Reg9[5:3]; Reg9[8:6]; Reg9[11:9]; Reg9[14:12]; Reg9[17:15]; Reg9[18]; Reg9[20:19]; Reg9[24:21]; Reg9[25]; Reg9[27:26]; Reg9[31:28]; Reg10[0]; Reg10[2:1]; Reg10[6:3]; Reg10[7]; Reg10[9:8]; Reg10[13:10]; Reg10[17:14]; Reg10[21:18]; 2 10 10 10 2 10 10 10 2 10 4 4 4 4 4 1 1 3 1 3 1 3 3 3 3 3 3 3 3 3 3 3 3 3 3 1 2 4 1 2 4 1 2 4 1 2 4 4 4 0 0 3FF 0 0 3FF 0 3FF 01 0 FF 0 0 0 4 0 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 1 0 0 1 0 0 0 AM_ Ramp Gain am_limit4_lo am_limit5_hi am_limit5_lo Reg5 Spares am_limit6_hi am_limit6_lo am_limit7_hi GPIO_Set 0 and 1 am_limit7_lo promptA_cfg promptB_cfg promptC_cfg AM7 Current Monitor Reg 7 spares Enable Data Out 1 Enable Data Out 2 Data1Stave_cur Data1Stave_enpre Data2Stave_cur Data2Stave_enpre R3_L1_left_cur R3_L1_right_cur BC_L_hybrid_cur BC_R_hybrid_cur DRCleft_cur FastclkLeft_cur FastclkRight_cur DRCright_cur L0_CMD_left_hybrid_cur L0_CMD_right_hybrid_cur XOFFL1_cur XOFFL2_cur XOFFR1_cur XOFFR2_cur Spare CFD_BC_coarseDelay CFD_BC_fineDelay Spare CFD_R3L1_coarseDelay CFD_R3L1_fineDelay Spare CFD_L0_CMD_coarseDelay CFD_L0_CMD_fineDelay Spare CFD_DRC_coarseDelay CFD_DRC_fineDelay FD_xoffL1_fineDelay FD_xoffL2_fineDelay Gain setting or AM Ramp step unused Set GPIO bits high or low subject to error bits HOW DO WE SET THESE? Default " " Current Monitor High Current Default Move these to Reg 7 Spares& add enable?? Need two bits to enable 320MHz driver Turn on one BC as diagnostic? Turn on one Lo_CMD as diagnostic? Reg10[25:22]; Reg10[29:26]; Reg10[31:30] Reg11[3:0]; Reg11[7:4]; Reg11[11:8]; Reg11[15:12]; Reg11[16] Reg11[31:17] 4 4 2 4 4 4 4 1 15 0 0 0 0 0 0 0 0 0 FD_xoffR1_fineDelay FD_xoffR2_fineDelay Reg10 Spares unused FD_DataInLeft1_fineDelay FD_DataInLeft2_fineDelay FD_DataInRight1_fineDelay FD_DataInRight2_fineDelay Enable Fast Clock Reg 11 spares unused