Homework 2

advertisement

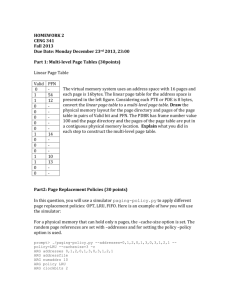

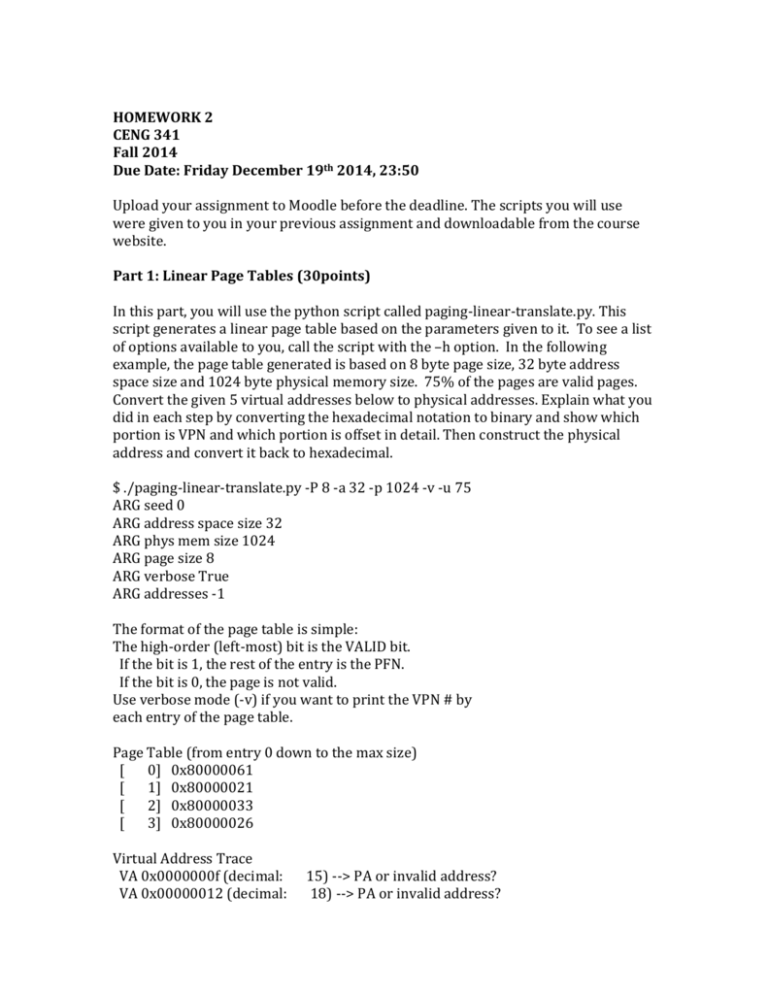

HOMEWORK 2 CENG 341 Fall 2014 Due Date: Friday December 19th 2014, 23:50 Upload your assignment to Moodle before the deadline. The scripts you will use were given to you in your previous assignment and downloadable from the course website. Part 1: Linear Page Tables (30points) In this part, you will use the python script called paging-linear-translate.py. This script generates a linear page table based on the parameters given to it. To see a list of options available to you, call the script with the –h option. In the following example, the page table generated is based on 8 byte page size, 32 byte address space size and 1024 byte physical memory size. 75% of the pages are valid pages. Convert the given 5 virtual addresses below to physical addresses. Explain what you did in each step by converting the hexadecimal notation to binary and show which portion is VPN and which portion is offset in detail. Then construct the physical address and convert it back to hexadecimal. $ ./paging-linear-translate.py -P 8 -a 32 -p 1024 -v -u 75 ARG seed 0 ARG address space size 32 ARG phys mem size 1024 ARG page size 8 ARG verbose True ARG addresses -1 The format of the page table is simple: The high-order (left-most) bit is the VALID bit. If the bit is 1, the rest of the entry is the PFN. If the bit is 0, the page is not valid. Use verbose mode (-v) if you want to print the VPN # by each entry of the page table. Page Table (from entry 0 down to the max size) [ 0] 0x80000061 [ 1] 0x80000021 [ 2] 0x80000033 [ 3] 0x80000026 Virtual Address Trace VA 0x0000000f (decimal: VA 0x00000012 (decimal: 15) --> PA or invalid address? 18) --> PA or invalid address? VA 0x0000001d (decimal: VA 0x00000010 (decimal: VA 0x00000009 (decimal: 29) --> PA or invalid address? 16) --> PA or invalid address? 9) --> PA or invalid address? Part 2: Multi-level Page Tables (30points) Linear Page Table Valid 0 1 1 0 0 0 0 0 1 0 0 0 1 1 0 0 PFN 54 12 14 10 13 - The virtual memory system uses an address space with 16 pages and each page is 16bytes. The linear page table for the address space is presented in the left figure. Considering each PTE or PDE is 8 bytes, convert the linear page table to a multi-level page table. Draw the physical memory layout for the page directory and pages of the page table in pairs of Valid bit and PFN. The PDBR has frame number value 100 and the page directory and the pages of the page table are put in a contiguous physical memory location. Explain what you did in each step to construct the multi-level page table. Part3: Page Replacement Policies (40 points) In this question, you will use a simulator paging-policy.py to apply different page replacement policies: OPT, LRU, FIFO. Here is an example of how you will use the simulator: For a physical memory that can hold only n pages, the –cache-size option is set. The random page references are set with –addresses and for setting the policy –policy option is used. prompt> ./paging-policy.py --addresses=0,1,2,0,1,3,0,3,1,2,1 -policy=LRU --cachesize=3 -c ARG addresses 0,1,2,0,1,3,0,3,1,2,1 ARG addressfile ARG numaddrs 10 ARG policy LRU ARG clockbits 2 ARG cachesize 3 ARG maxpage 10 ARG seed 0 ARG notrace False Solving... Access: Access: Access: Access: Access: Access: Access: Access: Access: Access: Access: 0 1 2 0 1 3 0 3 1 2 1 MISS MISS MISS HIT HIT MISS HIT HIT HIT MISS HIT LRU LRU LRU LRU LRU LRU LRU LRU LRU LRU LRU FINALSTATS hits 6 -> -> -> -> -> -> -> -> -> -> -> [0, [0, 1, [1, 2, [2, 0, [0, 1, [1, 3, [1, 0, [0, 3, [3, 1, [3, 2, misses 5 [0] 1] 2] 0] 1] 3] 0] 3] 1] 2] 1] <<<<<<<<<<<- MRU MRU MRU MRU MRU MRU MRU MRU MRU MRU MRU Replaced:Replaced:Replaced:Replaced:Replaced:Replaced:2 Replaced:Replaced:Replaced:Replaced:0 Replaced:- [Hits:0 [Hits:0 [Hits:0 [Hits:1 [Hits:2 [Hits:2 [Hits:3 [Hits:4 [Hits:5 [Hits:5 [Hits:6 Misses:1] Misses:2] Misses:3] Misses:3] Misses:3] Misses:4] Misses:4] Misses:4] Misses:4] Misses:5] Misses:5] hitrate 54.55 a) For a cache of size 5, generate worst-case address reference streams for each of the following policies: FIFO and LRU (worst-case reference streams cause the most misses possible.) For the worst case reference streams, how much bigger of a cache is needed to improve performance dramatically and approach OPT? b) Run the simulator for the following address references: 0, 1, 3,4, 5,1,3,2,3,6,7,2,4,5,4,1,2,3,0,2 Use OPT, LRU and FIFO separately with a cache size of 3. Compare FIFO and LRU algorithms to OPT. Why does LRU perform worse than FIFO?