Ece5020 notes Lecture 1 and upcoming homework: Skimming

advertisement

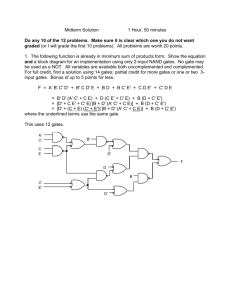

Ece5020 notes Lecture 1 and upcoming homework: Skimming, Viewing, and Reading: MIT OCW Video Lectures: Lec. 1 on Abstraction and CMOS Lecture. The idea of abstracting (simplifying) Maxwell’s equations into circuit analysis is extended to abstract semiconductor equations into switches for digital design (the digital abstraction). How timing analysis works in these abstractions will be discussed in the course, leading to methods of Logical Effort and Asynchronous design. OSU TEDx talk by Matt Stoltzfus on Transforming the Lecture Space. The referenced paper from the MIT Affective computing group is posted on Carmen. Bio-circuits. Textbook Chapter 1 (3rd ed. or 4th ed). Use Lecture slides as an abstraction for the textbook content. D. Harris webpage: Lecture 0, Lecture 1 Abstracting Digital vs. Analog Rabaey et al textbook webpage: Chapter 1 (Intro) ppt. slides Mircea tutorials: http://www.ee.virginia.edu/~mrs8n/cadence/Cadencetutorials.html www.mosis.com , AMI 0.5um Design Library , AMI 0.5um Padframe Library Start on Problems 1.4, 1.7, and 1.13 from the 3rd ed. textbook (online). These cover combinatorial and latched gates. Consider how the pull up and pull down blocks in gates are related by D’Morgan’s theory. Abstraction Problem. What are the similarities and differences in developing/using an abstract for report content vs. developing/using abstraction for electronic design content. Calculate the delay time of a 1mA current driving a 10pF capacitance to a voltage swing of 3v. an off chip delay estimation. Reduce the capacitance to 10fF and recalculate the delay time. an on chip delay estimation. This is This is Remark: note that the 1ma current is an equivalent current, since the current through a transistor is not really constant with voltage. We will see in Chp. 4 that that equivalent currents or resistances are a useful design model for high speed digital or large signal analog design. They will predict when more gates in series are faster than fewer gates in series. However, we will need to be able to tell when the equivalence is “good enough” to make a valid prediction. Scan from intro lecture: Inverters and changing to Analog Amps. CMOS Inverter DC curve analysis – Region C, the switching or analog region. Vgs – Vt concept. Analog amplifier and low Reff concept in timing calculations. Some approximate math for the Reff calculation, concept of tau quanta of time for logical effort. Cj delay vs load delay, gate sizing. Some Midterm Review: Region C calculation and resizing gates for equal delays A question of this type was on the midterm. as developed in the theory of logical effort. After the midterm, the next main topic is logic path delay Review the logical effort slides and the free version of Chp. 4 in the 3rd ed. of the textbook. TopSpice annotated schematic of Inverter Chain path. A 1 B C D E F G Schem at ic is sim ilar t o Figur e 4. 21 of 3r d ed. t ext book U1- 1 Cload = 2560f F delay quant a ( t au) C4 h1 H = 256 256 256 + 1 2 U2- 1 U3- 16 32 + 2 C3 Cst ar t = 10f F 16 16 U4- 1 U5- 7 U6- 49 3 C2 hk 7 7 U7- 1 U8- 4 21 + 3 7 U9- 16 U10- 64 C1 4 hk 4 4 4 4 16 + 4 delay quant a of kt h inver t er = Co/ Ci = Co*R/ k hk = Cok/ Cik each inver t er size and delay quant a 5 if hk = 2, how m any delay quant a? 6 7 Page: 1 of 1 Rev: 7 Revised: 2 Designing minimum delay in Inverter Chain path driving large capacitance is probably how logical effort was first developed. This example is in the logical effort slides, but not in the early part of the slides, ie. the slides are not in historical order of development. What about logical effort analysis for other types of combinational gates, NAND, NOR, MUX, etc? What about logical effort analysis for latches and flip flops? Best number of stages N when Cj is included. Need to write Delay equation in terms of N and optimize. Static Ram Cell is a latch without clocked pass transistors. Note that this requires transistor sizing analysis to change latch state using analog overpowering (both pullup and pulldown on at the same time. We will also use this approach in asynchronous logic gates. bit_b bit word weak med med A A_b strong