IEBL weekly progress report Student Name: Renjie Chen Project

advertisement

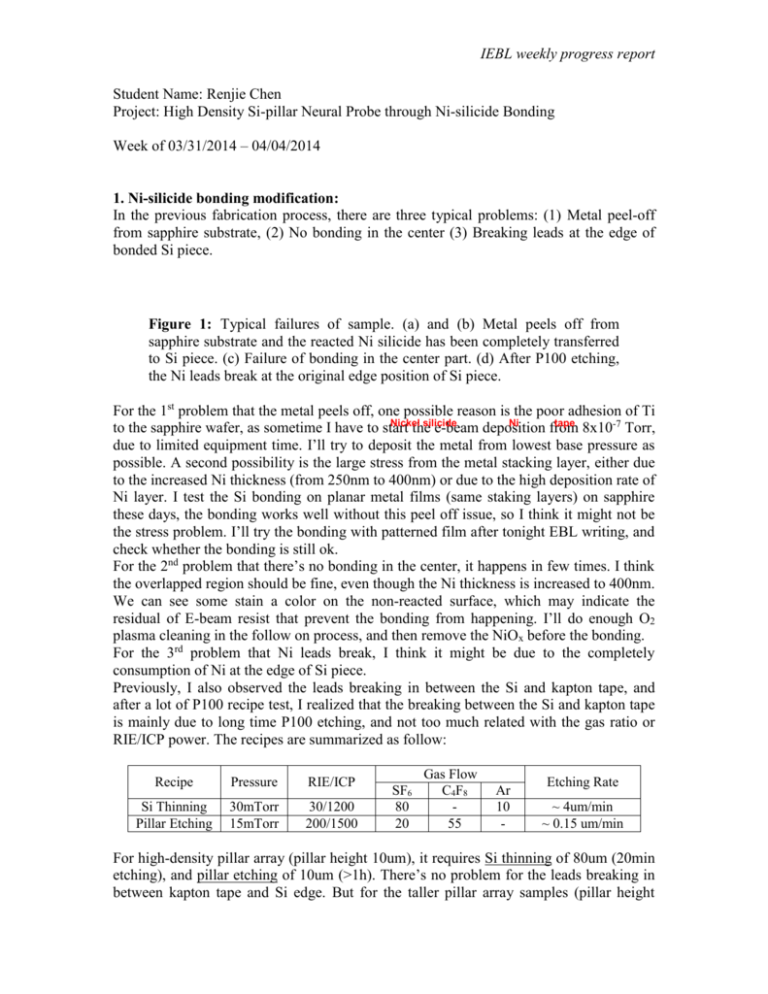

IEBL weekly progress report Student Name: Renjie Chen Project: High Density Si-pillar Neural Probe through Ni-silicide Bonding Week of 03/31/2014 – 04/04/2014 1. Ni-silicide bonding modification: In the previous fabrication process, there are three typical problems: (1) Metal peel-off from sapphire substrate, (2) No bonding in the center (3) Breaking leads at the edge of bonded Si piece. (a) (b) (c) (d) Figure 1: Typical failures of sample. (a) and (b) Metal peels off from sapphire substrate and the reacted Ni silicide has been completely transferred to Si piece. (c) Failure of bonding in the center part. (d) After P100 etching, the Ni leads break at the original edge position of Si piece. For the 1st problem that the metal peels off, one possible reason is the poor adhesion of Ti Nickel silicide Ni tape to the sapphire wafer, as sometime I have to start the e-beam deposition from 8x10-7 Torr, due to limited equipment time. I’ll try to deposit the metal from lowest base pressure as possible. A second possibility is the large stress from the metal stacking layer, either due to the increased Ni thickness (from 250nm to 400nm) or due to the high deposition rate of Ni layer. I test the Si bonding on planar metal films (same staking layers) on sapphire these days, the bonding works well without this peel off issue, so I think it might not be the stress problem. I’ll try the bonding with patterned film after tonight EBL writing, and check whether the bonding is still ok. For the 2nd problem that there’s no bonding in the center, it happens in few times. I think the overlapped region should be fine, even though the Ni thickness is increased to 400nm. We can see some stain a color on the non-reacted surface, which may indicate the residual of E-beam resist that prevent the bonding from happening. I’ll do enough O2 plasma cleaning in the follow on process, and then remove the NiOx before the bonding. For the 3rd problem that Ni leads break, I think it might be due to the completely consumption of Ni at the edge of Si piece. Previously, I also observed the leads breaking in between the Si and kapton tape, and after a lot of P100 recipe test, I realized that the breaking between the Si and kapton tape is mainly due to long time P100 etching, and not too much related with the gas ratio or RIE/ICP power. The recipes are summarized as follow: Recipe Pressure RIE/ICP Si Thinning Pillar Etching 30mTorr 15mTorr 30/1200 200/1500 SF6 80 20 Gas Flow C4F8 55 Ar 10 - Etching Rate ~ 4um/min ~ 0.15 um/min For high-density pillar array (pillar height 10um), it requires Si thinning of 80um (20min etching), and pillar etching of 10um (>1h). There’s no problem for the leads breaking in between kapton tape and Si edge. But for the taller pillar array samples (pillar height IEBL weekly progress report 30um), it requires Si thinning of 60um (15min), and pillar etching of 30um (>3h). I realized that the breaking of leads in between the Si edge and the kapton tape only happened for taller pillar array samples. For the high-density pillar array, the leads seem to break at the edge of the Si piece as shown in Fig 1(d). I think it might be due to the complete consumption of Ni at the edge of Si piece. A series of bonding tests was done between Si and planar film stacks on sapphire wafer, and the SEM images in Figure 2 show the cross-section of reacted Ni silicide. After 10min annealing at 400’C, the Ni has been completely consumed, and the thickness of NiSix only increased ~ 200nm with elongated annealing time at 400’C. We can see clearly at the edge that Si has consumed all the Ni beneath. I’m worried that this may cause the breaking of Ni leads during P100 etching process, as indicated in figure 3. (a) (b) (a) (b) (c) (c) Figure 2: Cross-section SEM images of bonded Si on planar film stacks on sapphire wafer. (a) 300’C 5min + 400’C 10min bonding; (b) 300’C 5min + 400’C 20min bonding; (c) 300’C 5min + 400’C 30min bonding. Center Edge Center Edge Figure 3: Schematic of bonded samples under P100 etching. Center Edge I plan to send both the planar film bonded sample and patterned film bonded sample bake for P100 etching test, to see whether the edge still has this breaking problem. If this is the case, I’ll need to shorten the annealing time, or make the Si bonded piece larger than the whole pattern, so that there will be no breaking at the edge. 2. BOSCH SiICP Etching Recipe Test In order to transfer the Si etching process here to CINT, I was testing the BOSCH Si etching recipe here, however, the results are not good. The recipes I tried and their results are listed in the following table. Recipe # 1 2 3 4 Pressure 30 mTorr 30 mTorr 30 mTorr 15 mTorr Gas SF6 80 80 80 80 flow Ar 10 40 10 10 RIE/ICP (W) 120/900 * 120/900 200/900 120/900 Result x100 (20min etch) 1.2 um/min 1.1 um/min 1.1 um/min 0.7 um/min Etch Rate * The ICP maximum power here is 900W, so I try to shrink the RIE/ICP power and keep the ratio the same as in P100 in Nano3. IEBL weekly progress report It can be seen from the microscope images that there’s no morphology changes after changing different etching parameters. The surface roughness might be due to the dirty chamber, because no polymer gas C4F8 is used in the test. Temporarily, I would like to try with the 10um thickness Si wafer for bonding, and can directly write the Ni dots afterward before sending back for pillar etching. 3. Photolithography on Sapphire wafer As we discussed in Wednesday group meeting that I faced some problems here while doing photolithography on sapphire wafer. In nano3, the chuck for MA6 aligner is transparent plastic, but here the small aligner is reflective stainless steel that reflects UV lights and causes overexposure of the whole sample. I tried to put a Si wafer beneath sapphire as John suggested, and did the test for whole night on Tuesday, because the AZ5214 resist has two expose steps (expose and flood) that introduce more parameters to tune. Finally, it was still not successful. Don helped me working on AZ5510 (high resolution negative resist) on Wednesday morning with MA6 aligner here, the pattern looks good, but the only issue is the adhesion problem as shown in Fig 4. I later checked the literature and the photoresist datasheet, there’s no mention of improving the adhesion issue. Yesterday after talking to several other people, I realized that the smaller aligner near the N2 box has problem with good contact, which waste me two days for exposure test. Now I’m using either MA6 or the small aligner near the corner, and went back to check AZ5214 resist, it works ok now. I’m planning to finish the EBL writing in the center region, and do the bonding tomorrow. Figure 4: Adhesion problem with AZ5510 photoresist. Plan for Next Steps: I plan to send back the following samples back to UCSD together with Cory’s sample and YunGoo’s sample before end of next week: (1) Samples that have Si bonded with planar film and patterned film on sapphire, to check whether the P100 etching will cause the leads breaking at the edge of Si piece. This can help prove whether the lead breaking is due to the completely consumption of Ni during bonding. (2) I’ll prepare 6 high-density patterns with Si pieces (90 um thick) bonded, and send back for Si thinning down. (3) I’ll try bonding with thin Si wafer (10um), and write the Ni dots here. Sent them back for pillar etching. Yun Goo and Michael are going to send me some Si wafer for solar cell patterning. I think my samples after thinning down with P100 can be sent back together with their sample.