Standard Project in VLSI Design SB1

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Standard Project in VLSI Design SB1

Laboratory Guide 7 – Post-layout Verification and Simulation

This laboratory guide provides an introduction to some important techniques for analogue simulation of IC layouts using Mentor Graphics' Calibre and Eldo tools, which form a part of the Analog Station package. For more details about Eldo , refer to the pamphlet: Analogue Simulation & Eldo .

The exercises in this session will give us detailed information about how the 2-input

NOR gate nor2 (designed earlier in this project using IC graph ) will operate when incorporated into the ringarray design. We shall first verify that the circuit behaves functionally as a NOR gate, with consistent input and output logic levels. Secondly, we shall use Eldo to determine (as accurately as possible) the rise and fall times of the gate, determined by transistor characteristics and parasitic capacitances. Our aim is to achieve fast but equalised rise and fall times at the output terminal of the gate, and we should be prepared for the possibility that modifications to the layout may be necessary to achieve this.

To put this session into perspective, let us first summarise the progress made thus far in the project. We have :

developed the concept of the ring oscillator (RO)

confirmed using Modelsim that the RO concept is valid

explored using Modelsim the effect of varying NOR gate delays

built a symbol and schematic for the RO based on the AMS library NOR2 gate

predicted the timing characteristics of the RO based on the AMS NOR2 gate

examined the transistor level schematic for a simple 2-input NOR gate

designed mask layouts for a 2-input NOR gate nor2

corrected any design rule violations in the nor2 layout

Note that although our own nor2 layout may be free of design rule violations, this does not in any way imply that it actually represents a 2-input NOR gate! It is necessary to verify that no errors have occurred in translating from the transistor schematic representation (perhaps via a stick diagram) to the layout. When we are satisfied of this, we need to confirm that the electrical performance is as required -- that is, that the particular combination of devices and interconnections actually functions as a NOR gate, and has the desired transfer and timing characteristics. Once these requirements are satisfied, the nor2 design may be incorporated in a library for use in the Ring Oscillator design or in other layouts where the NOR function is required.

Thus the key stages in the verification process are as follows :

verify the correspondence between the nor2 layout and the nor2t schematic

determine the parasitic elements present in the nor2 layout

back-annotate the parasitics to the corresponding nets of the nor2t schematic

simulate the result using Eldo

account for parasitics arising when the nor2 gate is connected to other elements

D M Holburn April 2009 ICstudio v2005 121 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Schedule

The remainder of this guide is divided into four key sections:

Section I Layout-Versus-Schematic (LVS) using Calibre

Section II Manual estimation of parasitic capacitances

Section III Extraction of parasitic capacitances using Calibre

Section IV Simulation of the back-annotated nor2t schematic using Eldo

Note: section II contains an exercise to be carried out in advance of the lab session.

You may wish to schedule your work to give yourself an interval away from the workstation for that purpose.

This section needs rewriting as Shawn’s modules do not cover!

Section I Layout-versus-Schematic (LVS) using Calibre

You should be logged in at a workstation as described in the Getting Started pamphlet, with Design Manager running. The current Mentor working directory should be $CBT_WD (which is the soft prefix for your $HOME/cbt directory), and you should select that same directory with the Navigator.

1. Remove the +5V voltage source from the nor2t schematic.

Prior to beginning the Eld o modelling work, a small change is required to the nor2t transistor-level schematic. This involves removing the +5V voltage source inserted originally. This will allow for the possibility of changing the supply voltage during the simulation. First open up Design Architect on the nor2t schematic. The nor2t component icon should be visible in the Navigator window.

Select this icon, and use the Data-Centred mode of invocation to start up Design

Architect : press the right (Menu) mouse button with the cursor over the Navigator window, and select the Open option in the resulting menu; choose design_arch .

When the Design Architect window opens up with the schematic sheet displayed, select the +5V source, and use the following command to delete it :

(Menu bar) > Edit > Edit Commands > Delete

In a similar way, delete also the immediately connected nets, but take care not to disrupt those nets interconnecting the MOSFET source and substrate electrodes, and do not delete the earth symbol.

Give the command: (Menu bar) > Check > Sheet > With Defaults and verify that there are no errors. Then save the design and leave Design Architect .

2. Open DVE and create a Design Viewpoint on the schematic nor2t for Eldo .

With Design Manager restored, start up the DVE application. In the Tools window, double click on the DVE item. When the DVE design window appears, examine the session window, noting particularly the Mietec item in the menu bar.

This contains entries that summon up utilities to create design viewpoints in the appropriate form for QuickSimII , Eldo , and ICgraph .

Give the command (Menu bar) File > Open > Design Viewpoint . When the

Open Design Viewpoint dialogue appears, use the Navigator to select the

D M Holburn April 2009 ICstudio v2005 122 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation component nor2t , and change the Viewpoint Name to Eldo_vpt1 . OK the dialogue box.

Now give the command: (Menu bar) > Mietec > Setup Eldo .

Be sure to allow the Setup userware to run to its completion. Wait before proceeding until you see the message :

Mietec setup for Eldo/Analog Interface is done

and cmos24 modelfile is connected appear in the status line at the foot of the screen. This may take 10-15 seconds.

D M Holburn April 2009 ICstudio v2005 123 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

3. Create a Design Viewpoint for Eldo (continued)

DVE will construct the required viewpoint. Note the list of Primitive elements, particularly MN and MP , recognised by Eldo as representing MOSFETs. Note also the appearance of a back-annotation object (a repository for extra information about the design). We shall later manipulate these back-annotation objects to provide Eldo with new information about circuit parasitics.

4. Close the design viewpoint.

The design viewpoint just created will later be operated on by the verification tools ICtrace and ICverify . In order to avoid problems with file locking, we must now close the design viewpoint (which has already been saved by the Mietec >

Setup Eldo operation carried out in paragraph 2). Give the command :

(Menu bar) > File > Close Design Viewpoint . Do not use a Save command explicitly - experience suggests this may cause corruption of the viewpoint. Do not exit from DVE; it will be required later.

5. Open ICstation on the nor2 layout and prepare for mask-level LVS.

We shall compare the nor2 layout we created in ICstation against the nor2t schematic. Restore the Design Manager window, and select the icon corresponding to the nor2 IC cell. Open ICstation on this object. Maximise the

ICstation window, and minimise the Design Manager window. In the Session

Palette , click the ICtrace(M) item. The ICtrace(M) palette appears.

First we open a Rules file (to allow ICtrace to determine the kinds of interconnection allowed in this process). Click the Load Rules item in the

ICtrace(M) palette. Check that the Rules File field contains the entry:

$MIETEC_CMOS24_IC_RUL , signifying the Mietec CMOS24 Design Rules. If not, type in this item taking care to avoid errors. OK the dialogue box.

Now set up for the LVS procedure. Click the LVS item in the ICtrace(M) palette. When the LVS (Mask) dialogue box appears, enter in the Source Name field the path to the design viewpoint Eldo_vpt1 you created in DVE (it should lie within the nor2t component). Use the Navigator if necessary.

Leave the other fields unchanged for the moment.

Click the Setup LVS button. When the Setup LVS dialogue box appears, review the five Property fields, and edit if necessary so they contain the following :

Type properties : phy_comp element comp

Pin name properties :

Power names :

Ground names :

Component Subtype : phy-pin

VDD

VSS

COMP_SUBTYPE

Check the Ignore Ports box. Click the No button for Recognise gates (since we wish to match schematic against layout transistor by transistor). OK the dialog box.

For the moment ignore the Setup Trace Props..

button, and OK the LVS (Mask) dialogue box. The LVS should run. Click the palette item Report , and select

LVS from the sub-menu. A report window should open, and should confirm the success of the LVS comparison. If not, speak to a demonstrator. You should be able to print out the result (several pages), using the procedure used earlier for setting up the printer. Consult a demonstrator for details.

D M Holburn April 2009 ICstudio v2005 124 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

6. Investigate the cross-probing feature

Assuming the LVS ran clean, investigate the probe-from-schematic feature which becomes available on successful completion of LVS. Close the report window, if open. With the layout window active, click the Logic item in the ICtrace(M) palette menu, and choose Open . When the dialogue box appears, enter the path to the Eldo viewpoint you created, and OK the box. A design window should open, showing the nor2t transistor level schematic. You may need to re-arrange windows on the screen in order to see both layout and schematic simultaneously.

Now use the mouse to select nets or transistor instances in the schematic window, and note that the corresponding elements in the layout become highlighted.

7. Identify a minor discrepancy between layout and schematic

Remembering that ICtrace is ignoring ports when performing its comparison, study the correspondence between schematic/layout entities and try to identify a further subtle (but benign) discrepancy between layout and schematic.

Use: (Palette menu) > Unshow > All to remove the highlighting. You can leave the schematic window open while you continue.

8. Verify that LVS is capable of detecting a layout error

You should confirm that ICtrace is actually capable of detecting a discrepancy between the layout and the schematic (implying a layout error). Close the report window, and make a minor circuit change to the nor2 layout. For example, temporarily removing the contact cut at the centre of the pair of n-channel transistors is an easy way of changing the connectivity. There is no need to save the changed design, since LVS is carried out on the layout as displayed. Repeat the LVS procedure outlined above, and study the report. Use the cross-probing feature to attempt to identify the errors diagnosed by ICtrace .

Restore the connectivity to the original situation. For example, if you chose to remove a contact cut as described above, replace it now, and re-run the LVS.

Confirm that it now runs without error. If time permits, make a small layout amendment that does not imply a change in connectivity -- for example, re-route a piece of interconnect. Verify that this has no effect on the outcome.

9. Investigate ICtrace 's ability to detect incorrect device properties.

When we ran LVS the first time, we ignored the Setup Trace Props..

feature.

This is provided to let ICtrace detect discrepancies between device properties specified in the schematic and those implied in the layout. The most useful application of this feature in digital IC design is to check that the transistors have been laid out with correct W & L values.

With the layout design window active, return to LVS by clicking the LVS item on the ICtrace palette menu. There should be no need to enter the Setup LVS dialogue (unless you exited from ICstation between sections) since the settings persist. Click the Setup Trace Props..

button. The resultant dialogue box exceeds the size of the screen, and you may need to use the mouse or Page Up and Page Down keys in order to navigate around it. Each entry in the table corresponds to a parameter which ICtrace can estimate and compare with any corresponding specification (in the instpar property) provided in the schematic.

Note particularly the mn and mp entries which correspond to n-channel and pchannel MOSFETs respectively. ICtrace recognises MOS transistors by detecting the superimposed mask layers, which are quite characteristic, and it can easily determine the length and width of the transistor channels.

D M Holburn April 2009 ICstudio v2005 125 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Enable tracing of L and W for n- and p-type transistors, by clicking the four Yes buttons for the corresponding items. Note that you can specify a tolerance (%), within which no warning will be issued. Ignore the remaining device types, which do not appear in our design. OK the dialogue box, and OK the parent dialogue in order to run the LVS.

If you were careful in your schematic and layout design, your LVS should still run without problem. However, if there are discrepancies between the L and W parameters specified in the nor2t schematic and those determined in the nor2 layout, ICtrace will warn you of these. If so, you will need to correct one or possibly both designs, using the appropriate editor.

If necessary, do this before continuing to the next stage. Be sure your design runs with no design rule violations and with no LVS errors before you proceed to the next stage.

The following section should be carried out away from the workstation.

You need a printed copy of your completed nor2 cell layout in order to proceed.

D M Holburn April 2009 ICstudio v2005 126 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Section II - Analysis of parasitic capacitances

Appreciation of the parasitic capacitances associated with a design is vital. Delay will be introduced by any capacitive element that has to be charged and discharged while the gate is operating. This applies to many, though not all, of the capacitive elements found in your design.

Later we shall use the tools within Mentor to analyse these capacitances with considerable accuracy. However, this process cannot be completely automated.

When considering a design it is very easy to overlook important contributions to capacitance and thus obtain an over-optimistic impression of performance. It is clearly important for a designer to have an appreciation of which contributions to capacitance have the most serious effect on performance, so that they can be minimised. The purpose of this section is to identify the most important contributions that need to be taken into account. Some are inherent in the layout for the nor2 cell

(already carried out), while others will arise from interconnect used to link the cells.

This interconnect has not yet been laid out, so its effects can only be estimated.

The following activity is to be carried out away from the workstation before proceeding with the automated extraction exercise. You will need a printed copy of your completed nor2 cell layout in order to proceed. If necessary, use the procedure in Lab Guide 6 to produce one, or refer to the copy included as an Appendix to that

Lab Guide. It may be useful when estimating dimensions to note that the size of the entire nor2 layout cell as supplied is 106

m tall by 57

m wide. You may wish to include one or more rulers in the checkplot to help estimate dimensions. Note also the availability of the ICgraph command: (Menu bar) Report > Selected , which reports

(among other things) the area in

m

2

of any layer currently selected.

Parasitic capacitances arising from interconnect

Three main forms of interconnect are used in digital IC layout. These are: polysilicon , metal1 and metal2 . All are separated from the substrate by means of dielectric layers of SiO2, polyimide or other material, and thus exhibit a defined capacitance to the substrate. The thickness of the dielectric is different in each of these cases, however, with the result that different materials have rather different specific capacitances (per unit area). Clearly there must also be inter-layer capacitances - for example, wherever polysilicon is overlaid by metal1 - but we shall ignore these effects for this project.

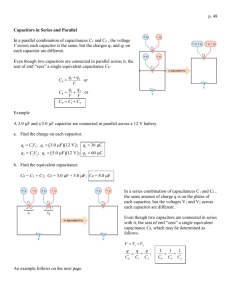

Figure 1 below illustrates some of the capacitance contributions within a typical nor2 gate due to interconnect .

D M Holburn April 2009 ICstudio v2005 127 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Figure 1 : Some capacitances due to interconnect

D M Holburn April 2009 ICstudio v2005 128 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Other contributions to parasitic capacitance

In addition to the parasitic capacitances arising from interconnect, there are contributions due to the semiconductor devices themselves. These can be identified :

at each gate (where a MOS capacitor is formed with plates comprising the gate electrode and the channel; the dielectric is the thin gate oxide);

at each drain and source, owing to the reverse-biased p-n junction formed between the source or drain and the substrate in which it lies.

These capacitances are closely controlled by the detailed dimensions of the devices, as well as by the characteristics of the materials used. We shall not evaluate the semiconductor capacitances here, as the models employed are quite complex. They will be determined later by Eldo , using extracted dimensions, and we shall consider the importance of these contributions at a later stage.

You can read about the evaluation of parasitic capacitance in CMOS gates in:

Analysis and Design of Digital Integrated Circuits

2 nd

Edition, by Hodges & Jackson . See p 75.

Analysis of parasitic capacitances due to interconnect

The next two sections will provide important data for inclusion in your Final Report.

The table below contains figures provided by AMS. They comprise typical specific capacitance values for three main forms of interconnect. In order to apply these values, you must estimate the area corresponding to to each element of interconnect.

It is apparent that several shapes corresponding to different materials may be electrically connected. Strictly speaking, we should also evaluate the electrical resistance of each element of interconnect and consider the entire structure as a set of interconnected R-C ladders. To simplify matters we shall asssume that we can neglect the electrical resistance of the interconnect, and that capacitive contributions may be combined as parallel capacitances.

Study the nor2 layout and schematic. Using data from the table, estimate the capacitance (to within about 10%) between each interconnect mask shape and substrate, using reasonably accurate scale measurements of area. Annotate your layout diagram accordingly. NB 1fF = 1015 F.

Use the table templates in the Appendix to this Lab guide to present your data.

Comment on the relative merits of the three forms of interconnect from the point of view of designing compact, high speed circuits.

AMS CMOS24 Technology - Interconnect specific capacitances

Material Polysilicon Metal1 Metal2 Units

Specific capacitance to substrate

4.03

10-2 2.3

10-2 1.73

10-2 fF

m-2

[1fF = 10-15 F]

D M Holburn April 2009 ICstudio v2005 129 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Estimating delay in interconnected gates

In real logic circuits consiating of many gates, estimates of delays must take into account not only this delays due the the capacitances (and other parasitic elements) within any gate, but must also consider effects caused by any other logic gates connected to it, and by the interconnect used to do this. Clearly, there are many different gate types, and myriad ways of interconnecting gates, so the problem can easily become complex. However, a number of useful simplifications can be made.

When estimating the delay introduced by a logic gate in a circuit consisting of several gates, it is convenient to suppose that all the elemental capacitances (due to wiring, other gate inputs, etc) to which the output terminal is linked can be combined as a single ‘lumped’ capacitor. The time taken to charge/discharge this capacitance can then be determined by considering the conductances in the pull-up and pull-down chains.

Using this approach facilitates a straightforward approach to analysis of timing delay which is nonetheless realistic and gives sensible results.

We shall now assume that the output of your nor2 gate is to be connected using metal1 interconnect to the two inputs of a succeeding identical nor2 gate (as in the ring oscillator). Both gates operate electrically as inverters - see Figure 2 opposite.

Draw (by hand) a schematic representation (based on Figure 1 and Figure 2) of the situation that exists when two (or more gates) are connected in cascade. It should help you identify those capacitances that contribute to delay.

Note : It is very easy to overlook capacitive contributions and get an impossibly optimistic but meaningless estimate for the delay. Equally, it is important to be aware of those capacitances that are connected to static nodes (where the potential does not change). These do not affect delay, and including them would also give a false impression. You must take care to avoid falling into either of these traps!

Making reasonable assumptions about the siting of the two abutted nor2 cells, estimate the area of metal1 , assumed to be of width 4

m, required to make these connections, and hence estimate its capacitance to substrate. Yo can deduce the form and size of the nor2 cell elements from the plot shown as an Appendix to Lab

Guide 6 ( IC layout with ICgraph ). Then, being careful that you have considered all contributions, estimate the total capacitance due to interconnect being driven by the first gate. Use the table templates given in the Appendix to help gather and present the data. Record the total capacitance , and annotate your schematic for later reference.

Delays in more complex logic systems

We are now in a position to account for the capacitive effects within individual logic gates themselves, and those arising from interconnect used to link gate inputs and outputs.

Consider carefully which of the various capacitative elements will contribute directly to the delays observed in the case of a multi-stage design such as the ring oscillator. Study the transistor level schematics of Figure 1 and elsewhere, and the nor2 layout annotated with parasitics.

D M Holburn April 2009 ICstudio v2005 130 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Use the table templates supplied in the Appendix to this Lab Guide to assemble and present these elements. Accordingly, update your schematic representing the cascaded gates of Figure 2. Annotate it to show all relevant contributions towards parasitic capacitance that affect delay. Some of these have been specifically mentioned above, while others have not, and you should think carefully about which contributions are likely to be of greatest significance in determining the speed of the gate. The table of specific capacitances (in Section II of this Guide, above) should be of help in deciding relative values.

A

B

Y

A

B

Y

A B Y A B Y

Figure 2 : Estimation of additional interconnect capacitance

The following section needs to be undertaken at the workstation.

D M Holburn April 2009 ICstudio v2005 131 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

III Extraction of parasitic capacitances using ICextract

10. Extract interconnect parasitic capacitance values using ICextract(M).

Before a proper simulation can be carried out it is necessary to determine the magnitudes of any parasitic components (for example, resistances or capacitances) inherent in the layout of the IC. ICextract provides facilities for extracting resistance and capacitance values in various forms, including lumped or distributed capacitances between pairs of layers as well as from each layer to substrate (ground). However, in this project we shall confine ourselves to determining only the lumped capacitances between interconnect and substrate

(since these are a primary determinant of rise and fall time).

ICextract has two modes of operation: Mask level (M) and Direct (D) . The former descends to the foot of any hierarchy and prepares a 'flattened' list of extracted parasitics for back-annotation to a transistor-level schematic. Directmode extraction inspects only interconnect at the highest hierarchical level and does not explore any sub-cells. For this work we shall use Mask Level extraction.

Important note : If you commence this section at the beginning of a session, you must first carry out an LVS using the procedure described in paragraph 4 above.

With ICgraph 's Design window active, revert to the IC Palettes menu, if necessary by clicking the Back option in the ICtrace(M) palette. Click on the

ICextract(M) item. The ICextract(M) palette appears.

If necessary, load the Mietec process and design rules by clicking on the Load

Rules item in the palette. Enter: $MIETEC_CMOS24_IC_RUL in the text box.

If you have a schematic window open on the logic, close it temporarily by giving the command (Palette Menu) > Logic > Close.

Click the Lumped item in the palette. When the Extract Mask Lumped

Parameters Dialogue box appears, click the Yes button for Specify Schematic

Source , and the Yes button for BackAnnotate . The dialogue box will enlarge at each click, disclosing additional options.

Set the BA Name field to flat_ba, and choose eddm for Source type . In the

Source Name field, enter the path to the Eldo viewpoint. No Navigator is available for this item, so you will need to key it in explicitly, for example

$CBT_WD/nor2t/Eldo_vpt1.

Change the entry in the Lumped Capacitance – Name field so that it reads cap_net (instead of icap_net ). Ensure that the Lumped Resistance and

Coupling Capacitance options (at the foot of the dialogue) are both set to No , but leave all other items as they are. OK the dialogue box. Extraction should proceed.

To view the results, give the command (Palette Menu) > Logic > Open . The

Logic Name should already be set to the appropriate viewpoint, but if not, enter or navigate to this. OK the dialogue box, and watch for the schematic window to appear. It should appear annotated in red with capacitance values (picofarads) at all key nodes. Enlarge the window, and study the values.

Are the capacitances similar to the values you estimated by hand? Comment.

Record the capacitances observed at the three main ports A , B and Y .

Note also the capacitance values given for the Vdd and Vss nets. How do you expect these to affect the operation of your design?

D M Holburn April 2009 ICstudio v2005 132 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

11. Verify that ICextract responds to changes in layout.

Refer to the section: Analysis of parasitic capacitances due to interconnect

(above), which considers the capacitance due to interconnect used to connect the output of the gate under consideration to other gate inputs.

Using ICstation 's layout commands, temporarily add to your layout a strip of interconnect. Imagine that you plan to connect the output port Y to the input ports A and B of a fictitious gate, placed adjacent to the first, and lay out the additional interconnect accordingly. (Only a reasonable approximation of the geometry is required). Do not save the modified layout. Re-run the ICextract utility, and observe and record the modified capacitance values.

Exit from ICstation . When prompted to save changes to the cell, be sure to choose the Discard option, so that the temporary interconnect is not saved.

12. Use DVE to connect back-annotated parasitics to the Eldo viewpoint.

You should still have a DVE session running from a previous phase. Restore its window on the screen. Open the Eldo viewpoint you created in paragraph 2. If you have no DVE session, use Design Manager to open a DVE session on the

Eldo design viewpoint created in paragraph 2.

Study the Design Viewpoint window. In addition to the reference to a backannotation object: Eldo_modfile.ba

, you should see listed an object entitled: flat_ba . This is the back-annotation derived from the ICextract session you performed. If you do not see this reference, speak to a demonstrator.

Close the design viewpoint using the command (Menu bar) > File > Close

Design Viewpoint .

Important. You may encounter difficulties in Eldo if you leave the design viewpoint open in DVE. However, you should leave your DVE session running in spare window, or minimised; you may need it later.

When your design runs cleanly through LVS and you have satisfactorily extracted parasitic capacitance information and back-annotated this to the design viewpoint, you are ready to carry out a simulation with Eldo .

13. Use Design Manager to check your viewpoint is ready for simulation

You should carry out the following check using Design Manager to confirm that all has gone well with your creation of the Eldo_vpt1 viewpoint.

In Design Manager, navigate to the new viewpoint (within the nor2t component).

Select it, and using the Popup menu available from the right mouse button, give the command: (Popup) > Explore > References . In the resulting screen you should see a reference to: MIETEC_CMOS24_ELDO_MODFILE (the upper case characters are significant).

NB : on closing this window you will have to start a new Navigator using:

(Menu Bar) > Windows , or using the menu palette.)

If you can see the reference described, you should be safe to proceed to Eldo in paragraph 14. If not, please mention this to a demonstrator before you continue.

D M Holburn April 2009 ICstudio v2005 133 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

IV Simulation of the schematic design using Eldo

In this section you will run the Eldo simulator to determine the electrical behaviour of your nor2 design when driven with typical signals. The results you obtain will give you a good indication of the efficiency of your design, and should show evenly matched rise and fall times of a few nanoseconds, dependent upon the details of your layout.

Running Eldo consists broadly of two distinguishable operations :

preparing power supplies, signals and other stimuli

running the simulation and inspecting the results.

Before you proceed with the Eldo section, you should have completed all previous sections in this guide, and you should have a Design Manager session and (preferably) a DVE session running.

14. Open Eldo on the back-annotated viewpoint.

Restore your Design Manager session to the screen. In the Navigator window, open up the nor2t object to expose the various design objects, including the Eldo viewpoint you created and back-annotated. Select this by clicking it, and use the method of data-centred invocation to start up Eldo on this object.

Note : You must start up Eldo on the specific design viewpoint object . In particular, do not attempt to start Eldo on the nor2t component, in the hope that it will somehow identify the correct design viewpoint! If you do, Eldo will generate a default viewpoint with no embedded Mietec device models, and you will be unable to run the simulation.

Watch the screen as Eldo starts up. Apart from the palette window, you should see two sub-windows appear; one containing the schematic corresponding to the viewpoint being modelled; the other displays simulator status messages. The schematic window should display the red back-annotations generated in

ICstation . If not, or if any other unexpected messages appear, speak to a demonstrator.

15.

Set up Eldo to perform a DC Sweep analysis on the nor2 gate

We shall determine the transfer function of the gate by holding input A fixed (at 0 volts), while varying input B over the range 0 - 5 volts. Before the simulation can begin, we must first set up some voltage and signal sources (referred to in Eldo as forces ). In most cases this can be achieved by selecting nets in the schematic, but some typing will also be required.

First we set up the power supply. In the schematic window, select the net to be connected to the positive VDD supply by clicking on it. Make sure the DC Mode palette menu is selected, and click on ( Palette Menu) > ADD FORCE . When the dialogue box appears, note the Signal identifier or net ID - it may be required later. Set the Type to DC and the Magnitude to 5. OK the dialogue box.

Now we set up a static voltage of zero at each of the inputs A and B . We shall later specify that B will be varied in order to determine a transfer characteristic.

Select one of these two nets in the schematic by clicking on it. Click on the

(Palette Menu) > ADD FORCE item. The corresponding name should appear in the Signal field of the dialogue box; if it does not, type it in. Enter 0 for in the

D M Holburn April 2009 ICstudio v2005 134 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Magnitude field, and type the name of the second net to be set in the field labelled: Other signals of the same DC force – e.g.

/A . OK the dialogue box.

Review the forces that have so far been applied by giving the command:

(Menu bar) > Report > Forces on Schematic . An Info Messages window pops up. Check the specification of each of the forces. Note that each force has a characteristic Forced Net identifier: note the IDs for the three forces.

16. Run the simulation to determine the transfer characteristic of the nor2 gate.

Now set up the simulation run. Click the SETUP ANALYSIS item in the palette menu. In the resulting dialogue box, select DC Sweep , and enter the force ID you noted in paragraph 15 for signal B . In the From , To and Increment Value fields enter 0 , 5 , and 0.1

respectively. OK the dialogue box.

Finally, determine which waveforms to keep for observation. In a large design it would be necessary to be selective, but in this case no serious penalty results from keeping them all. With the schematic window active, select inputs A , B , and output Y . Click the ADD KEEPS item in the palette menu. In the Add Keeps dialogue, click Selected and check the keep ALL schematic signals box. OK the dialogue. Give the command:

(Menu bar) > Report > Keeps to verify the information that is to be kept.

To run the simulation, click the RUN item in the palette menu. If all is well, the simulation should run within a second or two, and the Results palette menu should appear.

If a problem has arisen with the creation of the viewpoint, you may be greeted with messages like " Can't find models for TR_N and TR_P ". If you encounter this problem, please discuss it with a demonstrator before trying to continue.

To chart the results, with the schematic window active, select input B and output

Y ; then click the CHART item in the palette menu. You should see graphs including one of output voltage against input voltage. Note the availability of screen cursors (key F5 ) to help with quantitative measurement. It is also possible to print the active graph using the command: (Menu bar) > File > Print > Active window , using a procedure similar to that described in Lab Guide 5 for QuickSim

II . Please ask if you need further details for setting up printing.

From the graphs, determine the maximum linear amplification of the gate with respect to input B , i.e. (

V

V

Y

/

B

).

At what input voltage level is maximum linear gain achieved?

Consider the accuracy of the measured linear gain value. How might you set up the simulation conditions (paragraph 16) in a slightly different way in order to enhance the accuracy obtained?

Determine the input switching level (at which VY = VB).

Now determine the transfer function , gain and switching level relative to input A .

Estimate the noise margins (E1 course notes or see Weste & Eshraghian).

How might you use Eldo to determine the transfer function with both inputs being swept simultaneously (rather than just A )?

D M Holburn April 2009 ICstudio v2005 135 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

From the foregoing, you should be in a position to decide whether or not the circuit has suitable functional characteristics for use as a NOR gate. However, this analysis has given no information about the dynamic performance of the gate (i.e. its speed).

The following paragraphs detail how to carry out a transient response analysis of the nor2 design.

17. Set up a Pulse stimulus for use in transient analysis

In order to predict the rise and fall time of the nor2 gate, and hence the delay imposed by it on digital signals, we must carry out a transient analysis. In Eldo a transient response is constructed by evaluating nodal voltages and currents at intervals determined by a time-step until a specified stop-time is reached. It is necessary also to specify at least one input signal as a time-varying function.

Eldo offers several possibilities for this, including sinusoids, pulses, exponentials, or piece-wise linear waveforms. In digital circuit modelling, the most useful of these is the pulse waveform. To specify a pulse, several parameters are required.

These are illustrated by the waveform in Figure 3 below.

It is important to establish realistic values for the Rise and Fall times; however, for the time being, the suggested settings of 1ns will be satisfactory.

Figure 3 : Force Pulse Signal Parts

To set up the analysis, click the SETUP ANALYSIS item in the DC Mode palette menu. When the Setup Analysis dialogue appears, click Transient . Note that it is possible here to adjust the Stop Time and the Time Step ; however, these need not be changed for the moment. OK the dialogue box.

For the time being we shall keep the signal connected to input A fixed at 0 volts, and apply a pulse waveform to input B . Give the command: (Menu bar) >

Report > Forces , and verify that the signals applied at VDD and A are still correct. Correct these if necessary. With input B selected in the schematic window, click the ADD FORCE item in the palette menu. When the dialogue box appears, select the Pulse option, and fill out the dialogue box to generate a waveform to exercise the gate and cycle the output Y through each possible transition. Be sure to set the Initial Value and Pulsed Value to appropriate magnitudes, and be aware that the units of time are seconds unless qualified by the prefix n , etc. When all values are appropriately set, OK the dialogue box.

D M Holburn April 2009 ICstudio v2005 136 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

18. Carry out a transient analysis on the nor2 gate.

Use the RUN item in the palette menu to initiate the simulation.

Note : If you should observe the error message: " Internal timestep too small ", you may need to adjust either the rise/fall times of your pulse waveform, or certain other Eldo tolerance parameters. Please speak to a demonstrator.

To view the results, select in the schematic window the inputs and outputs required, then click the CHART item in the palette menu. You may wish to use cursors to help determine accurate rise/fall/delay times, or to generate a print-out.

When recording your results you must state the capacitance being driven, as without this information your results are meaningless.

Determine the output rise/fall time (10% to 90%) under these conditions.

Determine the delay between input stimulus and output response, by measuring the delay that elapses between the input signal passing through

VDD/2 and the output signal passing through the same level.

Determine a suitable PULSE force to apply to input A so that the combination of signals applied to A and B exercises the nor2 design through all possible input and output states. Compare the rise/fall delay times for every possible input combination.

If time permits, investigate the effect of varying the rise time/fall time of the applied pulse waveform(s).

Use the table templates in the Appendix to help with presentation of the data.

19. Determine the effect of external parasitic elements.

In an earlier section you evaluated ‘by hand’ the capacitance associated with the metal interconnect required to connect the output of the nor2 cell to the inputs of an adjacent nor2 stage (as in the ring oscillator), and thus determined the total capacitive load driven by the original gate. However, the transient response you just determined was for the nor2 cell totally isolated from any other circuits.

Under these conditions, which are not truly realistic, Eldo cannot be expected to give accurate values for the expected ring oscillator frequency.

One way to circumvent this would be to edit the nor2 layout temporarily, adding metal and other shapes typical of the kind of interconnect we might reasonably expect. ICextract could then be used to regenerate more accurate backannotations. If you wish to try this approach you may; however, we shall explore here a more convenient technique which will achieve the same objectives.

We shall instead edit the back-annotation information supplied to the design viewpoint, and re-run the transient response determination, in a form of heuristic

'what if' experiment.

With the schematic window active, select the output net Y . Give the command:

(Menu bar) > Edit > Property > Change...

The Change Properties dialogue should appear, listing the single property of that net which can be changed: cap_net , the capacitance property that was established by ICextract when it earlier applied the back-annotation data. This represents only the internal capacitance, due to interconnect inside nor2 . Select this property, and OK the dialogue box. A new, Change Property dialogue should appear. Edit the Value field so it contains a new capacitance value corresponding to the sum of the old value plus the external contribution, determined in paragraph 8. Record this

D M Holburn April 2009 ICstudio v2005 137 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation value, and OK the dialogue box. You should see the red annotation in the schematic update in consequence of the change you just applied. Give the command: (Menu bar) > Report > Design Changes , and confirm that the new listed back-annotations are consistent with your expectations.

Re-run the simulation, chart the transient response, and determine the new timing characteristics of the gate. Be sure to specify the capacitance being driven when you record your data. As before, if you should observe the error message:

" Internal timestep too small ", you may need to adjust either the rise/fall times of your pulse waveform, or certain other Eldo tolerance parameters. Please speak to a demonstrator.

20. Investigate the effect of varying supply voltage VDD.

The effect of the supply voltage VDD in determining the conductance of the transistor channel was discussed in an introductory sheet, and you may by now have had the opportunity to investigate the measured performance of a real ring oscillator at various different supply voltages. We shall use Eldo to try and model the performance of our ring oscillator design at a reduced supply voltage of 3 V, and hence predict the dependence of oscillation frequency on VDD. In order to investigate this using Eldo , it is necessary to modify the specification for the voltage source set up in paragraph 15, as well as the amplitude of the pulse stimulus set up subsequently for the transient analysis.

On the schematic, select the appropriate net corresponding to the VDD supply rail, and use the (Palette Menu) > ADD FORCE item to modify the supply voltage VDD to 3 V. If necessary, change the magnitude of the signal applied to input A so it lies within the range 0-3 V. Finally, select net B , and use the

FORCE item in the palette menu to change the amplitude of the pulse signal applied to 3 V. Use the (Menu Bar) > Report > Forces command to confirm these modifications have been correctly carried out. Carry out a transient analysis as in paragraph 18, and compare the results obtained. Compare these also with the results obtained from direct measurement on the experimental ring oscillator.

21. Investigate the effect of varying W/L.

The effect of aspect ratio (W/L) on worst-case gate delays has already been described. Careful choice of W/L is required to ensure that the delays corresponding to rising and falling signals are matched. You should by now have discovered how effective this matching process has been in your own case! In any event, we shall now briefly investigate the effect of modifying the W/L ratio for the p-channel transistors. As already discussed in paragraph 19, this could clearly be achieved by modifying the original design (the schematic in this case, rather than the layout); however, it is more convenient to carry out this experiment directly in Eldo . This can easily be achieved, because the information is actually transmitted to Eldo by means of the instpar property.

With the schematic window active, select one of the p-channel transistors. Give the command: (Menu bar) > Edit > Property > Change . When the dialogue box appears, select the instpar property for editing. Change L and/or W in such a way as to alter the aspect ratio by a factor 2-3. Repeat this procedure for the second p-channel transistor. Re-run the simulation and determine, and record, the new rise and fall times. If time permits, collect sufficient results to allow you to plot a graph showing the variation of delay time with W/L.

D M Holburn April 2009 ICstudio v2005 138 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Note: during the procedures described in paragraphs 18 onward, you may encounter one of the limitations of Eldo . When simulating circuits such as this with fast, but varying transient responses, Eldo is occasionally unable to achieve numeric convergence at points in the simulation corresponding to rapid changes at the input(s). You may find it necessary to alter the rise and/or fall times of the input pulse waveform or Eldo ’s tolerance parameters in order to obtain useful results.

22. Investigate other important sources of parasitic capacitance

Carry out this section if time permits. Otherwise proceed to paragraph 23.

So far we have looked in some considerable detail at the parasitic capacitances arising within the nor2 gate from metal and polysilicon interconnect. You can see for yourself the values of capacitance used by examining the output file generated by Eldo . To do this, give the command: (menu bar) Report > View

Outfile , In the resultant listing, study the section following the line beginning:

.OPTIONS

You should be able to reconcile most of the source, gate and drain connections to the MOSFETs (M) with the port names A , B , and Y ; comparison with the schematic in the ICGraph window should allow you to recognise all the interconnect capacitances (C) identified by ICExtract and back-annotated to the schematic. Refer to the supporting pamphlet: Analogue Simulation & Eldo for a simple explanation of the format used. Consult a demonstrator if you still have difficulty interpreting this listing.

However, there is a vital source of capacitance that has so far been completely overlooked; the capacitance due to the source and drain regions of each of the

MOS transistors. For a more complete discussion of the origin of these capacitances, see for example: Analysis and Design of Digital Integrated

Circuits

, by Hodges & Jackson, p 75. Manufacturer’s process data invariably includes coefficients that relate the capacitance to the area and perimeter of the source and drain – in the Eldo models in use here these are the parameters CJ and

CJSW. You should be able to identify these parameters in the early part of the output file generated by Eldo . Eldo is in fact perfectly capable of evaluating these contributions to parasitic capacitance; however, their effect can only be quantified if the area and perimeter of each source and drain (in contact with the substrate) is known. In the present case this information is not available from ICExtract , however, and can only be provided via the instpar property.

Use the layout plot for the nor2 cell to estimate the area (AS and AD) and perimeter (PS and PD) of each source and drain of the four transistors.

Record and tabulate your results (use the templates given in the Appendix).

Update the schematic to change the instpar parameter correspondingly. You can do this in a temporary way, by following the procedure of paragraph 21, or, more permanently, by updating the original schematic in Design Architect . A typical modified instpar might appear as below :

W=20U L=3U AS=400P PS=60U AD=400P PD=60U

Note the use of the suffix: P to signify a factor of 10

-12

( P ico).

With the instpar parameters updated, re-run the transient response and determine the new (and much more realistic) delay for rising and falling edges.

D M Holburn April 2009 ICstudio v2005 139 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

What is now the capacitance being driven? How do these figures compare with the delays measured in sections 18 and 19?

D M Holburn April 2009 ICstudio v2005 140 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

23. Collect and present the results from this session.

Gather the accumulated simulation results together and present them in an appropriate form using tables or graphs – a number of suggested templates are given in the Appendix. You should include as many as possible of the following conditions :

DC Sweep Analyis, providing data about the gate’s transfer function

transient response with internal circuit parasitics (paragraph 18)

transient response with internal/external parasitics (paragraph 19)

transient response incorporating other effects (paragraphs 20 - 22)

Be sure to state very clearly the conditions applying to the simulations. For example, in transient responses, the results are meaningless if the aggregate driven capacitance is not quoted. It is very easy to ignore capacitive effects and get an impossibly optimistic figure for the delay. You must take care to avoid falling into this trap.

Include also in your tabulated results any relevant results obtained from measurement on the experimental ring oscillator.

24.

Use results from Eldo to model the behaviour of your design with VHDL

Select those simulation results you consider to be the most realistic and characteristic for your NOR2 when used in the ring oscillator design (explaining why). Then use the procedure of Laboratory Guide 2 ( Functional simulation with Modelsim ) to model the overall system behaviour of your ring oscillator design based on the predicted timing characteristics of your nor2 cell. Hence determine the key timing parameters of the proposed ring oscillator module designed in this way.

Conclusion

The last few paragraphs should have given you some insight into the issues that most directly affect the behaviour of fast CMOS logic gates. We shall leave the verification process at this point, but should perhaps observe that there is considerably more that could be done.

Although we have made reasonable estimates of interconnect capacitances, the real ringarray has not yet been laid out, so we do not know what parasitic capacitances might arise owing to the interconnect used to link outputs to inputs, etc. A slightly different kind of extraction can elicit this data once the layout has been performed.

Eldo is not suitable for modelling the entire design, so at this stage, having assured ourselves of the satisfactory performance of our nor2 cell, we might develop a

QuickSimII timing model for it and use that simulator for the remaining work.

The remainder of the project is concerned with the use of semi-custom tools associated with ICstation , to prepare for the entire top_level design a set of masks ready for despatch to the fabrication facility.

D M Holburn April 2009 ICstudio v2005 141 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

Laboratory Guide 7 – Appendix I

The following suggested table templates may be of help in the presentation of material in the sections of the Final Report relating to this Lab Guide. Please adapt the formats to meet your own specific requirements.

Interconnect capacitances

Index Interconnect type Description Area /

m 2 Capacitance / fF

1

2

3

….

A similar table may be used to present calculated or extracted capacitance values.

Capacitances associated with ports

This table may help with assessment of the parasitic capacitance being driven by each gate output owing to coupled interconnect and input ports.

Port Identifier Area references Capacitances / fF Total Capacitance / fF

A similar table may be used to present calculated or extracted capacitance values.

Areas and perimeters of transistors

Transistor ref.

Source Drain Gate

Area (

m 2 ) Perim (

m) Area (

m 2 ) Perim (

m) Area (

m 2 ) Perim (

m)

Rise, Fall and Delay times for transient inputs

Input conditions

O/P

Rise/

Fall

Original setup

Rise/fall ns

Delay ns

External capacitances included

Rise/fall nsl

Delay ns

Reduced supply voltage

Rise/fall ns

Delay ns

A falls

Doubled W/L ratio for p

Rise/fall ns

Delay ns

Other conditions

Rise/fall ns

B falls

Both fall

Rise

…..

Similar tables may be used in other parts of the report, e.g. in Lab 8 to present area & number of vias for various procedures applied to flattened or hierarchical layouts.

Delay ns

D M Holburn April 2009 ICstudio v2005 142 SB1lab7.doc

Computer-based project in VLSI Design Lab Guide 7 - Verification & Simulation

D M Holburn April 2009 ICstudio v2005 143 SB1lab7.doc