Manuscript submitted to Applied Physics Letters

advertisement

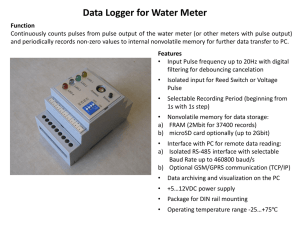

Supplementary Information Correspondence and requests for materials should be addressed to Z. B. Yan (email: zbyan37@gmail.com) or to J. –M. Liu (email: liujm@nju.edu.cn). Coexistence of high performance resistance and capacitance memory based on multilayered metal-oxide structures Z. B. Yan*, and J. –M. Liu* Laboratory of Solid State Microstructures, Nanjing University, Nanjing 210093 (P. R. China) As a voltage pulse (U0) is applied to an RC series circuit, it is known that the real voltage drop on the capacitor (U) will be delayed due to the charging effect, following a function U=U0[1-exp(-t/)] with =RC. Hence, a large value possibly hinders the application of a short pulse onto the capacitor. However, this is not the case in our speed measurement. The Au/DMO/NSTO/Au device is recognized as two serial-connected RC parallel circuits, as illustrated in Figure 2(d). The capacitance of the Au/DMO/NSTO part (Cn~1.1nf) is three orders of magnitude larger than that of the NSTO/Au memory junction (Cm: between 0.7pf and 2.7pf). As the device is at the LRS, the resistance of the Au/DMO/NSTO part (Rn~710k) is much larger than that of the NSTO/Au junction (Rm5.3k) and the capacitance of the device mainly comes from Cn. Therefore, ~RmCn~5.3k1.1nf=5.8s, which is much longer than the 8ns-width of the input pulse and consequently hinders the actual voltage-drop on Cn capacitor during the short pulse duration. Hence, the short pulse is mainly dropped onto the NSTO/Au memory junction during the 8-ns pulse duration. As the device is at HRS, the resistance of the NSTO/Au junction (Rm~1.1109) is more than three orders of magnitude larger than Rn, which causes the most voltage-drop onto the NSTO/Au junction. Besides, due to the large Cn that hinders the voltage-drop to the Au/DMO/NSTO part, is mainly contributed by RrCm. Here, Rr<100, is the internal resistance of generator plus with the line and the contact resistances. Therefore, ~RrCm<1000.7pf=70ps, which is much short than the pulse width (8ns). Hence, one can 1 argue that the voltage is really dropped onto the NSTO/Au junction without obvious delay during the short pulse duration. The above results are verified by the electric circuit simulation by using NI Multisim 12.0 software. The simulation results are shown in Figure S (a) and (b) below. The red and green waves indicate the voltage waveforms of the device and the NSTO/Au junction respectively, which are almost coinciding with each other. Hence, the 8-ns-width voltage pulse is really applied to the NSTO/Au memory junction no matter the device is at the HRS or the LRS. (a) HRS (b) LRS Figure S. The simulation results as the device is at (a) the HRS and (b) the LRS respectively. The signal frequency is 20MHz, the duty cycle is 15%, and the rise/fall time is 0.5fs. It is noted that the red line wave is somehow covered by the green line wave. 2