Q3. VHDL, Sequential VHDL

advertisement

INGENJÖRSHÖGSKOLAN

Högskolan i Jönköping

Tentamen i Kundanpassade kretsar för Em3

Exam in Custom Designed Integrated Circuits

(Med lösningsförslag)

Datum/Date: 2003-01-08

Tid/Time:

8.00 – 13.00

Lokal/Room: E170

Hjälpmedel:

Ordbok / Dictionary is allowed

Appendix A. VHDL-syntax, 447-457 (included).

Appendix B VHDL-package, 458-466 (included).

Appendix C Key words , 467 (included)

Betyg

Grades:

3 / Godkänd /Passed 10 – 14,5

4

15 – 19,5

5

20 - 25

Max poäng /

Max credits: 25

1

2

3

4

5

6

7

3

3

3

3

6

4

3

25

Examinator /

Examination: Alf Johansson 15 74 78 / 0705 43 98 44

Answers in Swedish or English. Give the answers on this paper if there is enough space

otherwise on a separate paper.

Namn / Name:______________________________________________

Tentamen i Kundanpassade kretsar 2003-01-08.

Page 1

INGENJÖRSHÖGSKOLAN

Högskolan i Jönköping

Q1. VHDL, Concurrent VHDL

Calculate the value of the signal vector a (when the circuit is stable).

architecture

signal a:

begin

a(7

a(4

end behav;

(3p)

behav of T1 is

std_logic_vector(7 downto 0);

downto 4)<= "01" & "10";

downto 0)<=(others=>'1');

a= 011X1111

Q2. VHDL, Signals and variables

The initial values for signals and variables in VHDL-simulations are the left-hand values

in the definitions. For std_logic the initial value is ‘U’. The same rules are valid for integer

ranges.

What is the value of x1 when process p1 stops?

(1p)

What is the value of x2 when process p2 stops?

(1p)

What is the value of v1 when process p3 stops?

(1p)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_signed.all;

entity uppg2 is

end;

architecture behav of uppg2 is

signal x1: std_logic_vector( 3 downto 0);

signal x2: integer range -8 to 7;

begin

p1:process

begin

for i in 0 to 3 loop -- start value 'U' loop takes no time

x1<=x1+1;

-- x1 = -'U'during loop

end loop;

-- x1 = 'U'after loop and 'X' after 1 delta

wait;

-- whole process takes one delta

end process;

-- x1 = 'X' at wait ('U'is also correct)

p2:process

begin

for i in 0 to 3 loop -- start value –8, loop takes no time

x2<=x2+1;

-- x2 = -8 during loop

end loop;

-- x2 = -8 after loop and –7 after 1 delta

wait;

-- whole process takes one delta

end process;

-- x2 = -7 at wait

p3:process

variable v1: integer range –8 to 7;

begin

for i in 0 to 3 loop -- start value -8

v1:=v1+1;

-- v1 = -7, -6, -5, -4

end loop;

wait;

-- v1 = -4 at wait

end process;

end behav;

Tentamen i Kundanpassade kretsar 2003-01-08.

Page 2

INGENJÖRSHÖGSKOLAN

Högskolan i Jönköping

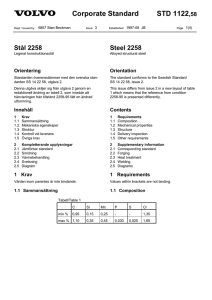

Q3. VHDL, Sequential VHDL

Describe in VHDL the circuit shown below. The D-FlipFlops are clocked on the rising edge

of clk. load is an synchronous load signal (active high). When load is 0 the 0-input of the

multiplexor is transferred to the mux output and when load is 1 the 1-input of the mux is

transferred to the mux output. Write the missing part of the architecture.

(3p)

load

0

1

D Q

+

0

1

D Q

0

1

D Q

sout

clk

library ieee;

use ieee.std_logic_1164.all;

entity sreg is

port (clk,load: in std_logic;

sout: out std_logic);

end;

architecture rtl of sreg is

signal q: std_logic_vector(2 downto 0);

begin

process(clk)

begin

if clk'event and clk='1' then

if load='1' then

q<="010";

else

q(2)<=q(1);

q(1)<=q(0);

q(0)<=q(2);

end if;

end if;

end process;

sout<=q(2);

end rtl;

Q4. VHDL, Sequential VHDL

How many flip-flops are created in the following VHDL code? Motivation is required for

each assumed flip-flop. Correct answer without motivation will give no credits. Specify

which signal or variable that creates flip-flops and how many for each object.

(3p)

library ieee;

use ieee.std_logic_1164.all;

entity T4 is

port(clk, reset: in std_logic;

Tentamen i Kundanpassade kretsar 2003-01-08.

Page 3

INGENJÖRSHÖGSKOLAN

Högskolan i Jönköping

a: in std_logic_vector(7 downto 0);

q: out std_logic_vector(3 downto 0));

end;

architecture rtl of T4 is

begin

process(clk,reset)

variable v1: integer range 0 to 7;

begin

if reset='1' then

v1:=0;

q<="0000";

elsif clk'event and clk='1' then

v1:=v1+1;

-- variable v1 read before written =>

if v1=3 then

-- 3 flip-flops (range 0 to 7)

q<=a(3 downto 0); -- 4 flip-flops generated for q

else

q<=not a(3 downto 0);

end if;

end if;

end process;

end rtl;

Answer: Number of flip-flops generated = 3+4 = 7

Q5. Finite State Machines, FSMs

Finite State Machines are a convenient way to design sequential logic. The mono-flip-flop

in this question will illustrate the principles behind FSMs.

P1

P2

P3

state reg

decode

inputs

next state

a) Draw a block diagram for a Moore type FSM (three blocks)

b) Draw a state diagram for a digital mono-flip-flop (MFF). The MFF is clocked

by the clock signal clk. The period of clk is Tclk. When the trig input signal

trig goes high the MFF output q shall be set high for a time period of 2xTclk.

The MFF can only be retrigged if trig goes low before it goes high again.

Ttrig-high>Tclk and Ttrig-low>Tclk are requirements on the trig signal.

c) Write the VHDL code for the MFF described in b). Only the signal clk can be

used as clock in clocked processes. Use one clocked process and two

combinational processes.

Tentamen i Kundanpassade kretsar 2003-01-08.

Page 4

outputs

(1p)

(2p)

(3p)

INGENJÖRSHÖGSKOLAN

Högskolan i Jönköping

trig=0

reset=1

s0

0

trig=1

s1

1

trig=0

s2

1

s3

0

trig=1

library ieee;

use ieee.std_logic_1164.all;

entity mff is

port ( clk, reset, trig: in std_logic;

q: out std_logic);

end;

architecture rtl of mff is

type state_type is (s0,s1,s2,s3);

signal state, n_state: state_type;

begin

p2:process(clk,reset)

begin

if reset='1' then

state<=s0;

elsif clk'event and clk='1' then

state<=n_state;

end if;

end process;

p1:process(state, trig)

begin

case state is

when s0 => if trig='1' then n_state<=s1; end if;

when s1 => n_state<=s2;

when s2 => n_state<=s3;

when s3 => if trig='0' then n_state<=s0; end if;

when others => n_state<=s0;

end case;

end process;

p3:process(state)

begin

case state is

when s1 | s2 => q<='1';

when others => q<='0';

end case;

end process;

end rtl;

Tentamen i Kundanpassade kretsar 2003-01-08.

Page 5

INGENJÖRSHÖGSKOLAN

Högskolan i Jönköping

Q6. Design methodology

a) What is synthesis and what is the output from this step? Mark also this action in

the Y-chart as an arrow between two domains

b) What is technology mapping (implementation) and what is the output from this

step (if we are designing a FPGA-circuit)? Mark also this action in the Y-chart

as an arrow between two domains.

c) What does that mean that a node is observable? Testable?

d) What does that mean that a node is controllable? Testable?

synthesis

Structural

Behavioral

technology

mapping

Physical

6a: (short) Synthesis translates VHDL code on RTL level to a netlist (logic synthesis).

Example: (VHDL (RTL) => .edif file)

6b: (short) Technology mapping translates a netlist to a physical description for a special

technology.

Example: (.edif => bitmap file for a FPGA)

6c: (short) The state of an internal node can be decided from outside. This is necessary for

testability.

6d: (short) The state of an internal node can be set from outside. This is necessary for

testability.

Tentamen i Kundanpassade kretsar 2003-01-08.

Page 6

(1p)

(1p)

(1p)

(1p)

INGENJÖRSHÖGSKOLAN

Högskolan i Jönköping

Q7. Test benches

a) What is a testbench regarding VHDL?

b) In a testbench you shall simulate a bus signal that can be driven by several drivers.

The drivers are of open collector type. Write a functional VHDL-model for the

circuit that is shown below. (Hint: the resistor can be modelled as a weak std_logic

value. An open collector driver has the values “active low” and “high impedance”)

(1p)

(2p)

Answers:

7a (short): A testbench is VHDL component that instantiates other VHDL components

that shall be tested. A testbench can generate input signals and verify output signals.

+

Resistor

a1

a

a2

Open collector drivers

architecture tb of testbench is

signal a,a1,a2: std_logic;

begin

a<='0' when a1='0' else 'H'; -- solution 1

a<='0' when a2='0' else 'H';

or

a<='0' when a1='0' else 'Z'; -- solution 2

a<='0' when a2='0' else 'Z';

a<='H'; -- model of resistor

end tb;

Tentamen i Kundanpassade kretsar 2003-01-08.

Page 7