ECE 1315 – Digital Systems

advertisement

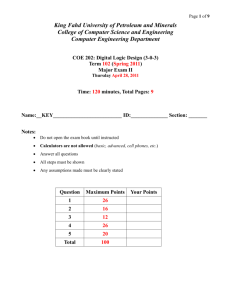

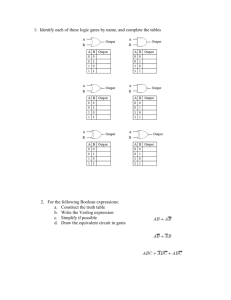

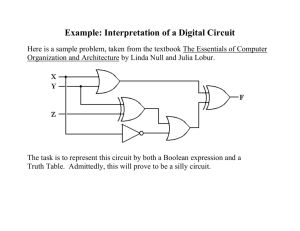

ECE 1315 – Digital Systems Lab Exercise 0 – Introduction to Logic Gates and LogiScan As performed by: Scott Norr September 9, 2009 Introduction The 7400 Logic Family uses TTL logic to implement Boolean Logic gates and other digital devices. The LogiScan Circuit Exerciser is a platform that dynamically tests all states of combinational logic circuits and displays the results on a personal computer. Hypothesis: Using a breadboard, some wire, the 7400 series logic family and a Logiscan Circuit Exerciser, it is possible to implement four Boolean logic functions, minimize the number of gates used, and verify the accuracy of their outputs. Equipment 1 – 74LS04 “Hex Inverter” 1 – 74LS32 “Quad OR” 1 – 74LS08 “Quad AND” 1 – Prototyping Board 1 – LogiScan Circuit Exerciser 1 – Personal Computer with LogiScan Software Procedure Four logic algorithms, each using two binary variables, were presented for experimentation. Each algorithm was implemented using the 7400 Logic Family and tested using the LogiScan circuit exerciser. It was necessary to convert the algorithms to Boolean expressions in order to implement them. The four algorithms and the corresponding Boolean expressions are listed in Table 1 below: Table 1: The Four Algorithms and Corresponding Boolean Expressions Function Logic Algorithm Boolean Expression F0(X1,X0) F1(X1,X0) F2(X1,X0) F3(X1,X0) F0=1 if X1=1 OR X0=1, else 0 F1=1 if X1=1 AND X0=1, else 0 F2=1 if X1=1 AND X0=0, else 0 F3=1 if X1=X0, else 0 F0=X1 OR X0 F1=X1 AND X0 F2=X1 AND X0’ F3=F0’ OR F1 All four Boolean expressions were implemented simultaneously on a breadboard, using three logic chips, the 74LS04, ’08 and ’32. Care was taken to minimize the number of logic gates used on these S.Norr Page 2 chips. For example, an OR gate was used to create Function 0 and was reused as part of Function 3, using fewer gates than would otherwise be needed. A schematic diagram of the four functions, as implemented in hardware is shown as Figure 1. Figure 1: All Four Functions as Implemented in 7400 Series Hardware A truth table was constructed by hand to verify the proper output of each algorithm. The truth table was checked against the output of the LogiScan software. This truth table is shown as Table 2 below: Table 2: A Truth Table for Each Algorithm X1 0 0 1 1 S.Norr X0 0 1 0 1 F0 0 1 1 1 F1 0 0 0 1 F2 0 0 1 0 F3 1 0 0 1 Page 3 Any errors in the hardware implementation, identified by discrepancies between the truth table and the LogiScan output were traced and corrected. The above truth table is consistent with the experimental results generated by the LogiScan output. Conclusion This lab exercise provided several learning opportunities. It introduced the experimenters to the 7400 Logic Family, provided basic instruction in wiring logic gates on a prototyping board and required the proper use of the LogiScan circuit exerciser. In addition this lab initiated the process of learning how to implement logic expressions in hardware and generating truth tables. All four logic functions were successfully implemented using the 7400 Logic Family and the outputs verified with LogiScan. The number of gates used to implement the four logic functions was 6 logic gates. Attachments 1. S.Norr Lab Exercise Sheet with Instructor Signature Page 4