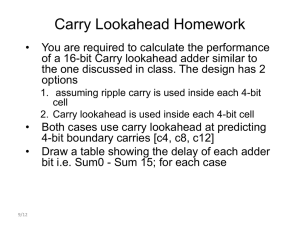

ECE 551 - Digital System Design & Synthesis Exercise 2

advertisement

ECE 551 - Digital System Design & Synthesis

Exercise 2 - Fall 2001

Write in the answer at A: for each of the following questions and bring to Wednesday’s

class whether complete or not for use in the discussion.

NOTE: Delays are in ns unless otherwise specified.

Delay Uses and Types

Give four specific uses for delay in Verilog simulations that correspond roughly to design

stages.

A:

A:

A:

A:

What are the three types of delay that can be specified in Verilog?

A:

A:

A:

Relation of Transitions to Delay

Rising Delays - final value of 1

Give the three distinct transitions that correspond to rising delays.

A:

Falling Delays - final value of 0

Give the three distinct transitions that correspond to falling delays.

A:

Turn-off Delays - final value of z

Give the three distinct transitions that correspond to turn-off delays.

A:

The type of transition (Rising/Falling/Turn-off) for delay is associated with the

change on the output

The rising delay is the time it takes for the output value to rise from the first value in

the transition to the second value in the transition. TRUE FALSE Explain

A:

Gate Propagation Delay (Inertial) - Examples

No delay value - default - delays are all 0.

nor (z, x1 x2)

Delay_value - unsigned_number = 1 - unit delay

nor #1 (z, x1, x2);

1

Delay_value - unsigned_number 1 - prop delay

nor #5 (z, x1, x2);

Delay_value - parameter_identifier - allows easy change of delay value

nor #nor_delay (z, x1,x2);

What is the delay from input A to output Y in the following circuit assign unit time of

1ns.

NOR #3 X1 (D, A, B, C),

#4 X2 (Y, D, E, F);

A:

ns

Gate Propagation Delay (Inertial) - Examples

Delay_value2 - unsigned_number - rising delay, falling delay

Describe the delays for: nor #(1,2) (z, x1, x2).

A:

Delay_value3 - unsigned_number - rising delay, falling delay, turnoff delay

Describe the delays for nor #(3,2,4) (z, x1, x2).

A:

Delay_value3 - constant_mintypmax_expression - rising delay - min:typ:max, falling

delay - min:typ:max, turnoff delay - min:typ:max

Describe the delays for nor #(2:3:4, 1:2:5, 2:4:6).

A:

Gate Propagation Delay (Inertial) - More

Constant_expression is quite complex - see Formal Syntax in text

Describe the delays for nor #(3.2:3.5:4.0, 4.1:4.5:5.2, 5.1:5.5:6.2).

A:

Describe the delays for nor #(nor_r_m : nor_r_t : nor_r_x, nor_f_m : nor_f_t :

nor_f_x, nor_t_m : nor_t_t : nor_t_x).

Describe the delays for nor #(del_switch ? nor_d_1 : nor_d_2).

A:

See Table 6.1, p. 135 of text.

What are delays for x and z values within transitions?

A:

Simulation Time Scales

Compiler Directive `timescale <time_unit> / <time_precision>

2

time_unit - the time multiplier for time values

time_precision - minimum step size during simulation - determines rounding of

numerical values

Allowed unit/precision values:

{1| 10 | 100, s | ms | us | ns | ps}

Table 6.3 in text contains errors

Simulation Time Scales (continued)

Example:

`timescale 10ps / 1ps

nor #3.57 (z, x1, x2);

What is the nor delay used in the simulation?

A:

Different timescales can be used for different sequences of modules

The smallest time precision determines the precision of the simulation.

Net Delay (Transport)

Delay assigned to net such as wire

Type of delay (inertial or transport) defined by object assigned to.

Example - Structural:

`timescale 10ps /1ps

wire #4 N25;

nor #(20,30) GA (N25, x1, x2), GB (z, N25, X3);

What is the delay for a rising output from x1 to z?

A: ps

What is the delay for a rising output from x1 to z?

A: ps

Net Delay (Transport)

Example - Continuous Assignment

`timescale 10ps /1ps

wire #4 N25;\\transport delay

assign #(20,30) N25 = ~ (x1 | x2); \\inertial delay

For a rising output, what is the delay from x1 to N25?

A: ps

Example - Implicit Continuous Assignment

`timescale 10ps /1ps

wire #(24,34) N25 = ~ (x1 | x2); inertial delay instead of transport delay for wire

For rising output, what is the delay from x1 to N25?

A: ps

Gate Propagation Delay (Inertial) - Shortcoming

Gate delays are uniform from every gate input to a gate output - not true in real MOS

3

circuits due to physical gate layout.

Workaround to model this detail: Use module with specify block

Pulse width rejection (for inertial delay) and delay value are tied together.

Workaround 1: Use combination of gate and wire delay

Workaround 2: PATHPULSES$ specification parameter in specify block

These approaches are incorporated in Module Delay and Inertial Delay Effects and Pulse

Rejection sections in the book.

Module Delay

Methodology to specify delay for behavioral descriptions

Specify Block

Declares paths and assigns delays to path

Path delay values can override structural delays

Supports back-annotation of delays after layout

Module Delay - Example

Add to module:

specify

(x1, x2 *> z) = (18:25:33, 24, 31, 40);

endspecify

Describe the delays specified.

A:

Module Delay Path - Simple

Specifies a path by identifiers of source and destination

=> specifies parallel path - establishes a vector path from vector source to vector

destination on a bit-wise basis. For n-bit vectors, n paths

*> specifices full path - establishes a path from each source bit to each destination bit.

For n-bit vectors, n2 paths.

What delays are specified by the following examples:

Parallel (x => z)= (5) //where x and z are 2-bit vectors.

A:

Full (x1,x2 *> z1, z2) = (5,4) where x and z are 2-bit vectors.

A:

Module Delay Path - Edge-Sensitive

Source is an edge transition

Useful for delays from clock edge to register output and beyond

Example: PETDFF Add to module:

specify

(posedge clock *>(Q:D)) = (3, 2);

(clear, preset *>Q) = (2,1);

4

endspecify

Describe the delays for this flip-flop.

A:

Module Delay Path - State-Dependent

Path is state-dependent if it exists only for a certain condition satisfied.

Useful for latch specification and beyond.

Example: Clocked latch - Add to module:

specify

if (clk) (D *> Q) = (3, 2);

endspecify

Describe the delays specified for this latch.

A:

Example: PETDFF - Add to module:

specify

if (!preset && !clear) (posedge clock *>(Q:D)) = (3, 2);

endspecify

Describe the delays specified for this flip-flop.

A:

5