A VPI-based IP Core Serial Fault Simulation and Test Generation

advertisement

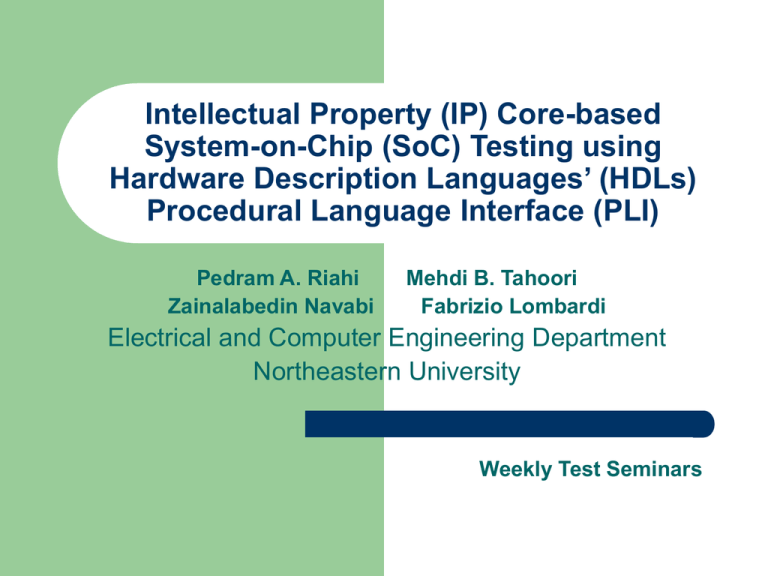

Intellectual Property (IP) Core-based

System-on-Chip (SoC) Testing using

Hardware Description Languages’ (HDLs)

Procedural Language Interface (PLI)

Pedram A. Riahi

Zainalabedin Navabi

Mehdi B. Tahoori

Fabrizio Lombardi

Electrical and Computer Engineering Department

Northeastern University

Weekly Test Seminars

Introduction

2

System-on-Chip (SoC)

SoC Testing

Present Solutions

Hardware Description Languages (HDLs)

SoC Testing using PLI

Benchmarks

Conclusion and Future Works

Northeastern University

Weekly Test Seminars

System-on-Chip (SoC)

Complex Functional Blocks

System-on-Board

Core:

Core 1

– μP/μC

–

–

–

–

–

–

3

DSP

Memory

Function-Specific

Logic Element

Communication

Peripheral

Analog Device

Northeastern University

Core 2

Memory

User Logic

Core 4

Core 3

Weekly Test Seminars

System-on-Chip (SoC)

Reusable Cores

Core Types:

–

–

–

High

Soft

Soft (Synthesizable)

Firm

Hard

Intellectual Property (IP)

–

Felexibility

Firm

Hard

In-house cores

Low

Low

4

Northeastern University

Predictability, Performance,

Complexity

Weekly Test Seminars

High

SoC Testing

Traditional Test Methods

Core-Level Testing

–

–

Design For Test (DFT)

Automatic Test Pattern

Generation (ATPG)

Final Circuit

Add

More

Testability

Circuitry

Macro

Subassembly

Chip-Level Testing

–

–

Justifying Test Sequences

Propagating Test Response

Add

Testability

Circuitry

Leaf Macro

5

Northeastern University

Weekly Test Seminars

Present Solutions

Core-Level Testing

–

–

–

–

–

6

System Chip’s Functional Test

Direct Access (I/O Muxing)

Local Boundary-Scan or Collar Register

Full-Scan / Built-in-Self-Test (BIST)

Proprietary Solution

Chip-Level Testing

Northeastern University

Weekly Test Seminars

Present Solutions

Full-Scan / Boundary-Scan (FScan-BScan)

Core 1

Core 2

Core 3

User Logic

Core 1

Core 2

Core 3

User Logic

Core 4

BScan

Interface

FScan-BScan

7

Northeastern University

Core 4

BScan

Interface

Full- or Partial-Isolating

Rings / Control Points

Weekly Test Seminars

Present Solutions

Full-Scan / Test Bus (FScan-TBus)

Test Bus / Boundary-Scan Chain

POs

TAP

Core 1

Core 2

User Logic

Core 3

Core 4

PIs

8

Northeastern University

TAP Linking

Core 1

TAP

Core 2

User Logic

T

A

P

TAP

Core 3

Core 4

BScan

Interface

Weekly Test Seminars

Present Solutions

Binary Decision Diagram (BDD)

Partial Netlist / Partial Boundary Scan

Core

1

9

Core

2

Core

under

Test

Northeastern University

Core

3

Core

4

Core

5

Weekly Test Seminars

Present Solutions

Core Transparency

Core 1

Core 2

Core 3

User Logic

Core 4

FPath

10

Northeastern University

Core 1

Core 2

Core 3

User Logic

Core 4

HScan

Weekly Test Seminars

Present Solutions

IEEE P1500

BIST

Chip-Level Testing

–

–

–

11

Parallel Direct Access

Serial Scan Access

Functional Access

Northeastern University

Weekly Test Seminars

Hardware Description Languages

(HDLs)

VHDL

Verilog

Procedural Interfaces:

–

–

VHPI

VPI

12

Cadence NC-Verilog

C Platform

Northeastern University

Weekly Test Seminars

SoC Testing with VPI

VPI-based

Test Environment

–

VPI-based

Fault Simulation

–

Core

Verilog Analyzer

Verilog Analyzer

Single Stuck-at Fault

Serial

VPI Task

VPI-based

Test Generation

13

Testbench

Intermediate Format

Verilog Simulator

Random Pattern

Northeastern University

Weekly Test Seminars

TopModule(W)

SM

M1(B)

Fault Simulation

with VPI

M2(B)

M4(B)

S

B

M3(B)

M4(B) M6(B)

Flat (nonMixed-Level)

Mixed-Level

S

S

B

B

BM

M1(W)

Structural Level

SM

BM

M2(W)

SM

M4(B)

M4(W)

M5(B) M6(B)

S

S

S

S

B

B

B

B

Behavioral Level

Hot

Wrapper Structure

14

Northeastern University

BM

M3(W)

M5(W) M6(W)

S

S

S

B

B

B

Weekly Test Seminars

Fault Simulation with VPI

Proposed VPI Tasks for Serial Fault Simulation

–

$faultlist

Node Type: reg, net

Node Name: ~.module_name/node_name

Stuck-at: sa0, sa1

–

–

–

–

–

–

–

15

Not Injected

Injected but not Detected

Partially Detected

Detected

$faultinjection, $faultrelease

$preinjection, $postrelease

$updatefaultlist

Northeastern University

Weekly Test Seminars

Test Generation with VPI

Proposed VPI Tasks for Directed Random Pattern

Test Generation

–

–

–

–

$faultcoverage

$morefault

$decide

$readstatus, $restorestatus

–

–

–

16

Status: 0, 1, X, Z

$randomvector

$saveoutput, $compareoutput

$savevector

Northeastern University

Weekly Test Seminars

Test Generation with VPI

Initialization

doread := true;

$faultlist;

while !($faultcoverage(coverage) satisfied) {

if (doread) $readstatus;

$randomvector(depth);

$readmem;

for (all vectors) { Apply Vector; $saveoutput; }

… Fault Injection and Simulation

… Decide }

17

Red is just required for Sequential Designs

Northeastern University

Weekly Test Seminars

Test Generation with VPI

Fault Injection and Simulation

Lindex := 0;

while ($morefault) {

$restorestatus;

$faultinjection(1);

flag := true;

for (all vectors and flag) {

Apply Vector;

if ($compareoutput == detected) {

$updatefaultlistone(1);

flag := false; Lindex := Largest index; }

$faultinjection(2); }

18

Northeastern University

Weekly Test Seminars

Test Generation with VPI

Decide

if ($decide(limit) == GOOD) {

$savevector;

$updatefaultlist(2);

if (Lindex > depth) {

$restorestatus;

for (all vectors that index < Lindex) Apply Vector; }

doread := true; }

else {

$restorestatus;

$updatefaultlist(3);

doread := false; }

19

Northeastern University

Weekly Test Seminars

Benchmarks

20

Flat Serial Fault Simulation (PARWAN: WRTLT’02,

ISCAS85-89: NATW’03)

Behavioral Operations vs. Primitive Gates and Mixed

Level Serial Fault Simulation (PARWAN: ESA’03,

ISCAS85: ATS’03)

Higher Level Behavioral Description and Directed

Random Pattern Test Generation (ITC’04)

Generating a Series of SoC Benchmarks

Northeastern University

Weekly Test Seminars

Conclusion and Future Works

A Methodology for SoC IP Core Testing

–

–

Eliminating Traditional Hardware Wrappers

–

21

Mixed-Level Serial Fault Simulation

Directed Random Pattern Test Generation

Delay and Area Overheads

VPI-based Deductive or Concurrent Fault Simulation

VPI-based PODEM and D-Algorithm

Mixed-Mode SoC Testing

Northeastern University

Weekly Test Seminars