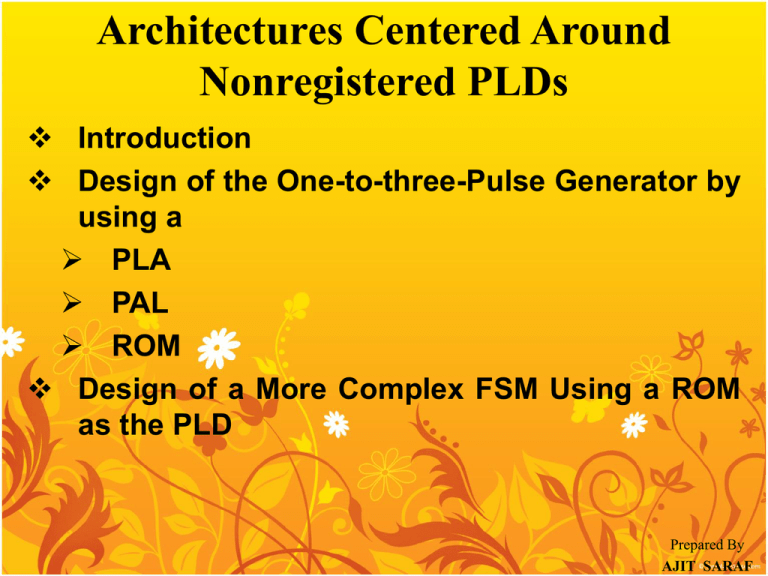

2) Non-Registered PLDs

advertisement

Architectures Centered Around Nonregistered PLDs Introduction Design of the One-to-three-Pulse Generator by using a PLA PAL ROM Design of a More Complex FSM Using a ROM as the PLD Prepared By AJIT SARAF Introduction Registered PLDs for total state machine design R-type (Registered-type) PALS V-type (Variable-type) PALs FPGA (Field Programmable Logic Array) Registered trademark Actel and Xilinx GALs (Generic Array Logic Devices) Registered trademark of Lattice Semiconductor, Hillsboro, OR 97124. EPLDs (Erasable Programmable Logic Devices) Registered trademark Altera and Xilinx PLSs (programmable logic sequencer) Registered trademark of Phillips, Sunnyvale, Signetics Co. Introduction (Non-Registered PLDs) Representing possible input and output conditioning circuits. Sometimes referred to as the Huffman model. The PLD represents a ROM, a PLA, or a basic I/O PAL and is used to generate both the NS and output forming logic. Model used for architectures centered around nonregistered PLD Introduction The memory can be any of the devices, namely discrete flip-flops of some type Shift register or Counter. If a shift register or counter is used, the highest priority is given to shifts or counts in assigning state codes so as to make the most efficient use of that particular memory device. For some FSMs, it may be advisable to use discrete flip-flops as the memory elements of choice - a designer's option. Introduction The input and output conditioning circuit elements are taken from Synchronizers Synchronizer / Stretchers Debouncing circuits Output holding (storage) registers for filtering. Design of the One- to Three-Pulse Generator by Using a PLA Description and operation of the one-to-three pulse generator (a) Block diagram (b) Operation table (c) Timing diagram showing one- and three-pulse generations. Sequential description of the one- to three-pulse generator (a) Flow chart (b) State diagram derived from the flowchart showing a suitable state code assignment. The Sum Rule (a) State diagram segment showing branching conditions relative to the jth state. (b) (b) Application of the sum rule to the jth state in the state diagram segment. P-term table suitable for programming a 7 x 9 x 4 or larger PLA PLA Structure Block diagram for an n-input/m-output PLA showing the programmable AND and OR array stages and the p product-term lines. Switch Debouncing Implementation for the one- to three-pulse generator showing the debouncing, synchronizing and initialization (Sanity) circuits. (10 Gates & 26 Inputs) Symbolic representation of the fusible bit position patterns for an 8X16X4 FPLA that is programmed to generate the NS and output forming logic required by the one-to three-pulse generator Implementation of the one- to three-pulse generator with a PLD such as an FPLA or basic I/O PAL Design of the One- to Three-Pulse Generator by Using a PAL Symbolic representation of the fusible bit position patterns for an 8 x 16 x 4 basic I/O PAL (Nonregistered) Design of the One- to Three-Pulse Generator by Using a ROM (a) State table showing an unconditional output P for states b, C, and d (b) Collapsed program table for a PROM implementation. PROM decoder and symbolic representation of the fusible bit patterns required 10 program the one to three-pulse generator Implementation of the one to three-pulse generator with a six-input. (our-output PROM showing the external logic required to generate pulses conditional on CK. Design of a More Complex FSM by using a ROM as the PLD Design of the NS and output logic for a fictitious FSM by using a ROM. (a) State diagram. (b) Collapsed ROM program table constructed directly from the state diagram in (a). EPROM decoder and symbolic representation of the fusible bit position patterns in the OR plane required to program the fictitious FSM Implementation of the fictitious FSM by using an 8-input/8-output EPROM.and two 4·bit storage registers.