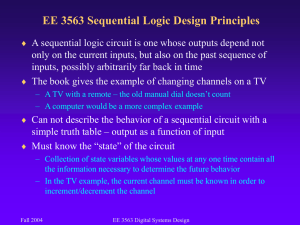

EE 3563 VHDL – Behavioral Modeling

advertisement

EE 3563 VHDL – Basic Language Elements Identifiers: – basic identifier: composed of a sequence of one or more characters • • • • upper case, lower case, digit, underscore first character must be a letter, last character must NOT be an underscore Two underscores cannot occur concurrently case insensitive: COUNT, count, Count, counT are all the same – extended identifier: sequence of characters written between two backslashes • • • Any printable characters can be used including %, $, *, etc. lower case and upper case are distinct examples: \2FOR$\, \countNow!\, \&#$(@#&!!!\ – Keywords can not be used as basic identifiers Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Basic Language Elements Data Objects – hold a value of a specified type – constant: holds a single value of a specified type and cannot be changed throughout the simulation – constant declaration: • constant RESULT: BIT:=1; constant FALL_TIME: TIME:=10ns – variable: holds a single value of a specified type but can be changed throughout the simulation • variable ABAR:BIT; variable STATUS:BIT_VECTOR(3 downto 0); – signal: holds a list of values including current value and a list of possible future values • • typically used to model wires and flip-flops signal DATA_BUS:BIT_VECTOR(0 to 31) – file: same as with any computer file, contains data Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Basic Language Elements Not all objects are created using the declarations Ports of an entity are automatically signal objects Generics of an entity are constant objects Formal parameters of functions and procedures are objects A “for” loop variable is an object for COUNT in 1 to 8 loop SUM:=SUM+COUNT; end loop; Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Basic Language Elements Data Types – specifies the constraints on values held by an object and the kind of value it is There are pre-defined types such as: – INTEGER (231 –1 to –231) – BOOLEAN (true, false) – BIT (0, 1) There can also be user-defined types and subtypes There are several categories of types including scalar, composite, access, and file types – We’ll focus on the scalar and composite A subtype is a type with a (possibly) added constraint – subtype SPC_INTEGER is INTEGER range 5 to 15; – subtype HALF_BIT is BIT range 0 to 0; – subtype NUMBER is INTEGER; -- no extra constraints here Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Basic Language Elements Scalar types – Enumeration – defines a type that has a set of user-defined values • • • type MY_VAL is (‘0’, ‘1’, ‘2’, ‘3’); type LOGIC is (AND, OR, NOT, XOR); Example declaration: variable AIN:LOGIC; – Integer – values fall within the specified integer range • • type REG_SIZE is range 0 to 31 subtype WORD is REG_SIZE range 0 to 15 – Floating Point – decimal types – Physical – represent measurement of some physical quantity like time, voltage, or current Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Basic Language Elements Composite Types – a collection of values – Array Types – collection of values all belonging to a single type • • • BIT_VECTOR and STRING are pre-defined one-dimensional array types type DATA_BYTE is array (0 to 7) of BIT; type MEMORY is array (0 to 127) of DATA_BYTE; – Record Types – collection of values that may belong to different types – Similar to a “struct” declaration in C type MODULE is record SUM:BIT_VECTOR(0 to 7); COUT:BIT; end record Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Basic Language Elements Operators – logical operators • and, or, nand, nor, xor, xnor, not – relational operators • <, >, =, <=, >=, /= -- /= means not equal to – shift operators • • logical shift left, logical shift right, arithmetic shift left, arithmetic shift right, rotate left, rotate right sll, srl, sla, sra, rol, ror – adding operators • +, -, & -- & is concatenation – multiplying operators • *, /, mod, rem – miscellaneous operators • Fall 2004 abs, ** -- ** is exponentiation EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling Entity declarations specify the entity name, the names of the interface ports, their mode (direction), and the type of ports There are several modes, we’ve seen two so far – – – – in – can only be read within entity model out – can only be written within entity model inout – can be read and written within entity model buffer – can be read and updated, it cannot have more than one source, can also be connected to another buffer • we will not need it – linkage – can be read and updated – used to interface with foreign language models • Fall 2004 we will not need it EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling The architecture body describes the internal view of the entity Concurrent statements describe internal composition of entity Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling The process statement contains sequential statements that describe the functionality of an entity in sequential terms The sensitivity list is a set of signals which will cause the process to execute in sequential order when an event occurs Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling The process then suspends and waits for another event to occur The process statement itself can execute concurrently with other concurrent statements, but internally, it executes sequentially The variable gets initialized to –1, then incremented to zero Any time an event occurs on A, this process is executed process(A) variable EVENTS_ON_A:INTEGER:=-1; begin EVENTS_ON_A:= EVENTS_ON_A+1; end process Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling Another example Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling A signal assignment statement can appear within or outside of a process – If outside a process, it is concurrent with the process statement – Within the process, it is sequential When executed, the expression on the right side of the assignment is evaluated at that time, not after any specified delay, then assigned to the signal after any specified delay Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling Wait Statement – a alternate way to suspend a process 3 forms of the wait statement Can be done in a single wait statement Examples Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling Another example using the wait statement, this time in a process without a sensitivity list Must have a sensitivity list or a wait statement, but NOT both Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling if statement – selects statements for execution based upon a condition Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling 2-input NOR gate done with if statements Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling case statement – selects one branch of execution from a list of many based upon expression Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling case statement Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling Null statement – it does nothing, sometimes may need to specify that nothing is to be done Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling loop statement – used to iterate through a set of sequential statements Several types of loops used in examples below Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling exit statement – used to jump out of a loop, cannot be used except inside a loop Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling next statement – can only be used inside a loop and begins execution back at the beginning of the loop Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling assertion statement – used for modeling constraints of an entity Fall 2004 EE 3563 Digital Systems Design EE 3563 VHDL – Behavioral Modeling report statement – can be used to generate a message Example: – report “This circuit does not work” Fall 2004 EE 3563 Digital Systems Design