vtran - Source III, Inc.

advertisement

Linking Simulation and ATPG Vectors

To ATE

With VTRAN and VCAP

Source III, Inc.

www.sourceiii.com

Background:

Logic Simulators and ATPG programs are used

extensively for chip design, validation and to create

high fault-coverage test vectors. Simulators generate

event-based vector data (VCD, EVCD, …) during

simulation. ATPG programs generate standard cyclebased, tester oriented vectors (WGL, STIL).

The Problem:

All of this vector data needs to be translated into

test programs for specific ATE so that the device can be

tested. There are 2 flows depending on whether vector

data is event-based or cycle-based.

1

VCD File

EVCD File

$timescale

1ps

$end

$scope module test_fed $end

$var wire

$var wire

$var wire

$var wire

$var wire

$var wire

.......

$upscope $end

1

1

1

4

1

1

!

"

#

$

%

&

$enddefinitions $end

#0

$dumpvars

0&

x%

bxxxx $

x#

x"

0!

........

$end

#4879

0"

#5000

1"

#5606

1#

b0011 $

#7060

1A

#10000

0+

0/

1*

........

p_mrdy_ $end

p_mintr_ $end

p_tclk $end

p_rxd [3:0] $end

p_rclk $end

p_crs $end

$timescale

1 ns

$end

$scope module

$var port

$var port

$var port

$var port

$var port

$var port

$var port

$var port

. . . . . .

$upscope $end

top $end

1 !

clki $end

1 "

clk2x $end

1 #

vcxo_ctrl $end

1 $

bclko $end

1 %

test $end

1 &

bopt $end

[3:0] A

devid $end

1 (

dsp_only $end

$enddefinitions $end

#0

$dumpports

pa 6 6 !

pX 6 6 "

pX 6 6 #

pX 6 6 $

pa 6 6 %

pb 6 6 &

pXXXX 6666 6666 A

pa 6 6 (

$end

#1

pT 0 0 "

pD 6 0 )

#5

pD 6 0 %

pU 0 6 &

pDDDD 5555 0000 A

pD 6 0 (

pH 0 0 0

pD 6 0 4

........

2

Flow 1: event-based (VCD/EVCD) data to ATE

Simulator

VCD

EVCD

Translator

ATE

Test Program

Event-based vector characteristics

Event entry when any signal transitions

No signal direction information for VCD

Timing is embedded in event data

Translation requirements:

Cyclizing Required (convert event-based to cycle-based)

State character translations

Identify/Specify Timing

Determine Signal Direction

Bidirectional Signal I/O data separation

Significant User input required

3

STIL File

STIL 1.0 ;

Signals {

out0 Out;

SDI0 In { ScanIn; }

SDO1 Out { ScanOut; }

BCK0 In;

. . . . . .

SignalGroups {

Group_1 = 'in0 + in1 + in2 + clk1 + clk2

+ SDI0 + SDI1 + ACK0 + BCK0';

. . . . .

Timing {

WaveformTable TS1 {

Period '90ns' ;

Waveforms {

out0 { HLXT { '0ns' X; '10ns' H/L/X/T; } }

out1 { HLXT { '0ns' X; '10ns' H/L/X/T; } }

BCK0 { 10 { '0ns' D; '60ns' U/D; '70ns' D; } }

. . . . .

ScanStructures {

ScanChain Chain1 {

ScanLength 4 ;

ScanIn SDI0 ;

ScanOut SDO0 ;

ScanCells ........ ;

. . . . .

MacroDefs {

"_scan_op_" {

Shift { V {

SDI0 = #; SDO0 = #;

SDO0 = #; SDO1 = #;

} }

. . . . . .

Pattern "_pattern_" {

W TS4;

V { // 0

Group_1 = NNN00NN00;

Group_3 = XXXXX;

}

C { // 100

Group_1 = NNN000011;

}

Macro "_scan_op_" {

SDI0 = 0010; SDO0 = XXHL;

SDI1 = 0001; SDO1 = XXLL;

}

V { // 500

Group_1 = 010001100;

}

W TS1;

V { // 600

Group_1 = 100000100;

}

Loop 12 {

W TS4

V { // 690

Group_1 = NNN00NN01;

Group_3 = XXXXX;

}

}

. . . . . . .

}

4

WGL File

waveform design

signal

"si" : input;

"se" : input;

"pi1" : input;

"pi2" : input;

"pi3" : input;

"ck_Epulse" : input;

"ck_Ppulse" : input;

"po" : output;

"so" : output;

end

timeplate "_default_WFT_" period 100ns

"si" := input [0ps:S];

"se" := input [0ps:S];

"ck_Ppulse" := input [0ps:Z, 50ns:D, 60ns:S, 80ns:D];

"ck_Epulse" := input [0ps:D, 20ns:S, 40ns:D, 50ns:Z];

"po" := output [0ps:X, 35ns:Q'window, 55ns:X];

"so" := output [0ps:X, 10ns:Q'edge];

. . . . . .

end

scancell

"Flop1"; "Flop2";

ccG ["Flop2", "Flop1" ];

end

scanstate

{ non_tester_ready_master_data }

{ scan_test }

ccU0 := ccG(XX);

ccL0 := ccG(01);

ccU1 := ccG(10);

ccL1 := ccG(01);

. . . . .

pattern group_ALL ("si", "se", "pi1", "pi2", "pi3",

"ck_Epulse", "ck_Ppulse", "po", "so")

{ test_setup }

vector("_default_WFT_") := [ X X X X X 0 0 X X ];

vector("_default_WFT_") := [ X X X X X 0 0 1 0 ];

vector("_default_WFT_") := [ 1 0 X X X 0 0 X 1 ];

repeat 25

vector("_default_WFT_") := [ X X X X X 0 0 X X ];

{ scan_test }

{ pattern 0 }

{ load_unload }

scan("_default_WFT_") := [ - 1 X X X 0 1 X - ],

output [cc:ccU0], input [cc:ccL0];

{ vector_capture }

vector("_other_WFT_") := [ 1 0 1 1 1 1 1 X X ];

. . . . .

end

end

scanchain

cc ["si", "Flop1", "Flop2", "so" ];

end

5

Flow 2: cycle-based (WGL/STIL) data to ATE

ATPG

WGL

STIL

Translator

ATE

Test Program

Cycle-based vector characteristics

All signal name and direction information included

All timing and waveform information included

High-level language constructs may be used

Possible scan data defined

Translation requirements:

Flatten or maintain scan

State character translations

Minimal User input required

6

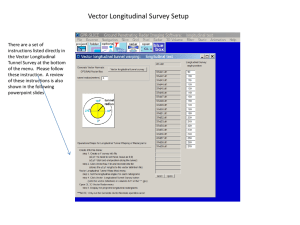

VTRAN

Vector data translation for Simulation & Test

7

VTRAN overview

• Bridging simulation & test formats

Simulation & ATPG-generated translations

Comprehensive vector processing options

• Large number of canned readers

STIL, WGL, VCD/EVCD, TDL_91, TSTL2, FSDB, FTDL

nanosim, VCL, … + User-Programmed Reader

• Numerous formatters for testers & EDA

STIL, WGL, Verigy, Credence, Teradyne, Advantest, IMS,

Verilog testbench, VHDL testbench, TSTL2, ….

• Nearly 20 years of success in hundreds of customer

applications

OEM’ed by Synopsys and Cadence for over 15 years

Used by Qualcomm, TI, Broadcom, Apple, Microsoft, Marvell,

TSMC, Xilinx, Nvidia, Micron, AMD, AMI, Cisco, …

8

VTRAN basic Flow

VTRAN

Tools

ATPG

Simulators

Vector

Formats

VCD/EVCD

WGL

STIL

…

OVF

TVF

Original

Vector File

Target

Vector File

Test Program

Verigy

Advantest

Teradyne . . .

Circuit Simulator

SPICE, HSPICE

Synopsys

TimeMill

PowerMill

NanoSim . . .

Processing

Command

File

Logic Simulation/

verification

VerilogTestbench

VHDL Testbanch

STIL

WGL

TSTL2 …

9

VCD/EVCD-to-ATE VTRAN FLOW

(errors)

VTRAN

Simulation

VCD/

EVCD

•Cyclize vectors

•State Trans

•Define Timing

•Signal Direction

•Masking

•other processing

Virtual

Test Program

Verification

VTRAN

ReadBack

ATE-to-Testbench

ATE Test

Program &

Timing

Verilog

Verification

Testbench

OK ?

ATE

Verification

Simulation

1. Simulation of final design generates VCD/EVCD file.

2. VTRAN performs cyclization, state mapping, makskng and other optional processing to generate ATE test program

3. In Virtual Test Program Verification, VTRAN ReadBack translates ATE test program to verification testbench.

4. Verification Simulation verifies test program – can be run with varying parameter corners.

5. If OK, then ATE test program is ready for tester.

6. If errors, then correlate to design or adjust VTRAN parameters.

10

VTRAN – cyclizing event vector data (vcd/evcd):

For single timeset data – use align_to_cycle

- User specifies cycle time

- User specifies signal sample points

- User specifies timing for output file

- VTRAN translates event- to cycle-based

For multiple timeset data use template_cyclization

- User specifies cycle time, sample points, and

timing for each timeset

- User specifies matching criteria for each timeset

- VTRAN matches timeset criteria to event data

to select the appropriate timesets and performs

event- to cycle-based translation

11

VTRAN Vector Processing

template_cyclization example:

TEMPLATE_CYCLIZATION

CYCLIZATION_SKEW = "0.5" ,

TERMINATE_ON_DEFAULTS = "20",

MATCH_REPORT = "designfile.rpt",

MATCH_TRACE_START = 1 ;

MATCH_TRACE_STOP = 8 ;

VIEW_OUTPUT = "designfile.view" ;

TIMESET SCAN_SHIFT

CYCLE 3.2;

PINTYPE NRZ * @ 0.5, 0.1;

PINTYPE -PRIMARY RZ cpref_clk @ 1.0, 2.0;

PINTYPE STB * @ 3.0, 3.1;

IDENTIFIER (scan_load=1)&(scan_enb=1) ;

ENDTIMESET;

TIMESET CAPTURE

CYCLE 6.4;

PINTYPE NRZ * @ .8, .1;

PINTYPE -PRIMARY RZ cpref_clk @ 2.0, 4.5;

PINTYPE -PRIMARY -ACTIVE_ONLY RO ubf_clk @ 1.5, 4.8;

PINTYPE STB * @ 6.1, 6.2;

IDENTIFIER (scan_load=0)&(scan_enb=1) ;

ENDTIMESET;

TIMESET RUN

CYCLE 4.0;

WEIGHT 1 ;

SAMPLE_POINT all_inputs @ 2.5;

PINTYPE NRZ * @ .4, .1;

PINTYPE -PRIMARY RZ cpref_clk @ 2.0, 3.0;

PINTYPE -PRIMARY RO ubf_clk @ 1.0, 3.2;

PINTYPE STB * @ 3.5, 3.6;

IDENTIFIER scan_enb = 0 ;

ENDTIMESET;

12

VTRAN Vector Processing

Add_Pin examples:

ADD_PIN

newpin

INPUT = 0;

ADD_PIN IOX BIDIRECT = ZX ;

ADD_PIN notclk input = 1 WHEN clk = 0 :

= 0 OTHERWISE ;

ADD_PIN ORpin input

=

=

=

=

1

1

1

0

WHEN pin1

WHEN pin2

WHEN pin3

OTHREWISE

= 1 :

= 1 :

= 1 :

;

ADD_PIN newclk INPUT = 1 ;

PINTYPE RZ newclk @ 25, 50 ; { creates constant clock }

13

VTRAN Vector Processing

mask_pins examples:

Very useful for debugging and cleaning-up test vector sets in

translations from VCD/EVCD event files. Remove spurrious glitches,

mask high-speed transitions, force initialization states.

MASK_PINS gpio1 @ 0, 700 ;

// cycle time = 100ns

gpio1 input state stream:

1100010111000000

gpio1 output state stream:

XXXXXXX111000000

MASK_PINS mask_character=1 gpio1 @ CONDITION err0=0 ;

err0 input state stream:

1111110000011111

gpio input state stream:

1110000000000000

gpio output state stream:

1110001111100000

MASK_PINS gpio1 @ TRANSITION 0->1, -4, +2 ;

gpio1 input state stream: 0000000011111111

gpio1 output state stream:

0000XXXXXX111111

MASK_PINS gpio1 @ SEQUENCE “00011111000”, “00XX1111XX0” ;

gpio1 input state stream:

1111000111110001

gpio1 output state stream:

111100XX1111XX01

14

VTRAN Vector Processing

mask_pins examples (continued):

MASK_PINS gpio1 @ CONTROL_TRANSITION ctrl1 0->1, -2, +3 ;

ctrl1 input state stream: 0000000011111111

gpio1 input state stream: 0011000011000111

gpio1 result state stream:

001100XXXXXX0011

MASK_PINS gpin1 @ TIMESET tset1 ;

MASK_PINS mask_character = “~pinA” pinX @ 1 ;

pinA input state stream: 0001110001110000

pinX

result state stream:

1110001110001111

MASK_PINS pinA @ CONDITION (err0=0)&(rel(-1)=0)&(err0(+1)=1) ;

err0 input state stream:

1111110000011111

rel input state stream:

1111111100000000

pinA input state stream: 0001110001110000

pinA

input

state stream:

0001110001X10000

15

VTRAN Vector Processing

Using Registers:

The REGISTER command supports the concept of a memory, or

register, element that can be used in a compound logic expression. The

basic idea is to provide a means whereby the occurance of an event

(logic condition or time) can be remembered and used as part of a logic

expression for other vtran statements.

REGISTER R1 init=0, set @ TIME 0 :

clear @ CONDITION (Reset=0)&(Run=1);

REGISTER Rmask init = 0, set @ CONDITION Pak=1 :

clear @ CONDITION (Pak=0)&(enb=1) ;

MASK_PINS all_outputs @ CONDITION Rmask=1 ;

16

VTRAN Vector Processing

bidirect_control examples:

For VCD translations, it is necessary to provide a mechanism by which

VTRAN can determine the direction of state data on bidirectional

signals. This is not necessary for EVCD, WGL or STIL files.

BIDIRECT_CONTROL gpio[12:0] = input WHEN dirctl = 0 ;

gpio bus is in input mode when dirctl is a logic 0

BIDIRECT_CONTROL gpio[6:0] = output WHEN (enb=1)&(dirctl=1) ;

gpio bus is in output mode when both enb and dirctl are logic 1

BIDIRECT_CONTROL gpio[8:5] = input WHEN dir = 0, DEFAULT_INPUT = N ;

gpio bus is in input mode when dir is logic 1, when in output

mode input track is N state.

17

Example VTRAN command script

OVF_BLOCK

BEGIN

{ Specify how to read input file }

orig_file = "sbc2.vcd";

SCRIPT_FORMAT verilog_vcd;

BIDIRECTS PAD_ICE_DATA[7:0];

INPUTS PAD_ICE_ADDR[15:0];

INPUTS PAD_ICE_EN_B;

BIDIRECTS PAD_PORTA;

BIDIRECTS PAD_PORTB[4:0];

OUTPUTS PAD_ICE_RST_O;

OUTPUTS PAD_ICE_IRQ_O;

INPUTS PAD_ICE_DATA[7:0];

INPUTS PAD_PORTB_ctl[4:0];

. . . .

PROC_BLOCK

BEGIN

{ Processing to be done on vectors }

cycle 100;

{10 MHz cycle}

BIDIRECT_CONTROL PAD_PORTA=input WHEN PAD_PORTA_ctl=1;

BIDIRECT_CONTROL PAD_ICE_DATA=input WHEN PAD_ICE_DATA_ctl=1;

BIDIRECT_CONTROL PAD_PORTB[4]=input WHEN PAD_PORTB_ctl[4]=1;

BIDIRECT_CONTROL PAD_PORTB[3]=input WHEN PAD_PORTB_ctl[3]=1;

. . . .

TVF_BLOCK

BEGIN

{ specify output file format }

tester_format HP93000 ,

-auto_group,

-DVC_OUTPUTS_FNZ,

XMODE = "ts1 3",

XMODE_MAP = "sbc2.map",

PIN_CONFIG_FILE = "sbc2.pin",

PINSCALE = "128",

TIME_STAMPS = "ON",

DVC_FILE = "sbc2.dvc"

REPEAT_THRESHOLD = "4"

;

TARGET_FILE = "sbc2.avc"; {output file }

END;

END;

ALIGN_TO_CYCLE 100, ALL_INPUTS @ 10, ALL_OUTPUTS @ 95 ,

PAD_XIN @ 40, PAD_XCIN @ 30;

PINTYPE

PINTYPE

PINTYPE

PINTYPE

NRZ * @ 10 ;

STB * @ 95 ;

RO PAD_XIN @ 30, 50;

SBC PAD_XCIN @ 20, 40;

STATE_TRANS outputs '0'->'L', '1'->'H', '-'->'X',

'x'->'X', 'z'->'X' 'Z'->'X';

STATE_TRANS pure_inputs 'X'->'0', 'x'->'0', 'z'->'Z';

STATE_TRANS bidir_inputs 'X'->'0', 'x'->'0', 'z'->'Z';

END;

18

VTRAN ReadBack modules:

This is an important feature for all tester interfaces,

particularly for translations from event-based vector files like

VCD and EVCD.

• Significant user input can result in errors

• Validates the VTRAN-generated test program

• Uses Virtual ATE testbench simulation

• Debug test program before silicon

• Saves costly ATE test time

VTRAN-generated

ATE test program

OK ?

Virtual

Test Program

Verification

VTRAN

ReadBack

ATE-to-Testbench

Verilog

Verification

Testbench

Verification

Simulation

19

STIL/WGL-to-ATE VTRAN FLOW

(errors)

VTRAN

ATPG

Synopsys

Cadence

Mentor

STIL/

WGL

•Scan data

•Multiple timesets

•ATE parameters

Virtual

Test Program

Verification

VTRAN

ReadBack

ATE-to-Testbench

ATE Test

Program &

Timing

Verilog

Verification

Testbench

OK ?

ATE

Verification

Simulation

1. ATPG run on final design generates STIL/WGL file.

2. VTRAN handles scan data and multiple timesets to generate ATE test program. Minimal user input required.

3. For Virtual Test Program Verification, VTRAN ReadBack translates ATE test program to verification testbench.

4. Verification Simulation verifies test program – can be run with varying parameter corners.

5. If OK, then ATE test program is ready for tester.

6. If errors, then correlate to design or ATPG for remedies.

20

VTRAN Support for Verigy 9300

Generates ASCII format file (for v2b utility)

Supports scan data (can also flatten scan)

Supports multiple timesets

Full support forRepeats and Loops from STIL/WGL files.

Also discovers Repeats and Loops in VCD/EVCD files for

compression.

• Repeat_Threshold feature

• Loop_Threshold feature

X-mode support

• Up to 8X

• Selectable by individual timeset

• Cumulative timing and pin-maps for multiple vector files

• Pinscale support

• Padding via default or padding file

• Create Signal Groups

21

VTRAN Support for Verigy 93000 (cont.)

File merging

• Can merge parallel vector files with overlapping or non-overlapping

signals

• Can merge sequential vector files

ReadBack module for test program validation via Verilog or

VHDL testbench.

Actively adding new support features.

22

VTRAN Support for Terdyne testers

Catalyst, J750, J971/973, UltraFLEX supported

Support for scan data and multiple timesets

Full support Repeats and Loops from STIL/WGL files. Also

discovers Repeats and Loops in VCD/EVCD files for

compression.

For J750 and uFLEX supports Basic Timing and Formulas

as well as standard tsets/esets files.

File merging

ReadBack modules for test program verification via Verilog

testbench.

uFLEX supports dual mode and x2/x4/x8/extended scan

types.

23

VTRAN Support for other testers

Advantest T66xx, T33xx and T2000

Credence (SWAV) and Saphire (STIL)

Q-Star IDDQ tester

HP94000

IMS

Trillium

LTX

Schlumberger ITS9000

ASIC formats: TDL_91, TSTL2, FTDL

Others under development per customer requests.

24

VTRAN Additional Processing Features

Merging Multiple Input Files:

Multiple input files can be merged using VTRAN with the MERGE_FILE

directive in the OVF_BLOCK :

OVF_BLOCK

BEGIN

TABULAR_FORMAT WGL –cycle ;

MERGE_FILE –concatenate

ORIG_FILE = “SET1.wgl”;

END_MERGE;

MERGE_FILE

ORIG_FILE = “SET2.wgl”;

END_MERGE;

MERGE_FILE

ORIG_FILE = “SET3.wgl”;

END_MERGE;

END;

PROC_BLOCK

BEGIN

. . .

25

VTRAN Additional Processing Features

IDDQ Control & Vector Insertion:

A general-purpose IDDQ vector insertion capability which provides for the

insertion of up to 3 control/data signals and any number of IDDQ vectors into

WGL or STIL files that have been generated with IDDQ markers.

IDDQ

IDDQfile = "iddqfname",

Keyword = "measureIDDQ"

Q_CLK = "1", { optional }

Q_MD = "1" { optional }

;

26

VTRAN comparison to competitors:

VTRAN/VCAP

Wavewizard

TSSI

User Interface

script

GUI

GUI

Learning Curve

1-2 days

1-2 weeks

2 weeks

Readers

> 20

3 or 4

3 or 4

Vector

Conditioning

Excellent

Fair

Good

Timing Analysis

Tool

Yes

Yes

Yes

Virtual Test

Included

Extra

Extra

Cost

Low

Medium

High

27

VTRAN SUMMARY

Comprehensive Translation Support - VTRAN™ supports over 30

vector and ATE formats including WGL, STIL, TDL_91, VCD/EVCD,

Teradyne, Verigy, Cadence, LTX, Advantest, IMS and many more.

Ease of Use - VTRAN™ has a typical learning time of 2-6 hours for

many translation applications.

Text/Srcipt Based - VTRAN™ is a batch compiler that is driven by a

command script created by the user. User maintains full control over the

process.

Over 25 Years in Business - VTRAN™ was introduced in 1990.

Thousands of successful translations done.

Large Customer Base - Texas Instruments, AMD, Apple, Microsoft,

Broadcom, Synopsys (OEM), Cadence (OEM), Infineon, Honeywell, Marvell,

NXP, Qualcomm,...

Excellent Documentation - Vtran™ User's Guide , INTERFACES

directory with numerous example translations, Extensive Application

Notes - all available online.

28

VTRAN SUMMARY (continued)

Powerful Editing Features - Adding/Deleting signals, Masking

signals (equation-based, sequence-based, time-based), name aliasing,....

Powerful Vector Processing Features - Repeat count control

(expansion, accumulation, max count), Loop control (expension,

accumulation, max count), File Merging, Insert Statements, Data Shifting,

Event Registers, Cyclization,....

Blazing Speed - VTRAN™ can translate GigaByte files in minutes.

Outstanding Technical Support - Source III is highly responsive to

all customer needs. New features are often added within days to meet

customer needs. We provide you with personlized technical support.

Low Cost!! - VTRAN™ is the lowest cost, full-feature, validated vector

translation program on the market.

29

VCAP

Vector Analysis Program

VCAP Extracts edge timing, waveform behavior and

statistical information from event-based files like VCD and

EVCD. It can serve as a front-end to VTRAN for cyclization.

Reports

VCD/

EVCD

VCAP

Timing file

for VTRAN

30

VCAP Analysis Features:

Handles wide variety of event-based vector formats

•VCD, EVCD

•Nanosim, Novas FSDB, Mentor Log files, tabular,

…

Checks for Max Delays

Analyses signal timing & behavior for single timeset

Checks for signal glitches

Illegal state checking

Checks for simultaneous transitions

Checks for output signal stability

Generate timing file for direct import into VTRAN

31

Thank You for your attention !

QUESTIONS ?

32