ECE 447 Fall 2009

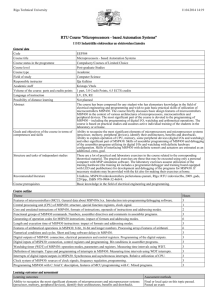

advertisement

ECE 447 Fall 2009 Lecture 3: TI MSP430 Introduction ECE447: General Microcontroller Characteristics • Integration of a CPU plus multiple peripherals on a single chip. • Low cost for high volume applications. • Lower clock frequencies when compared to devices like microprocessors and DSPs. – Typical range for microcontrollers: up to 100Mhz. • Low power consumption, allowing battery operation. • Data/Instruction word sizes from 4-bit to 32-bit • Limited memory, typically less than 1 Mbyte. • Various I/O pin-out configurations, from low to high (8 to 150 pins). ECE 447: Basic Computer System Parallel I/O Device Serial I/O Device Parallel Data CPU Data Bus Address Bus Control Bus Memory Program + Data Serial Data I/O Interface ECE 447: Microprocessor vs. Microcomputer Microprocessor – A processor unit typically with only basic I/O interface, off-chip memory. e.g.: Intel 8008, 8086, 80486, Pentium, Pentium 4, Core2Duo, PowerPC Single-chip Microcomputer – A processor unit with on-chip memory, I/O devices, and often other peripheral devices such as timers and A to D. e.g.: Intel 8048, Motorola 68HC11/12, TI MSP430 ECE 447: Microprocessor vs. Microcomputer Microprocessor – A processor unit typically with only basic I/O interface, off-chip memory. e.g.: Intel 8008, 8086, 80486, Pentium, Pentium 4, Core2Duo, PowerPC Single-chip Microcomputer – A processor unit with on-chip memory, I/O devices, and often other peripheral devices such as timers and A to D. e.g.: Intel 8048, Motorola 68HC11/12, TI MSP430 ECE 447: Processor Evolution Early microcroprocessors (8080, 6800, Z80) integration performance General-purpose microprocessors (e.g., Pentium, Athlon, Power PC) - high speed - long word size volume sold x1 Single-chip microcomputers (e.g., MC68HC11, MSP430) - small price - low power consumption - built-in memory - built-in I/O devices x 10 ECE 447: Microcontroller Applications • Cars – – – – – Engine fuel injection Transmission control Suspension and ride control Instrument display Braking system • Home Appliances – Washing machine – Microwave oven – Refrigerator • Sports Equipment – Exercise Machine – Heart Rate Monitor ECE 447: Microcontroller Applications • Consumer Electronics – – – – – Digital/Film cameras Remote Controls Televisions CD players Telephone • Computer Peripherals – Printers – Scanners – Disk drive controllers • Robots – The Brains ECE 447: Architecture vs. Organization vs. Realization Architecture: The instruction set and input/output capabilities available to the programmer Organization: The implementation of the architecture in block diagram form Realization: Actual implementation of an organization in a given technology, eg: CMOS High Level of Abstraction LOW ECE 447: Acronyms Used • CPU - Central Processing Unit := ALU (Arithmetic Logic Unit) + Control • RAM - Random Access Memory := Read/Write Memory • ROM - Read Only Memory (non-volatile) • EPROM – Erasable Programmable ROM • EEPROM - Electrically Erasable Programmable ROM • SPI - Serial Peripheral Interface (synchronous serial communication interface) • ADC - analog-to-digital converter • DAC – digital-to-analog converter • Port –Parallel I/O providing digital data lines (A,B,C,D,E) ECE447: MSP430 Microcontroller Characteristics • 16 bit RISC CPU: – Compact core design reduces power consumption and cost – 16-bit data bus – 27 core instructions and 7 addressing modes – Extensive vectored-interrupt capability • On-chip features: – – – – – – Programmable flash memory and SRAM 10/12/16-bit ADC, 12-bit dual DAC Timer capture and comparator systems Operational Amplifiers Watchdog and Supply Voltage Supervisor Communication systems (I2C, SPI) ECE 447: MSP430 Block Diagram ECE447: MSP430 Microcontroller Characteristics • Low Power Consumption: – – – – 0.1 A for RAM data retention 0.8 A for real-time clock mode operation 250 A/MIPS during active operation Less than 50 nA port leakage current • Low Voltage Operation – Vcc from 1.8V to 3.6V • Flexibility and Performance – – – – – – Startup less than 1 sec Instruction processing on bits, bytes, or words Up to 256 kBytes of Flash, up to 25 Mhz Clock Pin-outs from 14 pins up to 100 pins Embedded Debug/Emulation capability (JTAG) Wide Range of Peripherals ECE447: MSP430 Outside View Pin-Out (F2013) • Most pins have multiple features (pin multiplexing) • Pin limitations should be taken into account when designing a system so that pin conflicts are avoided • Larger devices allow more simultaneous I/O functions • Some functions are available on many pins (ie: TA0, TA1) • First task of a program is to configure the functions of each pin ECE447: MSP430 Inside View Functional Block Diagram (F2013) ECE447: MSP430 Inside View Functional Block Diagram (F2013) • This portion shows the CPU and its supporting hardware. • Basic Clock Subsystem • Emulation, JTAG, and Spy-Bi-Wire are used for communication with a host computer for downloading a program and debugging. ECE447: MSP430 Central Processing Unit • The MSP430 is a RISC (Reduced Instructions Set Computing) architecture: – Instructions set includes: • 27 physical instructions; • 24 emulated instructions. – Designed with static logic, which allows the CPU to be stopped and retain its state until it is restarted. – Arithmetic Logic Unit which performs computation. – Interconnect by a using a common memory address bus (MAB) and memory data bus (MDB) - Von Neumann architecture. – A set of 16 registers designated R0 - R15. ECE447: MSP430 Central Processing Unit Register Map A set of 16 registers designated R0 - R15. PC: Program Counter contains the address of the next instruction to be executed. SP: Stack Pointer to the address of the stack frame. The stack is primarily responsible for storing the return address of subroutine calls. SR: Status Register contains a set of flags – The C,Z,N, and V flags provide information from the last arithmetic operation. – The GIE flag enables the maskable interrupts. – The CPUOFF, OSCOFF, SCG0 and SCG1 flags control the operation of the MCU. Use of these flags allow operation in low power modes. CG1/CG2: Constant Generator provides the six most frequently used values so that they do not need to be fetched from memory. ECE447: MSP430 Inside View Functional Block Diagram (F2013) • The main blocks are linked by the memory address bus (MAB) and the memory data bus (MDB) • The device has 2kB of flash (1Kb is in the F2003) • The device has 128 bytes of RAM • The brownout protection comes into action when the supply voltage drop below an operational level. ECE447: MSP430 Memory • All memory is byte addressable (8-bits) and a byte is the smallest entity that can be transferred to and from memory. • The MSP430 memory address bus (MAB) is 16 bit wide so there are 216=65,536= 64K = 0x10000 addresses. • The MSP430X (like the F4618) architecture adds four bits to the address bus and CPU register to allow for 220 addresses. • The MSP430 memory data bus is 16 bits wide and can transfer either a word of 16 bits or a byte of 8 bits. – Bytes can be accessed at any address, but words must be accessed on a word aligned address (an even address value) • The MSP430 is a little-endian ordered machine. The low ordered byte is stored at the lower address. ECE 447: Area for Single Bit Cell Assumes 65 nm technology Flash human ROM EPROM EPROM FRAM EEPROM hair 20 0.8 1.1 1.1 1.1 1.6 RAM 3.3 ECE447: MSP430 Memory Map Memory Address End: 0FFFFh Start: 0FFE0h End: 0FFDFh Description Interrupt Vector Table Flash/ROM Start *: End *: Start: End: Start: End *: Start: End: Start: End: Start: End: Start: 0F800h 01100h 010FFh 0107Fh 01000h 0FFFh 0C00h 09FFh 027Fh 0200h 01FFh 0100h 00FFh 0010h 000Fh 0000h Access Word/Byte Word/Byte Information Memory (Flash devices only) Boot Memory (Flash devices only) Word/Byte RAM Word/Byte Word/Byte 16-bit Peripheral modules Word 8-bit Peripheral modules Byte Special Function Registers Byte • All memory including RAM, Flash, information memory, Special Function Registers (SFRs), and peripheral registers. • Starred (*) start and end addresses vary based on the particular MSP430 variant ECE447: MSP430 Inside View Functional Block Diagram (F2013) • Six Peripheral function blocks are shown. Many more exist in larger devices such as the F4618 – – – – – – 16 bit Sigma Delta ADC Port P1 8 bit I/O Port P2 2 bit I/O Watchdog timer Timer_A2 (2 Compare/Capture Registers) Universal Serial Interface ECE 447: I/O Device Architecture Control registers instructions ….. I/O device address1/name1 Status registers status of the device inputs (operands) ….. Data registers ….. outputs (results) ..... addressN/nameN ECE 447: Input/Output Register Types 1. Control registers - hold instructions that regulate the operation of internal I/O devices 2. Status registers - indicate the current status of internal I/O devices 3. Data registers - hold the input data sent to the I/O device and output data generated by this device 4. Data direction registers - control the direction (in or out) of the data flow to/from bidirectional data registers ECE 447: I/O Addressing Schemes Memory mapped I/O (Same Instructions) Separate I/O (Different Instructions) (e.g., Intel) (e.g., Motorola, TI) 0 0 max 0 I/O MAX Control lines: read/write MAX Control lines: read/write memory/io I/O ECE447: MSP430 Memory-Mapped Input and Output • Digital Input and Output are arranged on a set of pins and grouped in ports. • The MSP430 designates ports by number (P1, P2,…) • Pins can be configured as inputs or outputs • Internally, I/O ports appear as memory register (peripheral register) – Each port is associated with a byte. – Each bit in the byte corresponds to a specific I/O pin. – Each register can be read, written, and modified. ECE447: MSP430 Memory-Mapped Input and Output • Each port has several registers that are used to read, write, and configure it. • Port P1 has 8 registers, three are the most important: – Port P1 input, P1IN: Reading this returns the logical values on the P1 pins if they are configure for digital input and output. – Port P1 output, P1OUT: Writing to this register sends the value to be driven onto the port output pins if it is configured as a digital output. – Port P1 direction, P1DIR: A bit of 0 configures the corresponding pin as an input, which is the power-on default. Writing a 1 switches the pin to an output. ECE447: MSP430 Additional Resources • Resources for students working with the MSP430 – MSP430 device Data Sheet • The data sheet contains a wealth of information including device specific information. – MPS430 Family Users Guide • Provides a detailed description of all the functional modules within the family. • Register descriptions with bit details and reset values. – FET User’s Guide (Flash Emulation Tool) • A good FAQ on hardware, software development, and debugging. – Application Notes • TI has published over 100 ANs for the MSP430, from very general topics to very specific. – Code Examples • TI also has many code examples for the MPS430 available.