Lecture 8

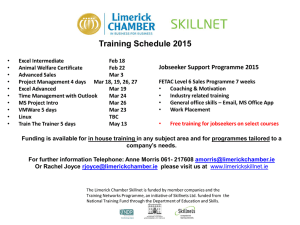

advertisement

Computing Machinery Chapter 8: The Very Simple Computer The Von-Neumann Architecture The concept of a stored program was part of the design of the Analytical Engine and well understood by Charles Babbage and Augusta Ada King more than 150 years ago. For some reason, this concept was temporarily lost or forgotten by the middle of the 20th century. Early electronic computers, such as the ENIAC, kept the logic and arithmetic instructions separate from the data. Some early computers had to be rewired in order to change their programs. The interpretation of a word in memory as either an instruction or data is determined by its location in memory rather than its pattern of ones and zeros. The content of memory has more than one possible interpretation. For example, the bit pattern, 01000000110010010000111111011010 can represent the integer 1,086,918,618 or an instruction to JUMP to another location (address) in memory, or it could represent an approximation for the numeric value of p. Designing the Very Simple Computer VSC Instruction operations code 3-bits limits the number of instructions to 23 = 8 address 5-bit limits the number of words to 25 = 32 8-bit instructions will all be direct addressing mode data type will be integer, twos'-complement operations will correspond to Post-Turing language with only 8 instructions, the VSC is the "Ultimate RISC" Computer The Very Simple Computer Program Counter (PC) Program Counter (PC) - The address of the next instruction that is to be executed is held in a register called the program counter (PC). The value in this register is passed to the memory unit as the address of the instruction to access. During the fetch portion of the fetch-execute cycle, the value in the PC is incremented. Memory Address Register (MAR) Memory Address Register (MAR) - The memory address register (MAR) of the VSC memory is also a 5-bit register. To read or write a word, we first place the memory address into the MAR and then activate the appropriate control lines (Read/Write, and Memory Enable) to perform the indicated I/O operation. Instruction Register (IR) Instruction Register (IR) - The VSC is a single-address instruction machine so the instruction register needs room to hold the operations code (op-code) of the instruction to be executed and the address on which the operation is performed. Since the VSC uses 8bit words, the instruction register (IR) supports a 5-bit address and a 3-bit op-code. Arithmetic Logic Unit (ALU) Latches ALU Latches (LAT1 and LAT2) - The arithmetic logic unit (ALU) accepts one or two input values. These values are held above the ALU in registers called Latch1 (LAT1) and Latch2 (LAT2). These registers have outputs that are always active since they are directly connected to the ALU and are never used to write to the bus. Accumulator (ACC) Accumulator (ACC) - The output of the ALU is the result of the execution of some arithmetic or logical operation. This value is held in the accumulator (ACC) until it is moved or otherwise managed by a subsequent instruction. Since the VSC is a singleaddress instruction CPU, the value in the ACC is transferred to one of the ALU latches during the fetch. The Instruction Set LDA addr - load the accumulator with the value from memory at address addr STA addr - store the value in the accumulator into memory at address addr. ADD addr - add value in memory at address addr to ACC and store in LAT1. CMP addr - take the 1's complement of the value in memory at address addr BNN addr - the branch-not-negative statement will set PC = addr if the value in the accumulator is not negative. SHL addr - shift value in memory at address addr one bit to the left. SHR addr - shift value in memory at address addr one bit to the right (arithmetic). HLT - this instruction terminates the fetch-execute cycle. Register Transfer Description 000 LDA X 001 STO X 010 ADD X ACC MEM[ X ] MEM[ X ] ACC ACC MEM[ X ] ACC 011 CMP X ACC MEM[ X ] 100 BNN X 101 SHL X if ( ACC 0 ) then PC X ACC MEM[ X ] * 2 110 SHR X ACC MEM[ X ] div 2 111 HLT X PC 111112 The Fetch/Execute Cycle MAR PC IR MEM[ MAR] get the address of the next instruction MAR IR 4 : 0 get the address in the current instruction PC PC 1 LAT 2 ACC increment to program counter LAT1 MEM[ MAR] EXEen move the data referred to by the instruction into LAT1 load the instruction register with the next instruction move the value in the ALU ACC into LAT2 execute the instruction Running the VSC MAR PC IR MEM[ MAR] MAR IR 4 : 0 PC PC 1 LAT 2 ACC LAT1 MEM[ MAR] EXEen Running the VSC MAR PC IR MEM[ MAR] MAR IR 4 : 0 PC PC 1 LAT 2 ACC LAT1 MEM[ MAR] EXEen Running the VSC MAR PC IR MEM[ MAR] MAR IR 4 : 0 PC PC 1 LAT 2 ACC LAT1 MEM[ MAR] EXEen Running the VSC MAR PC IR MEM[ MAR] MAR IR 4 : 0 PC PC 1 LAT 2 ACC LAT1 MEM[ MAR] EXEen Running the VSC MAR PC IR MEM[ MAR] MAR IR 4 : 0 PC PC 1 LAT 2 ACC LAT1 MEM[ MAR] EXEen Running the VSC MAR PC IR MEM[ MAR] MAR IR 4 : 0 PC PC 1 LAT 2 ACC LAT1 MEM[ MAR] EXEen Running the VSC MAR PC IR MEM[ MAR] MAR IR 4 : 0 PC PC 1 LAT 2 ACC LAT1 MEM[ MAR] EXEen Control Unit Executing OpCodes LDAen - load ACC enable - moves value in LAT1 into ACC STAen - store ACC enable - moves value in ACC into MEM[MAR] ADDen - ADD enable CMPen - CMP (1's complement) enable - takes the bitwise inverse of LAT1 BNNen - if(ACC7 = 0) then PC = IR<4:0> SHLen - shift-left enable SHRen - shift-right enable HLTen - halts the fetch-execute cycle by setting Control Unit IR Control Unit Fetch Operations PCre - PC read enable PCwe - PC write enable PCinc - PC increment MARwe - MAR write enable IRre - IR read enable IRwe - IR write enable LAT1we - LAT1 write enable LAT2we - LAT2 write enable ACCwe - ACC write enable (from ALU only) ACCre - ACC read enable (we read the ACC through the bus) VSC System Clock Fetch-Execute Cycle Timing Diagram Fetch-Execute Control Circuit VSC Instruction Decoder Circuit VSC Memory Unit Arithmetic Logic Unit Bitwise Complement and Shift Operations 74181 - A 4-Bit ALU VSC Input/Output Programming the VSC addr label instruction addr machine code . 0 LDA A 00000 00000100 1 ADD B 00001 01000101 2 STO C 00010 00100110 3 HLT 00011 11111111 4 A 24 00100 00011000 5 B 30 00101 00011110 6 C 0 00110 00000000 Loops in the VSC What is This? 00000 00010001 01011 00010100 00001 11000000 01100 10001111 00010 10100000 01101 00010001 00011 00110010 01110 11000000 00100 00010001 01111 00110001 00101 01100000 10000 11111111 00110 01010011 10001 00000111 00111 01010010 10010 00000000 01000 10001101 10011 00000001 01001 00001111 10100 00000000 01010 10100000