Solutions

advertisement

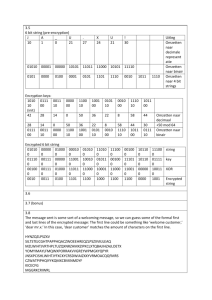

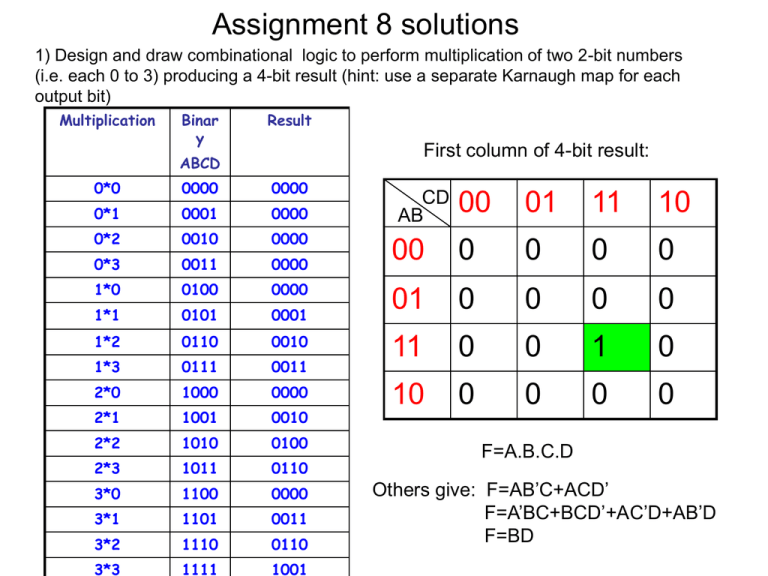

Assignment 8 solutions 1) Design and draw combinational logic to perform multiplication of two 2-bit numbers (i.e. each 0 to 3) producing a 4-bit result (hint: use a separate Karnaugh map for each output bit) Multiplication Binar y Result First column of 4-bit result: ABCD 0*0 0000 0000 0*1 0001 0000 0*2 0010 0000 0*3 0011 0000 1*0 0100 0000 1*1 0101 0001 1*2 0110 0010 1*3 0111 0011 2*0 1000 0000 2*1 1001 0010 2*2 1010 0100 2*3 1011 0110 3*0 1100 0000 3*1 1101 0011 3*2 1110 0110 3*3 1111 1001 CD AB 00 01 11 10 00 0 0 0 0 01 0 0 0 0 11 0 0 1 0 10 0 0 0 0 F=A.B.C.D Others give: F=AB’C+ACD’ F=A’BC+BCD’+AC’D+AB’D F=BD Assignment 8 solutions Assignment 9 solutions Design a 3-bit binary up-counter using D-FF to cycle over all odd numbers. To optimize the design, you are allowed to reset any even number states into any one of these odd numbers. At the end, show the complete state diagram with even numbered states, indicating which odd number they reset to. (Hint – your final design should contain 3 Dtype flipflops and a single combinational logic gate) Assignment 9 solutions Design a 3-bit binary up-counter using D-FF to cycle over all odd numbers. To optimize the design, you are allowed to reset any even number states into any one of these odd numbers. At the end, show the complete state diagram with even numbered states, indicating which odd number they reset to. (Hint – your final design should contain 3 Dtype flipflops and a single combinational logic gate) Assignment 9 solutions Design a 2 bit counter counting 0, 1, 2 using D-FF. There are two inputs: a data input which receives clock pulses, and a count direction input which when HIGH causes counting up and when LOW causes counting down. You may treat the excluded state 3 as you see fit to simply your design. At the end, indicate where the state 3 goes into Assignment 9 solutions Design a 2 bit counter counting 0, 1, 2 using D-FF. There are two inputs: a data input which receives clock pulses, and a count direction input which when HIGH causes counting up and when LOW causes counting down. You may treat the excluded state 3 as you see fit to simply your design. At the end, indicate where the state 3 goes into 0 1 0 0 1 Assignment 9 solutions Design a 2 bit counter counting 0, 1, 2 using D-FF. There are two inputs: a data input which receives clock pulses, and a count direction input which when HIGH causes counting up and when LOW causes counting down. You may treat the excluded state 3 as you see fit to simply your design. At the end, indicate where the state 3 goes into A Count B