Differential Amplifier

advertisement

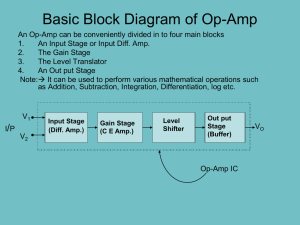

Operational Amplifier Introduction • Operation amplifier (op-amp) have high gain amplifier and able to amplify signal with frequency ranging from 0 to 1MHz. • An op-amp is named so because it was originally designed to perform mathematical operations like summation, subtraction, multiplication, differential and integration etc in analogue computer. • It has two input terminals, the inverting input ("-"), the non-inverting input ("+") and one output terminal. • A complete amplifier electronic circuit may contains transistor, diode, resistor, capacitor and others components and constructed on a single silicon chip. • The area is 5mm2 and thickness is less than 0.5mm, it is protected by lace plastic. Symbol and IC configuration of op-amp BASIC PRINCIPLES OF OP-AMP Inverting input Signal applied at negative input terminal will appear amplified but phase inverted at the output terminal. BASIC PRINCIPLES OF OP-AMP Non inverting input Signal applied at positive input terminal will appear amplified and in phase at the output terminal. Open loop voltage gain, Where, Vo = Output voltage Vid = voltage different on inverting input and non inverting input. Input Signal Modes • In single ended input mode one input is grounded and signal voltage is applied only to other input. • If the input is applied to the non-inverting terminal, the output signal will be in the same phase with the input signal. • In the single input mode connection, if the input is given to the non-inverting terminal, then the output will have a 1800 phase shift. In the double ended differential input mode, the difference input is amplified and in phase with the input signal. BLOCK DIAGRAM OF OP AMP An op-amp is a high quality amplifier. It contains three stages, which are connected in cascaded manner. Though designs vary between products and manufacturers, all op-amps have basically the same internal structure, which consists of three stages: • The first stage of an op-amp is a Differential amplifier (double ended) provides low noise amplification, high input impedance, usually a differential output. • The second stage is an intermediate gain stage. Voltage amplifier – provides high voltage gain, usually single-ended output. • The third stage is an Output amplifier stage – provides low output impedance, current limiting and short circuit protection circuitry. Block diagram of operational amplifier Configuration of Differential Amplifier Introduction There are four configurations of differential amplifier in the op-amp circuit. 1. Double ended input, balance output. 2. Double ended input, unbalance output. 3. Single ended input, balance output. 4. Single ended input, unbalance output. Each configuration is categories based on several factors: 1. Input signal quantity that use in circuit connection; – Input : 2 input signal is used, so it is called 2 input – Input: 1 input signal is used, so it is called single input. 2. How output voltage being measured. – If the voltage is measured between 2 collectors, the output will be balance. – If the voltage is measured at a collector and refer to ground, the output will not balance. Double ended input, balance output Double ended input, unbalance output. Single ended input, balance output Single ended input, unbalance output. DC analysis of differential amplifier Differential Amplifier Input bias current • The average of the currents flowing into both inputs. • It can calculated as follows: I BIAS I1 I 2 2 • The concept of input bias current is illustrated below: Input offset current • The difference of the two input currents when the output voltage is zero. I OS I 1 I 2 • The concept of input offset current is illustrated below: Input offset voltage • A small dc voltage appears at the output when no differential input voltage applied. • Its primary cause is a slight mismatch of the base-emitter voltages of the differential amplifier input stage of an op-amp. • Typical values of input offset voltage are in the range of 2 mV or less. In the ideal case, it is 0V. Common-Mode Gain (Acm) • Same voltage source is applied at both terminals • Output voltage is ideally zero due to differential voltage is zero • Practically, a small output signal can still be measured + V o V i ~ Common-mode rejection ratio (CMRR) • The common mode rejection ratio (CMRR) is the measure of the device's ability to reject common mode signals • It is the ratio of open loop gain, Aol to common-mode gain, Acm. Aol CMRR Acm • The CMRR is often expressed in decibels (dB) as Aol CMRR 20log Acm and with common devices having ratings between 60 dB to 120 dB. • The higher the CMRR is, the better the devices. Example 1. A certain op-amp has an open-loop voltage gain of 100,000 and a common-mode gain of 0.2. Determine the CMRR and express it in decibels. 2. Determine the CMRR and express it in dB for an op-amp with an open-loop voltage gain of 85,000 and a common-mode gain of 0.25. 3. An op-amp has a CMRR of 90dB. If its differential voltage gain is 30000, calculate its common-mode gain. INTERNAL CIRCUITRY OF OP-AMP: +Vcc Q4 Input 1 Q1 Q7 Q5 Q2 output Input 2 Q8 Q3 Push-pull amplifier Q6 -Vcc Differential amplifier Input stage Voltage amplifier Intermediate/Gain stage Push-pull amplifier Output level Internal circuitry of an Op-amp Internal block diagram of an Op-amp Input Stage: Differential Amplifier: - an op-amp is usually matched transistors configured as a dual-input Differential amplifier(DA) - output of this input stage taken from across the outputs (collector) of the paired transistors - this balanced output is fed into another dual-input DA in the intermediate stage (gain stage) Intermediate/Gain Stage: Voltage Amplifier - the output of this intermediate/gain stage is taken from just one of the transistors (single-ended output/unbalanced) - the DC level at the output of this stage is high with respect to ground, so a level-shifting circuit such as an emitter follower is used to shift it down closer to ground Output Stage : Push-pull amplifier - Act as buffer to connect 2nd level and output differential amplifier not affected by load - Consists of a push-pull amplifier: which increases the swing of the output voltage and enhances the load current capacity of the op-amp (prepare enough current to trigger load at the output terminal). Push-pull Amplifier Push-pull Amplifier • When the input signal is positive, the npn transistor has a positive voltage at the emitter compared with the 0 V on the far side of the load. Conventional current flows through the load to the 0 V line. The current is “pushed” through the load. • If the input is negative, the collector of the pnp transistor is negative compared to the zero point, and conventional current flows from the 0 V through the load to the pnp transistor. The current is "pulled" through the load. IDEAL CHARACTERISTICS OF OP-AMP a) Voltage gain = -the gain of the op-amp without positive or negative feedback. -ideal op-amp, Aol is taken to be infinite value. -Typical values of Aol range from 20,000 to 200,000 in real devices. b) Input impedance = -Input impedance is the ratio of input voltage to input current Avo = Vo Vid Vin Z in I in - When Zin is infinite, the input current Iin=0. - High-grade op-amps can have input impedance in the Tera Ω range. c) Output impedance = 0 - An ideal op-amp has infinite input impedance and zero output impedance. - when Iin is zero if Rin is equal to infinity. Model of an op-amp Vo AoVi RL Ro RL If the output resistance Ro is very small, there is no drop in output voltage due to the output resistance of an op-amp. d) Input offset voltage = 0 - input offset voltage of an op-amp is equal to the output for zero input voltage divided by the open-loop voltage gain of the amplifier. Vos = Vo Aol - output voltage of an op-amp should be zero when the value of an applied voltage at both the input terminals is zero. in practical op-amp, found that the output voltage does exist for zero input voltage. it cause by small imbalances within the op-amp. e) Offset current = 0 - caused by difference in bias currents are needed by both input transistors in the Op-Amp. - It happen due to unsuccessful matching between transistor β – input transistor 1 2 I OS I B1 I B 2 f) Bandwidth = - The bandwidth of an amplifier is the range of frequencies for which the amplifier gives "satisfactory performance". Comparison of Operational Amplifier Characteristic The Op-Amp Configurations Non-inverting amplifier Rf vin vo 1 R1 Inverting amplifier Rf vo R1 vin Differential amplifier Rf vo 1 R1 Rf R3 v2 v1 R1 R2 R3 Summing Amplifier v1 v2 v3 vo R f R1 R2 R3 Integrator Differentiator Comparator vo Ao v1 v2