slides - Fei Hu

advertisement

Channel Coding (II)

Cyclic Codes and Convolutional Codes

1

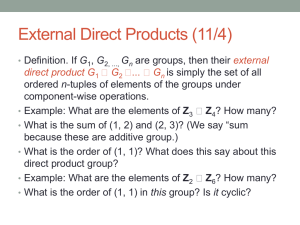

Topics today

Cyclic codes

– presenting codes: code polynomials

– systematic and non-systematic codes

– generating codes: generator polynomials

– encoding/decoding circuits realized by shift registers

Convolutional codes

– presenting codes

convolutional encoder

code trees and state diagram

generator sequences

ECED4504

2 of 20

Defining cyclic codes: code polynomial

An (n,k) linear code X is called a cyclic code when every cyclic shift of

a code X, as for instance X’, is also a code, e.g.

X ( x 0 x1

x n 2 x n 1 )

X ' ( x n 1 x 0

x n 3 x n 2 )

Each cyclic code has the associated code vector with the polynomial

X ( p ) x 0 x1 p

3 of 20

xn2 p

n2

x n 1 p

n 1

Note that the (n,k) code vector has the polynomial of degree of n-1 or

less. Mapping between code vector and code polynomial is one-to-one,

e.g. they specify the same code uniquely

Manipulation of the associated polynomial is done in a Galois field (for

instance GF(2)) having elements {0,1}, where operations are performed

mod-2

For each cyclic code, there exist only one generator polynomial whose

degree equals the number of check bits in the encoded word

ECED4504

The common factor of cyclic codes

GF(2) operations (XOR and AND):

Modulo-2 Addition

+

0

1

0

0

1

1

1

0

Modulo-2 Multiplication

*

0

1

0

0

0

1

0

1

Cyclic codes have a common factor pn+1. In order to see this we

consider summing two (unity shifted) cyclic code vectors:

X ( p ) x 0 x1 p

x n2 p

X '( p ) x n 1 x 0 p x1 p

2

p X ( p ) x 0 p x1 p

2

4 of 20

n2

x n 1 p

x n2 p

x n2 p

n 1

n 1

Unshifted

Right rotated

n 1

x n 1 p

n

Right shifted by multiplication

Question is how to make the cyclic code from the multiplied code?

Adding the last two equations together reveals the common factor:

p X ( p ) X '( p ) x n 1 p x n 1 x n 1 ( p 1)

n

ECED4504

n

5 of 20

Factoring cyclic code generator polynomial

Any factor of pn+1 (Note: decompose it into factors) with the degree

q=n-k generates an (n,k) cyclic code

Example: Consider the polynomial p7+1. This can be factored as

p 1 (1 p )(1 p p )(1 p p )

7

3

2

3

For instance the factors 1+p+p3 or 1+p2+p3, can be used to generate an

unique cyclic code. For a message polynomial 1+p2 (I.e. 110), the

following encoded word is generated:

(1 p )(1 p p ) 1 p p p

2

3

2

5

and the respective code vector (of degree n-1, n=7, in this case) is

(1 1 1 0 0 1 0)

ECED4504

6 of 20

Obtaining a cyclic code from another cyclic code

Therefore unity cyclic shift is obtained by (1) multiplication by p where

after (2) division by the common factor yields a cyclic code

1

X '( p ) p X ( p ) m od( p 1)

n

and by induction, any cyclic shift is obtained by

X ( p ) p X ( p ) m od( p 1)

(i)

Example:

right shift 101

(n=3)

(i)

101 X ( p ) 1 p

1 p

3

1

3

p p

1 p

3

3

1 p

2

pX ( p ) p p

pX ( p )

n

1 p

1

1 p

3

not a three-bit code,

divide by the common factor

110

Important point is that division by mod pn+1 and multiplication by the

generator polynomial is enabled by tapped shift register.

ECED4504

Using shift registers for multiplication

7 of 20

Figure shows a shift register to realize multiplication by 1+p2+p3

In practice, multiplication can be realized by two equivalent topologies:

ECED4504

8 of 20

Example: multiplication by using a shift register

adding dashed line would

enable division by 1+pn

determined by

the tapped connections

word to be

encoded

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

(1 p )(1 p p )

2

3

1 p p p p p

2

3

3

1 p p p 11101

2

ECED4504

4

4

Encoded word

0

0

0

1

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

1

out

0

0

0

1

1

1

0

1

0

9 of 20

Examples of cyclic code generator polynomials

The generator polynomial for a (n,k) cyclic code is defined by

G ( p ) 1 g1 p

g q 1 p

q 1

p ,q n k

q

and G(p) is a factor of pn+1. Any factor of pn+1 that has the degree q

may serve as the generator polynomial. We noticed that a code is

generated by the multiplication

X ( p ) M ( p )G ( p )

where M(p) is a block of k message bits. Hence this gives a criterion to

select the generator polynomial, e.g. it must be a factor of pn+1.

Only few of the possible generating polynomials yield high quality

codes (in terms of their minimum Hamming distance)

G ( p) p 0 p 1

3

Some cyclic codes:

ECED4504

10 of 20

Systematic cyclic codes

Define the length q=n-k check vector C and the length-k message

vector M by

M ( p) m m p

m p

k 1

0

C ( p ) c 0 c1 p

k 1

1

c q 1 p

q 1

Thus the systematic n:th degree codeword polynomial is

X( p) p

nk

( m 0 m1 p

c 0 c1 p

m k 1 p

c q 1 p

p M ( p) C( p)

q 1

k 1

)

message bits

q

Check bits determined by:

C ( p ) m od p

ECED4504

nk

M ( p) / G ( p)

check bits

11 of 20

Determining check-bits

Prove that the check-bits C ( p ) can be calculated from the message bits

M(p) by

C ( p ) m od p

p

p

nk

nk

nk

M ( p) / G ( p)

10 / 4 2 2 / 4

M ( p) / G ( p) Q ( p) C( p) / G ( p)

M ( p) / G ( p) C( p) / G ( p) Q ( p) C( p) / G ( p) C( p) / G ( p)

0

p

nk

M ( p ) C ( p ) G ( p )Q ( p )

message

check

must be a systematic code

based on its definition

(previous slide)

X ( p )

Example: (7,4) Cyclic code:

G ( p ) p p 1

3

M

(

p

)

p

p

p 74 M ( p ) p 6 p 4

3

ECED4504

2

p M ( p) / G ( p) p p 1 1

C( p)

Q( p)

nk

3

3

6

4

p M ( p) C( p) p ( p p) 1 p p 1

Q ( p ) G ( p ) ( p 3 p 2 1)( p 3 p 2 1) p 6 p 4 1

nk

3

2

12 of 20

Example: Encoding of systematic cyclic codes

ECED4504

Decoding cyclic codes

13 of 20

Every valid, received code word R(p) must be a multiple of G(p),

otherwise an error has occurred. (Assume that the probability for noise

to convert code words to other code words is very small.)

Therefore dividing the R(p)/G(p) and considering the remainder as a

syndrome can reveal if the error has happened and sometimes also to

reveal in which bit (depending on code strength)

The error syndrome of n-k-1 degree is therefore

This can be expressed also in terms of error E(p) and the

code word X(p)

S ( p ) m od R ( p ) / G ( p )

R ( p) X( p) E( p)

error syndrome

S(p) is:

S ( p ) m od X ( p ) E ( p ) / G ( p )

S ( p ) m od E ( p ) / G ( p )

ECED4504

Decoding cyclic codes: example

14 of 20

Using denotation of this example:

16.20 s ( x ) m od e ( x ) / g ( x )

ECED4504

Decoding cyclic codes (cont.)

15 of 20

Table 16.6

error

syndrome

error

s ( x ) m od r ( x ) / g ( x )

code

g (x)

ECED4504

msg

Part II. Convolutional coding

16 of 20

Block codes are memoryless

Convolution codes have memory that utilizes previous bits to encode or

decode following bits

Convolutional codes are specified by n, k and constraint length that is

the maximum number of information symbols upon which the symbol

may depend

Thus they are denoted by (n,k,L), where L is the code memory depth

Convolutional codes are commonly used in applications that require

relatively good performance with low implementation cost

Convolutional codes are encoded by circuits based on shift registers and

decoded by several methods as

Viterbi decoding that is a maximum likelihood method

Sequential decoding (performance depends on decoder

complexity)

Feedback decoding (simplified hardware, lower performance)

ECED4504

Example: convolutional encoder

17 of 20

x ' j m j 2 m j 1 m j

x '' j m j 2 m j

X out x '1 x ''1 x ' 2 x '' 2 x '3 x ''3 ...

(n,k,L) = (2,1,2) encoder

Convolutional encoder is a finite state machine processing information

bits in a serial manner

Thus the generated code word is a function of input and the state of the

machine at that time instant

In this (n,k,L)=(2,1,2) encoder, each message bit influences a span of

n(L+1)=6 successive output bits that is the code constraint length

Thus (n,k,L) convolutional code is produced that is a 2n(L-1) state finitestate machine

ECED4504

(3,2,1) Convolutional encoder

18 of 20

x ' j m j3 m j 2 m j

x '' j m j 3 m j 1 m j

x ''' j m j 2 m j

ECED4504

Here each message bit influences

a span of n(L+1)=3(1+1)=6

successive output bits

Representing convolutional code: code tree

x ' j m j 2 m j 1 m j

x '' j m j 2 m j

X out x '1 x ''1 x ' 2 x '' 2 x '3 x ''3 ...

Tells how one input bit

is transformed into two output bits

(initially register is all zero)

ECED4504

19 of 20

Representing convolutional codes compactly:

code trellis and state diagram

20 of 20

Input state ‘1’

indicated by dashed line

Shift register states

ECED4504