Chapter 12

advertisement

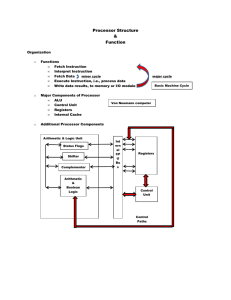

WILLIAM STALLINGS COMPUTER ORGANIZATION AND ARCHITECTURE 7TH EDITION Group 5 • Chris Bello • Arnold Colina • Edemio Navas • Rieni Gonzalez Chapter 12 CPU Structure and Function CPU Structure CPU must: Fetch instructions Interpret instructions Fetch data Process data Write data CPU With Systems Bus CPU Internal Structure The Memory Hierarchy • User-Visible Registers • Control and Status Registers User-Visible Registers - Availability • General Purpose Registers – can be assigned to a variety of functions by the programmer •Data Registers – holds data • Address Registers – may be considered as somewhat general purpose o Segment Pointers – segmented addressing machine o Index Registers – indexed addressing – auto-indexed o Stack Pointers - user-visible stack addressing • Condition Codes (flags) – results from operations Design Issues • General Purpose Registers or Specialized Registers? – Flexibility vs. Saving bits • How many registers? – Fewer registers result in more memory references • How big are these registers? – At least long enough to hold the largest address Control Registers – Control the operation • Program Counter (PC) –Has the address of an instruction to be fetched • Instruction Register (IR) – Has the instruction recently fetched • Memory Address Register (MAR) – Has the address location in memory • Memory Buffer Register (MBR) – Contains a word of data to be written to memory or the word most recently read o Data are exchanged with memory using the MAR and MBR o MAR connects directly to the address bus Status Registers – What’s your status? • Sign – contains the sign bit of the result of the last arithmetic operation • Zero – Set when the result is 0 • Carry – Set if an operation resulted in a carry or borrow • Equal – Set if a logical compare result is equality. • Overflow – Used to indicate arithmetic overflow • Interrupt enable/disable – Indicates if Interrupt is enabled or disabled • Supervisor – Indicates if the processor is in supervisor or user mode. o Some privileged instructions can be executed only in supervisor mode Practical Application Examples? • Motorola MC6800 [STR179] – Eight data registers – Nine address registers – 32 bit Program Counter – 16 bit Status Register Practical Application Examples? • Intel 8086 [MORS78] – Four 16-bit data registers that are addressed on a 16-bit basis – Four 16-bit pointer and index registers – Four 16-bit segment registers – Instruction Pointer and 1-bit status and control flags An instruction cycle includes the following sub cycles : •Fetch : Read the next instruction from memory into the processor. •Execute : Interpret the opcode and perform the indicated operation . •Interrupt : If interrupts are enabled and an interrupt has occurred , save the current process state and service the interrupt . •Indirect: after an interruption is fetched , it is examined to determine if any indirect addressing in involved .If so ,the required operand are fetched using indirect addressing . Data flow , fetch cycle The exact sequence during an instruction cycle depends on the design of the processor but in general Terms we can indicate what must happen . 1-During the fetch cycle an instruction is read from memory . 2-The PC contains the address of the next instruction to be fetched . 3-This address is move to the MAR and placed on the address bus . 4-Control Unit request a memory read and result is placed on the data bus and copied into MBR and moved to the IR. 5-Meanwhile the PC is incrementing by 1 , preparatory for the next fetch . 6-Once the fetch is over , the control unit examines the contents of the IR to determine if it contains an operand specifier using indirect addressing .If so ,an indirect cycle is performed . DATA FLOW , FETCH CYCLE CPU PC MAR MEMORY CONTROL UNIT MBR: memory buffer register MAR: memory add register IR: instruction register IR MBR PC: program counter ADD DATA CONTROL BUS BUS BUS Pipelining Fetch instruction Decode instruction Calculate operands (i.e. EAs) Fetch operands Execute instructions Write result Overlap these operations Two Stage Instruction Pipeline Timing Diagram for Instruction Pipeline Operation The Effect of a Conditional Branch on Instruction Pipeline Operation Six Stage Instruction Pipeline Alternative Pipeline Depiction Dealing with Branches Multiple Streams Prefetch Branch Target Loop buffer Branch prediction Delayed branching Multiple Streams Have two pipelines Prefetch each branch into a separate pipeline Use appropriate pipeline Leads to bus & register contention Multiple branches lead to further pipelines being needed Prefetch Branch Target Target of branch is prefetched in addition to instructions following branch Keep target until branch is executed Used by IBM 360/91 Loop Buffer Very fast memory Maintained by fetch stage of pipeline Check buffer before fetching from memory Very good for small loops or jumps c.f. cache Used by CRAY-1 Loop Buffer Diagram Branch Prediction (1) Predict never taken Assume that jump will not happen Always fetch next instruction 68020 & VAX 11/780 VAX will not prefetch after branch if a page fault would result (O/S v CPU design) Predict always taken Assume that jump will happen Always fetch target instruction Branch Prediction (2) Predict by Opcode Some instructions are more likely to result in a jump than thers Can get up to 75% success Taken/Not taken switch Based on previous history Good for loops Branch Prediction (3) Delayed Branch Do not take jump until you have to Rearrange instructions Branch Prediction Flowchart Branch Prediction State Diagram Dealing With Branches Questions: • • • • • • What are the general parts of the CPU? What general roles are performed by processor registers? What categories of data are commonly supported by user-visible registers? What is the function of condition codes? What is a program status word? Why is a two-stage instruction pipeline unlikely to cut the instruction cycle time in half, compared with the use of no pipeline? Questions: • • List and briefly explain various ways in which an instruction pipeline can deal with branch instructions How are history bits used for branch prediction Answers • • • • • • ALU, Registers, Control Unit, Internal Bus Data, Addresses, or Instructions To provide information about the data in question To inform the status of an operation Contains condition codes plus other status information The execution cycle may take longer than the fetch cycle, since it involves reading and storing operands. Answers Cont… • • Predict always/never taken, by opcode, taken/not taken switch, branch history table History bits contain the information on the previous branches taken which then are used to determine the branch to take.