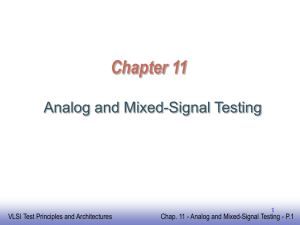

PPTX - IEEE-SA - Working Group

advertisement

IEEE 1149.4 Standard for a Mixed-Signal Test Bus Scope and Purpose BSDL Extension Defines a mixed-signal test bus architecture that provides access to analog and digital test points for: • Interconnect test • Parametric test • Internal test (2010 Revised Version) Top Level Architecture Digital Boundary Module (DBM) VH VL VG Core DIGITAL Analog Boundary Module (ABM) Circuit I/O PINS Boundary Scan Path TBIC (Test Bus Interface Circuit) AT2 TO/FROM CORE TAP Controller Instruction register and decoder CELL number TCK Analog Boundary Module (ABM) VH VL VG SH SL Analog function pin B2 9 8 7 6 AT1 AT2 Core Core disconnect SCAN PATH AB1 AB2 CELL number AT1 TBIC TBIC (IATB0) To TDO Application Example Extended interconnect test – measuring R value Ca Co D1a D2a D1b D2b 5 4 3 2 1 0 CHIP_A SCAN PATH CELL number A1 R V VG AB2 C D B1 B2 C D B1 B2 • Examples of safety critical applications include medical, security, transportation and process control. 13 12 11 10 9 8 7 SCAN PATH 6 attribute MST_ABM of comp_name : entity is -- port TBIC_partition_name C D B1 B2 “A1: IATB0 (13, 12, 11, 10), ” & “A2: IATB1 (9, 8, 7, 6) ” ; -- AB1a/AB2a from IATB0, AB1b/AB2b from IATB1 Further Information For further information, contact: IEEE 1149.4 Mixed-Signal Test Bus Working Group at http://grouper.ieee.org/groups/1149/4/index.html • Describing cells associated to each ABM • Second measurement CHIP_A CHIP_A CHIP_B AB2 R A5 VG 13 12 11 10 AT2 V C D B1 B2 AB1 AB2 Present Working Group members: CHIP_B A1 ABM AB1 IT • Mixed-signal devices can be used in a system which is tested regularly in the field such as in safety critical applications. ABM A5 AT2 A1 Potential Applications CHIP_B AB1 AT1 • Third party tools will be able to generate interconnect test patterns automatically using the provided BSDL from each device. • Mixed-signal devices for commercial applications. A1 AB1b AB2b A2 AB1a AB2a ABM VF1 SCAN PATH • ABM Statement • First measurement IT • BSDL extension allows mixed-signal chip vendors to provide description of their device’s test circuitry in the datasheet. (IATB1) attribute MST_TBIC of comp_name : entity is “ATI, AT2 : ” & -- pin1, pin2 “5, 4 ” & -- Ca, Co “(IATB0 (3, 2), ” & -- D1a, D1b (Base) “(IATB1 (1, 0) ” ; -- D2a, D2b (Partition) AT2 AT1 • Passive analog components between chips are able to be measured. SCAN PATH SB2 ABM Switch Control • Bridge and open faults detection test for both digital and analog nets can be performed simultaneously. AB1a AB2a AB1b AB2b SG Internal analog test bus From TDI B1 attribute BOUNDARY_REGISTER of comp_name : entity is ….. “9 (BC_1, *, control, 0), ” & -- C “8 (BC_7, A2, bidir, 0, 9, 0, Z), ” & -- D “7 (BC_1, *, internal, 0), ” & -- B1 “6 (BC_1, *, internal, 0), ” & -- B2 SD SB1 D • Provides interconnect test for high-density surfacemount assembled boards. • Parametric test and internal analog test can also be performed. • TBIC Statement DS + C R A5 ABM VTH AB1 AB2 ABM SCAN PATH Digital Test Access Port (TAP ) as in IEEE 1149.1 TDO Test Control Circuitry TMS • Description of boundary registers of an ABM Analog Test Access Port ATAP AT1 TDI Examples Internal Test Bus (AB1, AB2 ) VG Digital Test Access Port (TAP) as in IEEE 1149.1 • Describes 1149.4 test circuitry in a device • Compatible with 1149.1 BSDL • To support test pattern generation process A2 (ANALOG FUNC. PIN) ANALOG I/O PINS VH VL Benefits C D B1 B2 8 9 10 11 AB1 AB2 VF2 attribute MST_ABM of CHIP_A : entity is “A1 ( IATB0_A: 13, 12, 11, 10 ),” & -- C, D, B1, B2 • If Voltmeter impedance >> impedance of the switches • R = (VF1-VF2) / IT Attribute MST_ABM of CHIP_B : entity is “A5 ( IATB0_B: 8, 9, 10, 11 ),” & -- C, D, B1, B2 Bambang Suparjo Stephen Sunter Keith Lofstrom Heiko Ehrenberg Kenneth P Parker Zafar Quadri Adam Cron Adam Ley Marc Hunter