The 8086 Microprocessor and its Architecture

advertisement

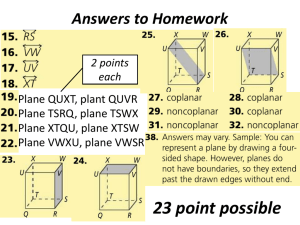

Khaled A. Al-Utaibi alutaibi@uoh.edu.sa The 8086 Registers The 8086 Memory Addressing The 8086 Memory Organization Data Registers: −The data group consists of the AX, BX, CX & DX registers. −Each one of these registers is 16-bit wide, but can be accessed as a byte or a word. Figure 1: Data Registers Pointer & Index Registers: −The registers in this group are all 16-bits wide. −They can not be accessed as a low or high byte. −They are used as memory pointers. −Register IP can not be accessed by the programmer and has only one function that is to point to the next instruction to be fetched by the CPU Figure 2: Pointer and index registers. Example 1: Referring to the next Fig 3, if SI=1000H, what is the contents of register AH after executing the instruction MOV AH, [SI]? Figure 3: Memory map of Example 1 Example 1: Referring to the next Fig 3, if SI=1000H, what is the contents of register AH after executing the instruction MOV AH, [SI]? −AH = 26H Figure 3: Memory map of Example 1 Status & Control Flags: −It is a 16-bit register −Six of the flags are status indicators reflecting the properties of the result of the last arithmetic or logical instruction. −The 8086 has several instructions that can be used to transfer program control based on the state of these flags, e.g. JNZ (jump on not zero), JZ (jump on zero). −Three of the flags can be set or reset directly by the programmer: TF (trap flag), IF (interrupt flag), and DF (direction flag). Figure 4: Status and control flags. Example 2: If the register AL=7FH and the instruction ADD AL, 1 is executed, what will be the content of the AL register? What will be the values of the status flags? Example 2: If the register AL=7FH and the instruction ADD AL, 1 is executed, what will be the content of the AL register? What will be the values of the status flags? Segment Registers: −These registers are used by the CPU to determine the memory segment addresses. −The function of these registers will be explained when discussing the memory addressing. Figure 5: Segment registers. Memory Space: −The 8086 processor has 20-bit address bus. −This allows the processor to address 220 or 1,048,576 different memory locations (1 MB). Memory Addressing: −the memory space is divided into segments and −the CPU is limited to accessing program instructions and data only from these segments. Figure 6: The 8086 memory space. Memory Segments & Segment Registers: −Within the 1MB memory space, the 8086 defines four memory blocks each of size 64K Code Segment: holds the program instruction codes Data Segment: stores data for the program Extra Segment: holds extra data (e.g. shared data). Stack Segment: used to store interrupt and subroutine return addresses. −The four segment registers (CS, DS, ES, and SS) are used to point to the beginning of each segment (i.e., location 0 or the base address) as shown in Fig 7. −The four segments need not be defined separately (i.e. they can overlap) as shown in Fig.8. Figure 7: The 8086 memory segments. Figure 8: Overlapping of the 8086 memory segments. Segments and Offsets : −A combination of a segment address and an offset address accesses a memory location. −All memory addresses must consist of a segment address plus an offset address. −The segment address, located within one of the segment registers, defines the beginning address of any 64K-byte memory segment. −The offset address selects any location within the 64K byte memory segment. −All memory segments have a length of 64K bytes. Figure 9: The 8086 memory-addressing, using a segment address plus an offset. Segments and Offsets : −Fig 9 shows how the segment plus offset addressing scheme selects a memory location. This illustration shows a memory segment that begins at location 10000H and ends at location 1FFFFH (64K bytes in length). It also shows how an offset address, sometimes called a displacement, of F000H selects location 1F000H in the memory system. Note that the offset or displacement is the distance above the start of the segment, as shown in Fig 9. The segment register contains 1000H, yet it addresses a starting segment at location 10000H. Segments and Offsets : −Note that Each segment registers is only 16 bits wide. −However, the CPU must generate a 20-bit memory address to access a location within the first 1M of memory. −It takes care of this by appending four 0’s (0H)to the low order bits of the segment register (multiplies the segment register contents by 16). −This forms a 20-bit memory address, allowing it to access the start of a segment. For example, when a segment register contains 1200H, it addresses a 64K-byte memory segment beginning at location 12000H. Likewise, if a segment register contains 1201H, it addresses a memory segment beginning at location 12010H. −Because of the internally appended 0H, memory segments can begin only at a 16-byte boundary (called a paragraph) in the memory system. Segments and Offsets : −Once the beginning address is known, the ending address is found by adding FFFFH (64K). −For example, if a segment register contains 3000H, the first address of the segment is 30000H, and the last address is or 3FFFFH. −The following table shows several examples of segment register contents and the starting and ending addresses of the memory segments selected by each segment address. Segments and Offsets : −The offset address, which is a part of the address, is added to the start of the segment to address a memory location within the memory segment. −For example, if the segment address is 1000H and the offset address is 2000H, the microprocessor addresses memory location 12000H. −The offset address is always added to the starting address of the segment to locate the data. −The segment and offset address is sometimes written as 1000:2000 for a segment address of 1000H with an offset of 2000H. Default Segment and Offset Registers: −The 8086 has a set of rules that apply to segments whenever memory is addressed. −These rules, define the segment register and offset register combination. −For example, the code segment register (CS) is always used with the instruction pointer (IP) to address the next instruction in a program. −The code segment register defines the start of the code segment and the instruction pointer locates the next instruction within the code segment. −This combination (CS:IP) locates the next instruction executed by the CPU. −For example, if CS=1400H and IP=1200H , the microprocessor fetches its next instruction from memory location or 15200H. Default Segment and Offset Registers: −Another default combinations is the stack. −Stack data are referenced through the stack segment register (SS) at the memory location addressed by either the stack pointer (SP) or the pointer (BP). −These combinations are referred to as SS:SP or SS:BP. −For example, SS=2000H and BP=3000H , the CPU addresses memory location 23000H for the stack segment memory location. −Other defaults of segment and offset combinations are shown in the following table. Logical and Physical Addresses: −Addresses within a segment can range from address 0 to address FFFFH. −This corresponds to the 64K length of the segment. −An address within a segment is called an offset, or logical, address. −For example, logical address 0005H in a code segment (CS= B3FFH) actually corresponds to the real address B3FF0H + 5 = B3FF5H. −This "real" address is called the physical address. −The physical address is 20 bits long and corresponds to the actual binary code output by the CPU on the address bus lines −The logical address is an offset from location 0 of a given segment. Example 3: Calculate the beginning and ending addresses for the data segment, assuming register DS=E000H. Example 3: Calculate the beginning and ending addresses for the data segment, assuming register DS=E000H. −Starting Address = E0000H −Ending Address = E0000 + 0FFFF = EFFFFH Example 4: Calculate the physical address corresponding to logical address D470H in the extra segment. Repeat for logical address 2D90H in the stack segment. Assume the segment Definitions ES= 52B9H and SS= 5D27H. Example 4: Calculate the physical address corresponding to logical address D470H in the extra segment. Repeat for logical address 2D90H in the stack segment. Assume the segment Definitions ES= 52B9H and SS= 5D27H. −Calculating the Physical Address of D470H −Physical Address = 52B90 + 0D470 = 60000H −Calculating the Physical Address of 2D90H −Physical Address = 5D270 + 2D90 = 60000H The memory is organized as two banks (Even Bank and Odd Bank) This allows the processor to access one word (two bytes) through its 16-bit data bus. Figure 9: The 8086 memory banks.